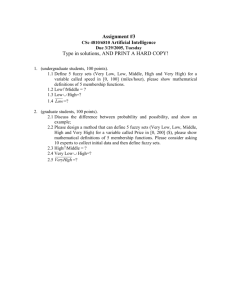

Single Chip Fuzzy Control System Based on Mixed-Signal FPGA Adviser Student

advertisement

Single Chip Fuzzy Control System

Based on Mixed-Signal FPGA

2009 International Conference on Intelligent Human-Machine Systems and Cybernetics

PPT製作:100%

Adviser:Kung, Ying-Shieh

Student:Chen , Yi-Chun

SN:M9920206

Nov. 24 2010

Outline

Abstract

I. INTRODUCTION

II. THE ARCHITECTURE OF FUZZY CONTROL SYSTEM

III. THE FPGA IMPLEMENT OF FUZZY CONTROLLER

IV. FUZZY CONTROL ARITHMETIC

2

A. Median Filtering

B. To Obtain e and ec

C. Fuzzy Discrete Quantization

D. Rule Base Table

V. CORE 8051 PROGRAM

VI. SOFTWARE TESTING

VII. CONCLUSION

REFERENCES

Abstract(1/2)

A fuzzy control system is analyzed and designed basing on a new hardware

platform mixed-signal FPGA.

Besides fuzzy control module, FPGA is also embedded with 8051, PWM,

ADC.

After analyzing the principle of fuzzy control module, it’s divided into

several modules according to the functional needs on the basis of this

division the logic structure of all modules can be obtained.

3

Abstract(2/2)

Then based on top – down design method, the fuzzy control module is

designed with Verilog HDL, and the whole design is optimized and

simulated successfully.

Finally, the implementation of the fuzzy control system on a specific

FPGA is given.

4

I. Introduction(1/2)

Classical control theory, which has been accumulated and improved

perfectly over a long period of time, is very effective to solve the control

problems in linear timeinvariant systems, but ineffective for nonlinear timevarying systems.

Fuzzy Control has strong robustness, and the impact isn’t obvious due to the

variational parameter of control plant, so it’s especially suitable for

nonlinear, timevarying, and time-delay systems.

5

I. Introduction(2/2)

As a high-performance, programmable platform, FPGA (Field

Programmable Gate Arrays) can shorten the circle of design and can be used

to implement the fuzzy controller situated between ASIC and MCU [1], [2],

[3].

By combining the fuzzy controller designed using Verilog HDL and the

8051 IP core, the entire fuzzy control system is a high-speed, highly reliable,

integrated, real-time system and, as a result, dramatically reducing overall

system cost and board space.

6

II. THE ARCHITECTURE OF FUZZY CONTROL

SYSTEM(1/4)

The proprietary FPGA architecture present new capabilities to integrate

a wide range of functionality into a single device, while at the same

time offering the flexibility of updates.

As a member of the world’s first mixed-signal FPGA family, AFS600

integrates mixed-signal analog, flash memory, and FPGA fabric in a

monolithic PSC (Programmable System Chip).

7

Core 8051 and fuzzy control module make the system not only have

the fuzzy control principle, but also have good human machine

interface [4].

II. THE ARCHITECTURE OF FUZZY CONTROL

SYSTEM(2/4)

Figure 1. The architecture of fuzzy control system

8

II. THE ARCHITECTURE OF FUZZY CONTROL

SYSTEM(3/4)

Core 8051 is made up of ALU, PWU, OCI, timer, UART, I/Os, RAM,

SFR, reset and clock control module. The flash memory of embedded

memories is used to be ROM of Core 8051.

The analog block consists of the analog quad I/O structure, RTC , ADC

and ACM. All of these elements are combined in the single analog

block macro, with which the user implements this functionality.

The analog quad is divided into four sections: voltage monitor block,

current monitor block, gate driver block, temperature monitor block.

9

II. THE ARCHITECTURE OF FUZZY CONTROL

SYSTEM(4/4)

At the heart of the AFS600 analog system is a programmable

successive approximation register ADC. The ADC can support 8-, 10-,

12-bit modes of operation.

The voltage monitor block is used in system, which is configured two

channels, 12-bit mode. The result is read by Core 8051 to display and

fuzzy controller for real-time processing.

10

THE FPGA IMPLEMENT OF FUZZY

CONTROLLER(1/8)

Fuzzy controller of the system is two-input and single output, which is

represented by the knowledge database, fuzzification, fuzzy reasoning

and defuzzification four parts.

Knowledge database provides subordination of the fuzzy quantity for

fuzzification module.

Therefore, after fuzzification module receives the precise amount of

external input, it can convert them into corresponding fuzzy quantity

and subordination.

11

THE FPGA IMPLEMENT OF FUZZY

CONTROLLER(2/8)

At the same time, Knowledge database not only provides control rules

for fuzzy reasoning module which performs reasoning process and

infers fuzzy quantity output from fuzzy quantity input, but also

provides subordination of the fuzzy quantity for defuzzification module.

Defuzzification will convert fuzzy quantity and subordination into

corresponding precise amount [5].

The fuzzy controller is designed using the top-down method, which is

divided to several modules that have right and clear relation and can be

easily to implement.

12

THE FPGA IMPLEMENT OF FUZZY

CONTROLLER(3/8)

Figure 2. The design flow of fuzzy controller

13

THE FPGA IMPLEMENT OF FUZZY

CONTROLLER(4/8)

Fuzzification module is to fuzzy error and change of error. The value

error is obtained by e=T(n)-R, where e is the error, R is the control

target, T(n) is the value at “n” time.

Fuzzy quantity subset of e in the system is Positive Small (PS), Zero

(ZO), Negative Small (NS), Negative Median (NM) and Negative Big

(NB).

The value change of error is obtained by ec=T(k)-T(k-1), where ec is

the change of error, T(n) is the value at “n” time.

Fuzzy quantity subset of ec is PB, PM, PS, Zero, NS, NM and NB.

14

THE FPGA IMPLEMENT OF FUZZY

CONTROLLER(5/8)

The universe scale of control value U is {0, 1, 2, 3, 4, 5, 6}, fuzzy

quantity subset PB, PM, PS, PL, ZO whose meaning to the next control

block is: PB-long time conduction, PM-middle time conduction, PSsmall time conduction, PL-little time conduction, ZO-hardly conduction.

TABLE I. FUZZY SUBSET QUANTIZATION TABLE OF U

15

THE FPGA IMPLEMENT OF FUZZY

CONTROLLER(6/8)

Fuzzy control role prescribes that when e is large, the control volume is

chosen to eliminate error quickly; while e is small, the control value

must be chosen to prevent overshooting. The fuzzy control block is

made up of two inputs e and ec, one output control value uf. Therefore,

the reasoning statement to control is: if e and ec then uf.

TABLE II. RULE BASE TABLE

16

THE FPGA IMPLEMENT OF FUZZY

CONTROLLER(7/8)

The fuzzy control algorithm uses look - up table method which makes

an element in the fuzzy universe take the place of fuzzy linguistics

value in the fuzzy control states.

The system uses fuzzy control algorithm with modifying factors that

can adjust control rule. The basic principle of algorithms uses output

expression to describe.

Control rules are simple and convenient, easy to handle. Rule is as

follows, note that α is modifying factor :

U: -<αe+(1-α)ec>, (0<α<1)

17

(1)

THE FPGA IMPLEMENT OF FUZZY

CONTROLLER(8/8)

From the control rule described, we can see that control behavior

depends on e and ec and can achieve a satisfactory control effect by

modifying α.

Sample values (e and ec) are quantized to input fuzzy linguistic

universe in the fuzzy controller, then the control precise value can be

obtained in look-up table based on the quantization.

The clear volume C(k) which is obtained by fuzzy reasoning module is

only a level set of fuzzy universe and cannot be executed to control the

object. It must be multiplied by a constant factor Ku.

Ku is defined theoretically as following: Ku=ΔUmax /n, where the

scale of control volume is [-ΔUmax, Umax], and fuzzy control universe

is U={-n,-n+1, …,n-1,n}.

18

IV. FUZZY CONTROL ARITHMETIC(1/4)

The fuzzy control arithmetic is implemented by Verilog HDL and

designed by the method of modularization, which is divided to four

modules, two macro blocks and one PLL block [7],[8].

Figure 3. The RTL schematic of fuzzy controller

19

IV. FUZZY CONTROL ARITHMETIC(2/4)

A. Median Filtering

As Fig.3 shows, the front interface module is sort module, where

sample values are processed to get better impact.

Median filtering is a kind of nonlinear signal processing technology,

which suppresses interference pulse and random noises, conquers the

accidental fluctuation.

B. To Obtain e and ec

The AD_OUT value after median filtering is effective value to be used

in fuzzy reasoning, which is next turned into memory “mem”. The

value e and ec is obtained by e=T(n)-R, ec=T(k)-T(k-1).

20

IV. FUZZY CONTROL ARITHMETIC(3/4)

C. Fuzzy Discrete Quantization

The input precise values must be processed by scale transformation into

corresponding universe bound.

A number of e and ec are quantized to several levels. The scale of e is [-

17.8, 1.2], its universe scale is {-6,-5,-4,-3,-2,-1,0,1}, and the scale of

ec is [-1.3, +1.3], its universe scale is {-6,-5,-4,-3,-2,-1,0,1,2,3,4,5,6}.

The ADC is configured 12-bits mode, so the scale of input value is 0-

4095.

21

IV. FUZZY CONTROL ARITHMETIC(4/4)

D. Rule Base Table

In the real time control system, the control precise value can be looked

up in Table 3 which shows the recommended rule base table for this

application [9].

According Ku’s definition above, this value must be computed

multiplying the vector by a constant factor.

22

TABLE III. FUZZY CONTROL’S LOOK UP TABLE

V. CORE 8051 PROGRAM(1/1)

As a part of the entire system,Core 8051 gathers the external data real-

time.

After modification, it controls other facilities of system, and forms an

excellent human-machine interface with LCD, KEY, LED, UART etc.

C is program language, and KeilC51 is compiler. It is a front, back

system, in which the routine task is a loop, the communication and

timer control use interrupt to act real-time.

23

VI. SOFTWARE TESTING(1/4)

All modules are simulated and tested, including fuzzy controller and

Core 8051. Fuzzy controller is implemented by Synthesis integrated in

Libero, and simulated by ModelSim.

The following waveforms are simulated by ModelSim, which can

validate every module is correct.

Simulation for fuzzy controller: The scatter module’s simulation is

accordant to design, which does discrete processing for input values.

24

VI. SOFTWARE TESTING(2/4)

Figure 4. The simulation waveform of scatter

Module Lut is a look up table according to input.

Figure 5. The simulation waveform of Lut

25

VI. SOFTWARE TESTING(3/4)

Simulation for PWM: To observe the output duty cycle, we set the

period to 66 us, because the actual period is too long to simulate.

The duty cycle is configured using duty cycle register.

Figure 6. The simulation waveform of PWM

26

VI. SOFTWARE TESTING(4/4)

The system human-machine interface and upper position machine

interface.

Figure 7. Human-machine and upper position machine interface

27

VII. CONCLUSION(1/2)

A fuzzy control model that combines multiply parameter formula fuzzy

control arithmetic and PWM control method was obtained.

Utilizing the mixed-signal characters of AFS600 FPGA, the multiple

analog acquisition and processing system based mixed-signal FPGA are

implemented, and the peripheral equipment and software are designed.

It can be used in other industrial environment after a little modified.

28

VII. CONCLUSION(2/2)

It is worthwhile to mention that the total elements occupy only 49%.

This system has simple structure and highly integrated advantages,

which can integrate all modules to one single chip and reduces the

expansion of peripheral for product update conveniently.

29

REFERENCES(1/3)

[1] Chia-Feng juang and Yu-Wei Tsao, “A Type-2 Self-Organizing

Neural Fuzzy System and Its FPGA Implementation”, IEEE

Transactions On Systems, Man, and Cybernetics, vol. 38-6, pp. 15371548, Dec. 2008.

[2] Ying-Shieh Kung, Chung-Chun Huang and Tzu-Yao Chuang,

“FPGA-Realization of a High-Performance Controller”, IEEE

International Conference On Industrial Technology, pp. 1-6, April 2008.

[3] Yongqiang Guo, Kangling Fang and Hongjun Zhou, “Design of

Fuzzy Feed-forward Decoupling System based on FPGA”, The 2008

International Conference on Embedded Software and Systems, vol. 2931, pp. 405-409, July 2008.

30

REFERENCES(2/3)

[4] Marek Polawski and Michal Bialko, “Implementation of Parallel

Fuzzy Logic Controller in FPGA Circuit for Guiding Electric

Wheelchair”, 2008 Conference on Human System Interactions, vol. 2527, pp. 405-408, May 2008.

[5] S. Iregui, D. Linares and M. Melgarejo, “Performance Evaluation of

Fuzzy Operators for FPGA Technology”, Annual Meeting of the North

American Fuzzy Information Processing Society, vol. 19-22, pp. 1-6,

May 2008.

[6] shuting Cai, xuesong Chen and qinruo Wang, “FPGA

Implementation of Generalized Fuzzy Operations”, Fifth International

Conference on Fuzzy Systems and Knowledge Discovery, vol. 3, pp.

560-564, Oct. 2008.

31

REFERENCES(3/3)

[7] FANG Jian-dong and GUO Zhen-xing, “The Design in System of

Parallel Reconfigurable Fuzzy Controller”, Microelectronics &

Computer, vol. 25, pp. 124-131, Sept. 2008.

[8] Liu Chunwu and Huang Zhiping, “Multiplexing-Architecture and

its FPGA Realization for Multi-Channel Signal Processing”, Journal of

Electronic Measurement and Instrument, vol. 22, pp. 72-75, Feb. 2008.

[9] Oscar Montiel, Yazmin Maldonado, Roberto Sepulveda and Oscar

Castillo, “Simple Tuned Fuzzy Controller Embedded into an FPGA”,

Annual Meeting of the North American Fuzzy Information Processing

Society, vol. 19-22, pp.1-6, May 2008.

32

Thanks for your attention!

33