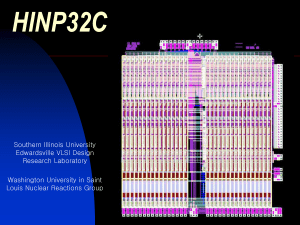

HINP32C

advertisement

HINP32C A Multi-Channel Integrated Circuit for Use With Silicon Strip Detectors in Experiments in Low and Intermediate Energy Nuclear Physics NEED FOR HINP32C SAMPLE APPLICATIONS Need for high density signal processing in low and intermediate energy nuclear physics community is widespread No commercial chip was found with: 1) large range (> 50 MeV) and dynamic range 2) Built in high quality timing circuitry 3) Self-triggering capability 4) Sparsification 5) Capability to utilize external preamplifiers Spectroscopy of low-lying particle unstable states by resonance decay correlation techniques. Direct and inelastic scattering of secondary unstable beams on p or d targets to study single-particle structure and excitation energy dependence of the nuclear level density. Particle-particle correlation experiments at intermediate energy designed to refine source-size characteristics. With external high gain and perhaps cooled preamplifiers, experiments requiring large arrays for detecting e-’s and ’s. GENERAL DESCRIPTION HINP32C (Heavy-Ion Nuclear Physics, 32 Channel) is a 32 channel integrated circuit (IC) for use in a series of experiments in low- and intermediateenergy nuclear physics. The IC is fabricated in the AMIS 0.5 m, N-well, double-poly, triple-metal, high-resistance C5N process through MOSIS. The die is 6 mm x 6 mm. Each channel consists of a charge-sensitive amplifier (CSA) with two gain modes: 100 MeV and 500 Mev full-scale. The CSA output (50 ns risetime) is split to feed energy and timing branches each of which produce sparsified pulse trains with synchronized addresses for off-chip digitization with a pipelined ADC. In addition to the two internally selectable gain ranges, the user can use external CSAs, as long as the decay time is close to 25 s. The energy leg consists of a third-order, tranconductance-C shaping filter with a fast return to baseline, < 20 s, and variable peaking time: 1 s - 2 s. This slow-shaper is followed by a continuous-time peak sampling circuit. Energy resolution is ~ 23 keV in the 100 MeV mode. The timing leg consists of a pseudo constant-fraction discriminator (CFD) composed of a leading edge and a zero-cross discriminator. The zero-crossing discriminator has its offsets dynamically nulled. A 6-bit DAC is used to correct offsets associated with the leading-edge circuit as well as to set CFD threshold levels. When the CFD fires, it starts a time-to-voltage conversion (TVC). The TVC circuit has two measurement ranges: 250ns and 1 s. The conversion is stopped by a common stop signal applied to all channels. The TVC circuit, as well as the peak sampling circuit, is automatically reset after a variable delay time (300 ns – 30 s) referenced to when the CFD fires, unless vetoed by the user. A fast logical ‘OR’ signal and an analog output proportional to the number of channels that were ‘hit’ are available for use. The logical ‘OR’ and the analog multiplicity output are also automatically reset unless vetoed by the user. Furthermore, the user can selectively read out pulse heights from channels for which the CFDs did not fire. A common channel provides biasing for the 32 processing channels and contains readout electronics. A 48-bit configuration register allows the user to selectively disable CFD outputs on a channel-by-channel basis, select test modes, select processing for either positive or negative CSA pulses, select CSA gain mode, TVC measurement range, and assign an 8-bit ID to the chip. The chip only responds when an externally applied chip address matches the ID stored in the chip's configuration register. SINGLE CHANNEL BLOCK DIAGRAM Resets TVC and Peak Sampler Reset Logic SELECT Pseudo CFD TVC Timing Peak Sampler Energy IN CSA VDD Mux Mux Slow Shaper SIMULATED PERFORMANCE NOISE 2.65 Output Voltage (V) Output (mV) 2600 10 1 0.1 2500 50 100 150 200 0.001 Capacitance(pF) 0.01 0.1 1 10 100 Mev Noise Slope: 3 e/pF Noise at 0pF: 2475e Resolution at 75pF: 21.6 KeV Linear range (Low gain mode): 100 Mev Linear range (High gain mode): 500 Mev REFERENCES Project WEB site: http://www.artsci.wustl.edu/~jmelson/nucinst.html 2.55 1000 20 25 Time (us) 30 49. 5 49. 0 48. 5 48. 0 47. 0 1. 00E+04 35 1. 00E+05 1. 00E+06 1. 00E+07 1. 00E+08 Input Electrons Response of the slow shaper with a negative going input pulse. Variation in propagation delay through the CFD is less than 500 ps over a range of 50dB. DESIGN TEAM George L. Engel, Muthukumar Sadasivam, Mythreyi Nethi Department of Electrical and Computer Engineering VLSI Design Research Laboratory Southern Illinois University Edwardsville Detailed electrical descriptions and updates: http://www.ee.siue.edu/~gengel/HINP.htm 50. 0 47. 5 2.45 0.001 0 2.6 2.5 0.01 2400 Propagation Delay (ns) 50. 5 100 2700 CFD Walk Plot 51. 0 2.7 1000 2800 WALK Response of Shaper Linearity of CSA and Shaper 2900 No.of Electrons SHAPER RESPONSE LINEARITY Noise Performance of CSA and Shaper Jon M. Elson, Lee G. Sobotka, Robert J. Charity Department of Chemistry Washington University, Saint Louis, MO 63130