(Part 2) (ppt) [no change]

advertisement

![(Part 2) (ppt) [no change]](http://s2.studylib.net/store/data/015416350_1-d0010556c1247088c051ef152463d0ca-768x994.png)

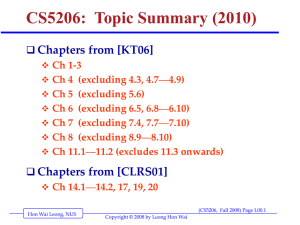

Hardware (Part B) Reading Materials: Chapter 5 of [SG]: The Computer System Optional: Chapter 2 of [Brookshear] OUTLINE 1. Organization of a Digital Computer 2. Major Components of a Computer System 3. von Neumann architecture: how it fits Together 4. The Future: non von Neumann architectures (UIT2201: Hardware(b)) Page 1 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Introduction Computer organization examines the computer as a collection of interacting “functional units” Functional units may be built out of the circuits already studied Higher level of abstraction assists in understanding by reducing complexity (UIT2201: Hardware(b)) Page 2 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.1 The Concept of Abstraction (UIT2201: Hardware(b)) Page 3 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Digital Computer: Logical Organization Organization of a Computer Input Devices CPU Output Devices Memory Unit (UIT2201: Hardware(b)) Page 4 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.2 Components of the Von Neumann Architecture (UIT2201: Hardware(b)) Page 5 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Components of a Computer System Functional units in Von Neumann architecture: Memory Input/Output Arithmetic/Logic unit Control unit Sequential execution of instructions One instruction at a time Fetched from memory to the control unit Concept of a stored program (UIT2201: Hardware(b)) Page 6 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Memory and Cache The functional unit that stores instructions (programs / “software”) and Data / information Primary Memory Types: ROM (Read Only Memory) Read only, permanent RAM (Random Access Memory) Read/Write, Volatile Cache memory keeps values currently in use (with faster memory) (UIT2201: Hardware(b)) Page 7 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.3 Structure of Random Access Memory (UIT2201: Hardware(b)) Page 8 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Memory and Cache (continued) RAM (Random Access Memory) Memory made of a large array of addressable “cells” (each of the same size) Maps “addresses” to memory locations (cells) Current standard cell size is 8 bits All memory cells accessed in equal time Memory address Unsigned binary number N long Address space is then 2N cells (UIT2201: Hardware(b)) Page 9 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Memory Unit -- Operations Data Transfers: Need Instructions: FETCH – instr to read content of a memory location (fetch some data from memory) STORE – instr to write a value to a memory location (store some data into memory) Need Special Registers: MAR – for the address of the memory location; MDR – for data to be written to / read from memory implemented via digital circuitry Using decoders to select individual cells Fetch / Store decoder (UIT2201: Hardware(b)) Page 10 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Registers (or Memory Registers) Memory register Examples: MAR, MDR Very fast memory location (1 cycle) Given a name, not an address Serves some special purpose Modern computers have dozens or hundreds of registers (UIT2201: Hardware(b)) Page 11 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Fetch Operation To “read” data/info from memory fetch (address) 1. Load the address of the desired memory cell into the MAR 2. Decode the address in the MAR 3. Copy content of that memory location into MDR (UIT2201: Hardware(b)) Page 12 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Store Operation To store information into memory Store (address, value) 1. Load the address into the MAR 2. Load the value into the MDR 3. Decode the address in the MAR 4. Store the contents of MDR into that memory location. (UIT2201: Hardware(b)) Page 13 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.7 Overall RAM Organization (UIT2201: Hardware(b)) Page 14 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Cache Memory Memory access is much slower than processing time Faster memory is too expensive to use for all memory cells Locality principle Once a value is used, it is likely to be used again Small size, fast memory just for values currently in use speeds computing time (UIT2201: Hardware(b)) Page 15 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Peripheral Devices (Overview) Other Devices that augments the CPU+memory I/O: Keyboard, mouse, monitor, printers, speakers, Storage: Cache, Disk drives, CD-drive, Zip-drive, tapes Communication: Network cards, modems, Devices communicate with CPU via controllers usually some kind of circuit board (eg: sound cards) Also, I/O devices vary greatly Can Dynamically added/removed devices Flexible Design needed to allow easy addition / removal / upgrading Design may be sub-optimal. Flexibility often more important than optimality. (UIT2201: Hardware(b)) Page 16 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Input/Output and Mass Storage Communication with outside world and external data storage Human interfaces: monitor, keyboard, mouse Archival storage: not dependent on constant power External devices vary tremendously from each other (UIT2201: Hardware(b)) Page 17 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Input/Output and Mass Storage… Volatile storage Information disappears when the power is turned off Example: RAM Nonvolatile storage Information does not disappear when the power is turned off Example: mass storage devices such as harddisks, thumb-drives, and tapes (UIT2201: Hardware(b)) Page 18 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Input/Output and Mass Storage… Mass storage devices Direct access storage device Hard drive, CD-ROM, DVD, etc. Uses its own addressing scheme to access data Sequential access storage device Tape drive, etc. Stores data sequentially Used for backup storage these days (UIT2201: Hardware(b)) Page 19 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Input/Output and Mass Storage… Direct access storage devices Data stored on a spinning disk Disk divided into concentric rings (sectors) Read/write head moves from one ring to another while disk spins Access time depends on: Time to move head to correct sector Time for sector to spin to data location (UIT2201: Hardware(b)) Page 20 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.8 Overall Organization of a Typical Disk (UIT2201: Hardware(b)) Page 21 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Input/Output and Mass Storage… I/O controller Intermediary between central processor and I/O devices Processor sends request and data, then goes on with its work I/O controller interrupts processor when request is complete (UIT2201: Hardware(b)) Page 22 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.9: Organization of an I/O Controller (UIT2201: Hardware(b)) Page 23 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Arithmetic/Logic Unit Actual computations are performed Primitive operation circuits Arithmetic (ADD, etc.) Comparison (CE, etc.) Logic (AND, etc.) Data inputs and results stored in registers Multiplexor selects desired output (UIT2201: Hardware(b)) Page 24 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.12 Using a Multiplexor Circuit to Select the Proper ALU Result (UIT2201: Hardware(b)) Page 25 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Arithmetic/Logic Unit (continued) ALU process Values for operations copied into ALU’s input register locations All circuits compute results for those inputs Multiplexor selects the one desired result from all values Result value copied to desired result register (UIT2201: Hardware(b)) Page 26 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Recap… Have seen how logic gates and flip-flops can be used to form combinational and sequential circuits; Any logic/arithmetic functions (operations) can be implemented this way; But, then the “functions” will be “hard-wired”. Need a “different computer” for each new job!! Instead, we want a general purpose computer computer runs a STORED program; “function” of the computer varies according to the different STORED program; the stored program is arbitrary general purpose computer; Basic Architecture: Von-Neumann Architecture (UIT2201: Hardware(b)) Page 27 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Control Unit Manages stored program execution Task Fetch from memory the next instruction to be executed Decode it: determine what is to be done Execute it: issue appropriate command to ALU, memory, and I/O controllers (UIT2201: Hardware(b)) Page 28 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Machine Language Instructions Can be decoded and executed by control unit Parts of instructions Operation code (op code) Unique unsigned-integer code assigned to each machine language operation Address field(s) Memory addresses of the values on which operation will work (UIT2201: Hardware(b)) Page 29 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.14 Typical Machine Language Instruction Format (UIT2201: Hardware(b)) Page 30 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Machine Language Instructions… Operations of machine language Data transfer Move values to and from memory and registers Arithmetic/logic Perform ALU operations that produce numeric values (UIT2201: Hardware(b)) Page 31 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Machine Language Instructions… Operations of machine language (continued) Compares Set bits of compare register to hold result Branches Jump to a new memory address to continue processing (UIT2201: Hardware(b)) Page 32 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Control Unit Registers And Circuits Parts of control unit Links to other subsystems Instruction decoder circuit Two special registers: Program Counter (PC) Stores the memory address of the next instruction to be executed Instruction Register (IR) Stores the code for the current instruction (UIT2201: Hardware(b)) Page 33 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.16 Organization of the Control Unit Registers and Circuits (UIT2201: Hardware(b)) Page 34 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Putting All the Pieces Together — the Von Neumann Architecture Subsystems connected by a bus Bus: wires that permit data transfer among them At this level, ignore the details of circuits that perform these tasks: Abstraction! Computer repeats fetch-decode-execute cycle indefinitely (UIT2201: Hardware(b)) Page 35 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.18 The Organization of a Von Neumann Computer (UIT2201: Hardware(b)) Page 36 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai CPU (Central Processing Unit) Components of a CPU: Control Unit: the “brain” of the CPU. decoding which operation is to be performed, and deciding the next operation to perform ALU (Arithmetic Logic Unit) consists of logic circuits for addition, multiplication, and all other operations Buses: wire connecting wires connecting up different parts of CPU, and the CPU to other components; Each component is built using logic circuits (UIT2201: Hardware(b)) Page 37 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai CPU Execution: Example: W = X + Y To add two numbers stored in X and Y and store the result in W CPU performs the following steps: 1. 2. 3. 4. 5. 6. 7. Place address of first number (X) in MAR; Issue a “FETCH” command to Memory Unit; Transfer content of MDR to Register R1; Place address of second number (Y) in MAR: Issue a “FETCH” command to Memory Unit; Transfer contents of MDR to Register R2; Issue a “ADD” command to ALU to perform addition of numbers in registers R1 & R2 and place result in register R3; 8. Transfer contents of R3 to MDR; 9. Place address of result (W) in MAR; 10. Issue a “STORE” instruction to Memory Unit; (UIT2201: Hardware(b)) Page 38 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Functioning of a CPU The steps above illustrates basic technique for CPU to execute simple instructions similar technique is used for all other instructions ANALOGY: “If we have buttons for the CPU functions, then a human can press the appropriate button to execute the above step” In real computers, the role of human is performed by the “Control Unit”, role of buttons by using control signals Control Unit is also responsible for decoding the instruction, figuring out the next instruction, etc (UIT2201: Hardware(b)) Page 39 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Future: Non-Von Neumann Architectures Physical limitations on speed of Von Neumann computers Non-Von Neumann architectures explored to bypass these limitations Parallel computing architectures can provide improvements: multiple operations occur at the same time (UIT2201: Hardware(b)) Page 40 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Future: Non-Von Neumann Architectures SIMD architecture Single instruction/Multiple data Multiple processors running in parallel All processors execute same operation at one time Each processor operates on its own data Suitable for “vector” operations (UIT2201: Hardware(b)) Page 41 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.21. A SIMD Parallel Processing System (UIT2201: Hardware(b)) Page 42 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai The Future: Non-Von Neumann Architectures MIMD architecture Multiple instruction/Multiple data Multiple processors running in parallel Each processor performs its own operations on its own data Processors communicate with each other (UIT2201: Hardware(b)) Page 43 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Figure 5.22. Model of MIMD Parallel Processing (UIT2201: Hardware(b)) Page 44 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Summary of Level 2 Focus on how to design and build computer systems Chapter 4 Binary codes Transistors Gates Circuits (UIT2201: Hardware(b)) Page 45 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Summary of Level 2 (continued) Chapter 5 Von Neumann architecture Shortcomings of the sequential model of computing Parallel computers (UIT2201: Hardware(b)) Page 46 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Summary Computer organization examines different subsystems of a computer: memory, input/output, arithmetic/logic unit, and control unit Machine language gives codes for each primitive instruction the computer can perform, and its arguments Von Neumann machine: sequential execution of stored programs Parallel computers improve speed by doing multiple tasks at one time (UIT2201: Hardware(b)) Page 47 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai If you are new to all these read the textbook carefully Do the practice problems and some exercises in the book Do the tutorials in the course. … The End … (UIT2201: Hardware(b)) Page 48 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Registers – clock speed of CPU RAM – 20 ns (20 x 10-9 s); Hard-disk (eg: 15,00rpm) – 2 ms (2 x 10-3s) Factor of about 10-5 difference Paper on desk – 1s Drawer in office – 10s Warehouse in Changi – 2 hrs (7200s) (UIT2201: Hardware(b)) Page 49 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai Memory Hierarchy Registers – 1 cycle L1-cache – a few cycles DRAM – hundreds of cycles Hard-disk – millions of cycles Analogy Calculator – immediate Paper on desk – few seconds Drawer in office – 1 minutes Warehouse in Changi – 2 hrs (7200s) (UIT2201: Hardware(b)) Page 50 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai References http://en.wikipedia.org/wiki/Access_time http://whatis.techtarget.com/definition/0,,sid9_gci523855,00. html#regram http://en.wikipedia.org/wiki/Processor_register http://en.wikipedia.org/wiki/Memory_hierarchy (UIT2201: Hardware(b)) Page 51 LeongHW, SoC, NUS Copyright © 2003-2008 Leong Hon Wai

![Concurrency (ppt) [new]](http://s2.studylib.net/store/data/015416347_1-961ba936e79840a20f1e3759fae84cf8-300x300.png)

![Alg-Animation (ppt) [updated]](http://s2.studylib.net/store/data/015416340_1-2753dde5340711cacfbfeacfa598b86c-300x300.png)