CMOS Front End ASICS for the SLHC Inner Tracker

advertisement

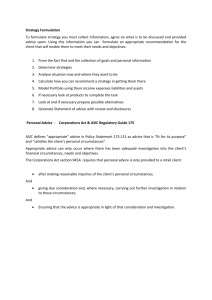

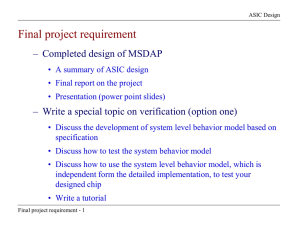

CMOS Front End ASICS for the SLHC Inner Tracker May 3, 2007 Mitch Newcomer SCT CMOS ASIC Design Team CERN MIC Francis Anghinolfi, Jan Kaplon University of Geneva Daniel Lamarra, Sebastien Pernecker AGH-Cracow Wladek Dabrowski, Krzysztof Swientek University of Pennsylvania Mitch Newcomer, Nandor Dressnandt Work organized/updated UPENN 5/3/07 through bi weekly phone conferences 2 ABCn/Module Readout Summary Recently discussions associated with the readout of Silicon Strip modules have led to the adoption of a two ASIC hierarchical approach: • • ABCn objectives will be scaled back. Improvements in data storage / buffering, new commands will be retained as well as housing an all CMOS front end readout. It will be backwards compatible or very similar to ABCD, intended primarily to implement module level improvements for SLHC. It will be developed on a fast track utilizing all institutional available resources, offloading more contentious issues of module to stave level readout and module level DCS to a second ASIC. A Module Controller chip will be developed over a longer time frame to address issues associated with module to stave communication and serial powering. Data transfer within a module is not finally optimized. This scheme provides an ASIC suitable module development while data transfer options are explored and finalized. UPENN 5/3/07 3 Two Specialized ASICs Module Controller DLL PLL To Stave Fiber Drive 40MhZ CMD Data Out M In Tok/Data ABCN No DLL/PLL ABCN No DLL/PLL ABCN No DLL/PLL #1 #2 #3 Out Tok/Data CMDout HF HFCMD Addresses issues at appropriate hierarchial level. - PLL/DLL clock/data phase - Logic Interface reduces logic loading: AC coupling/ Balanced enc. - Establish CLK/CMD phasing once per module. - Temp/Voltage Readback?? - Module Level power Regulator? 5/3/07 In Tok/Data Out Tok/Data S HFCLK Module Rcvr/Drvr ASIC UPENN Out Tok/Data S HFCLK (40-160MHz) Base CLK CMDin In Tok/Data (40-160MHz) In Tok/Data S HFCLK HFCMD …20E (40-160MHz) HFCLK HFCMD (40-160MHz) Simplified ABCn submission - No PLL/DLL - No Clock phase decoding -DRV/Rcvr’s DC coupled -Minimize # first time blocks in ABCn -Lower risk of missing submission schedule. -Lower complexity Higher yield -Can be made Backwards compatible 4 Two ASIC Hierarchical Approach ASIC #1 ABCn (fast track 0.25um Design) • Sensor signal processing (CMOS for now ) • L1 data sparsification / BC association • Sufficient Buffer depth for data syncronization • Backwards (ABCD) compatible • Reduced power over ABCD 2.5 1.9mW/ch • On board Regulators • Compatible with Serial powering • ?Constant power? UPENN 5/3/07 5 Two ASIC Hierarchical Approach ASIC #2 Module Controller MC** (Target first 130nm MPW Submission) • • • • • Stave to Module Data Communication Stave Level Data Alignment Fast Clock Generation 40MHz BC 40/80/160MHz DCS functionality : temp / voltage Serial Power ? This kind of organization has been mentioned previously: In Alex Grillo’s Oct ‘05 note this is the Com Con chip. Philippe Farthouat presented it as a possibility in an/the Inner tracker upgrade proposal UPENN 5/3/07 6 SCT Module Control ASIC To/From ABCn’s To/From Stave Controller Enabled BiPhase Mark decoding CMD in 40MHz CLK DLL CLK Phase Delay Module Data Out PLL CLK gen 40/80/160MHz Data Master Logic/Buffers HF CLK HF Data 1 … Enabled BiPhase Mark encoding (Clock embedded Data?) HF CMD Clk/CMD Sync HF Data n Monitor Functions ( t, V, PLL/DLLLock) UPENN 5/3/07 7 Penn SCT Module Readout Effort ABCn • I/O: Low level, Low Power Drivers/Rcvrs • Clock off (constant) Power Shunt • Power / Speed / Layout tradeoffs in clock rate and encoded clock schemes (130nm ABCn) • Extracted Simulation / Verification MC • • • • DLL / PLL data alignment** AC compatible Drivers / Rcvrs DCS interface temp/voltage meas. (similar to DTMROC) ASIC assy / Floor planning with Manhattan Routing **Significant effort on PLL/DLL (originally for ABCn) already in FY07 UPENN 5/3/07 8 6mW (200MHz) Point to Point Differential Current Rcvr INp INm UPENN 5/3/07 9 6mW Point to Point Clock Rcvr 0.25um CMOS worst case slow models 8pF ASIC to ASIC Stray, 1mA current drive 200MHz Clock input Rcvr (analog) Output First Inverter out UPENN 5/3/07 10 Near Term Timetable ABCn 0.25um – High Priority • July 07 -Blocks ready for floor planning • Submit ABCN Dec ‘07 MC ASIC 130nm • July – October ‘07 define / justify / finalize stave data interface. DCS interface • Submission Date (loose) Spring ‘08 ABCn 130nm TBD ( Dec ’08 ?) UPENN 5/3/07 11 Estimated Effort / Resources (CMOS ASIC design Effort) People EE Student Help - (EE) .9 FTE 1. FTE MC ASIC Chip assembly 130nm wrapper Manhattan Routing 2.5K (Tor Ekenberg) Travel 5K UPENN 5/3/07 12