researchitems.doc

advertisement

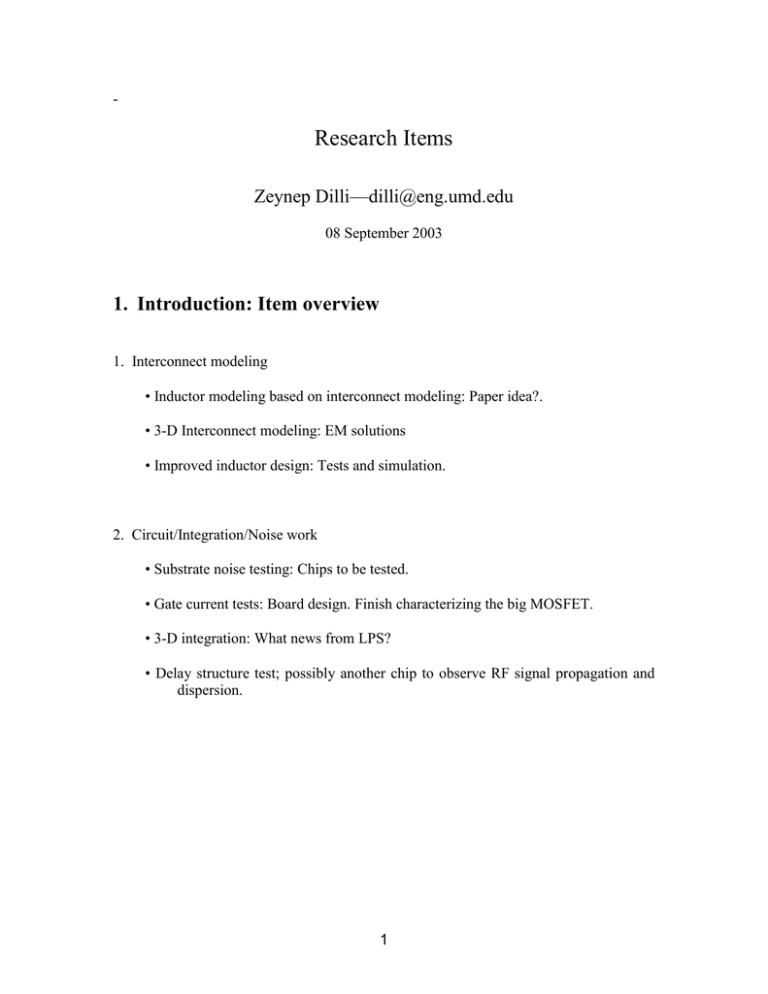

- Research Items Zeynep Dilli—dilli@eng.umd.edu 08 September 2003 1. Introduction: Item overview 1. Interconnect modeling • Inductor modeling based on interconnect modeling: Paper idea?. • 3-D Interconnect modeling: EM solutions • Improved inductor design: Tests and simulation. 2. Circuit/Integration/Noise work • Substrate noise testing: Chips to be tested. • Gate current tests: Board design. Finish characterizing the big MOSFET. • 3-D integration: What news from LPS? • Delay structure test; possibly another chip to observe RF signal propagation and dispersion. 1 2. Interconnect modeling On-chip interconnects have been modeled in transmission line terms using various methods that aim at going from field solutions to the TL parameters R, L, C and G. 1 Inductor modeling based on interconnect modeling In the literature, on-chip inductors have been modeled as a single circuit element which has an equivalent circuit as presented in Figure 1. Figure 1: Equivalent circuit model for on-chip inductors. The parameters on this model are obtained by various means. L and R, can be obtained from measured the s-parameters of the fabricated device. There has been very recent research (publications dated 2003) on modeling on-chip inductors using transmission line modeling techniques. Specifically, a group at Oregon State university has gone so far as to combine interconnect modeling techniques with partial element equivalent circuit modelling theory (which has been around since the 70s, initiated by Ruehli) to model inductance and resistance. What we do might be expanding on this work by including skin effect and capacitive modeling, as well as adding the capacitive and lossy-substrate effects. 2 2 3-D interconnect modeling For the 3-D integration project, we need to investigate the electromagnetic effects of longer vertical vias that go through the full substrate of the chips. We can use software that we developed as well as commercially available EM software for the first step of this analysis. At the moment, we have a frequency-domain 2-D solver for electric fields in a conductor near the presence of a ground plane. This solver needs to be extended into three dimensions, as well as supplied with more robust boundary conditions. Another step is to add the presence of a lossy dielectric substrate between the metal and the ground plane. There are some questions that specifically need to be addressed in the inquiry into this problem. One is the question of which effects would be negligible, to wit, is it necessary to give these vias the full transmission-line-effect treatment when they are only about 200 µ m long? Another question is what extra parasitics might arise from signals turning a vertical corner to go orthogonally to the on-chip signal plane. We need to look into whether such corners create more radiation or affect electromigration limits by reshaping current flow. The extra substrate-noise potential of signals boring through the full substrate thickness also need to be investigated. 3 Improved inductor design For on-chip inductors, research into improved designs has been a heated subject for the past ten years or so. Several main directions are the use of differently-shaped inductors (square vs. octagonal vs. other non-Manhattan geometries) and non-planar inductors (“2.5D” or “stacked” inductors, fully 3D inductors). As past work, we have two chips that Bai Yun designed and got fabricated: 1. The first chip features two pairs of inductors placed in close proximity to investigate the possible coupling between them. One pair has ground rings around its inductors; the other does not. This chip needs to be tested. 2. The second chip features inductors of different structures, including a pair of inductors with the same length, with one planar, and the other stacked. The stacked inductor, which we expect to yield higher inductance for the given path length, needs to be tested. Tejas Chitnis also worked on implementation of other 3-D inductor structures as I recall; however I am not aware how that attempt concluded. In combination with the physical 3-D integration work, it might be possible to investigate further inductor layouts. A more interesting tack to take would be to investigate how the doping pattern under the inductor affects inductance and Q. There is already some mention in literature of considering the effect of doping levels on parasitic substrate current (the “slow-mode, dielectric mode, metal mode” issue) as applied to inductors as well as to interconnects. However, as far as I am aware, there hasn’t been any investigation on patterning the substrate underneath the inductor to “fit” the inductor somehow and what effect that could have. 3 3. Circuit/Integration/Noise Investigations 1 Substrate noise testing Bai Yun designed and fabricated four versions of a chip that includes a digital part (ring oscillator) and an analog part (VCO). The idea is to run the digital part and observe changes to the operation of the analog part. The versions are unprotected, with different forms of protection, and with a different circuit architecture for the VCO. This last chip needs to be tested. 2 Gate current tests We have a 0.6 µ m technology chip that includes a large MOSFET (100 times the minimum size). We are going to design a PCB to mount this chip on, in preparation to characterizing this MOSFET. Although the gate oxide for this technology is somewhat thick: of the order of 10 nm, this might be a problem for observing gate current. Test circuits and structures need to be designed and fabricated for the results we are aiming to obtain. MOSIS has upcoming runs on the 22nd of September or 27th of October, and the latter should be enough time to formulate the next step. 3 3-D integration We have a 0.6 µ m technology chip that is designed to form several 3-D structures when two of its copies are stacked vertically: Ring oscillators, two-bit counters and buffers. We are currently awaiting the physical processes to mature for the complete assembly of the 3-D structures. 4 Delay structure test The same chip also includes structures to possibly observe signal propagation and delay down an on-chip interconnect. The chip needs to be mounted on a board for testing to be completed. However, it is possible that a dedicated chip that duplicates Bo Yang’s work with the RF signals on a coax cable might be a better way to proceed for such testing. 4