750syl08.doc

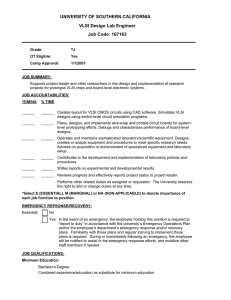

advertisement

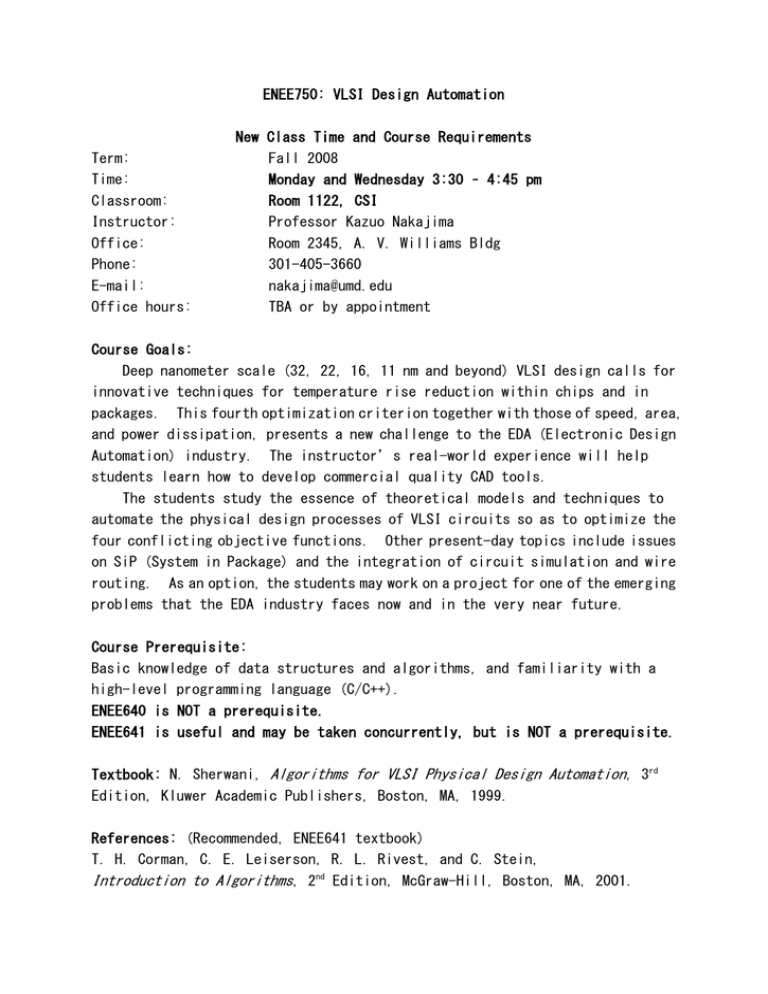

ENEE750: VLSI Design Automation Term: Time: Classroom: Instructor: Office: Phone: E-mail: Office hours: New Class Time and Course Requirements Fall 2008 Monday and Wednesday 3:30 – 4:45 pm Room 1122, CSI Professor Kazuo Nakajima Room 2345, A. V. Williams Bldg 301-405-3660 nakajima@umd.edu TBA or by appointment Course Goals: Deep nanometer scale (32, 22, 16, 11 nm and beyond) VLSI design calls for innovative techniques for temperature rise reduction within chips and in packages. This fourth optimization criterion together with those of speed, area, and power dissipation, presents a new challenge to the EDA (Electronic Design Automation) industry. The instructor’s real-world experience will help students learn how to develop commercial quality CAD tools. The students study the essence of theoretical models and techniques to automate the physical design processes of VLSI circuits so as to optimize the four conflicting objective functions. Other present-day topics include issues on SiP (System in Package) and the integration of circuit simulation and wire routing. As an option, the students may work on a project for one of the emerging problems that the EDA industry faces now and in the very near future. Course Prerequisite: Basic knowledge of data structures and algorithms, and familiarity with a high-level programming language (C/C++). ENEE640 is NOT a prerequisite. ENEE641 is useful and may be taken concurrently, but is NOT a prerequisite. Textbook: N. Sherwani, Algorithms for VLSI Physical Design Automation, 3rd Edition, Kluwer Academic Publishers, Boston, MA, 1999. References: (Recommended, ENEE641 textbook) T. H. Corman, C. E. Leiserson, R. L. Rivest, and C. Stein, Introduction to Algorithms, 2nd Edition, McGraw-Hill, Boston, MA, 2001. ENEE750, Fall 2008 (2) Topics: Overview of deep nanometer scale VLSI design Design and fabrication of VLSI devices Data structures and basic algorithms Partitioning Floorplanning Placement Global routing Detailed routing Thermal analysis for multi-layer interconnects Carbon nanotube interconnects Course Requirements: Homework/Class Participation 30% Midterm Exam 20% Project/Final Exam 50% Notes: The students either take the final exam or do a project. The project requirements may consist of studying/presenting/implementing the techniques described in research papers or of working on a new research problem, creating a model for the problem, developing techniques for the model, and implementing them. Written report of experimental findings and if time permits, oral presentation, are required. Active participation in class/presentation discussions is required. Attendance is considered as part of active participation.