3. Black Box Electronics.ppt

advertisement

Black Box Electronics

An Introduction to Applied Electronics for Physicists

3. Digital Electronics and more

University of Toronto

Quantum Optics Group

Alan Stummer, Research Lab Technologist

Digital Concerns

Physical

•

•

•

•

Supplies: Older +5V, newer +3.3V to +0.9V.

Volatile/Nonvolatile: Hold state and memory when power turns off? Volatile are

SRAM and DRAM. Nonvolatile are Flash (new: MRAM and FeRAM).

Edge Rate: Logic family (speed, power, voltage, termination).

Feature size: small is now 90nm, going to 65nm and 45nm.

Speed and Complexity

•

•

•

•

Microprocessors: μP, μC, DSP. Sequential execution only.

Programmable (FPGA): Sequential and/or parallel execution, Verilog or VHDL,

intensive simulations, volatile (“config chip”), high pin count (BGA/QFP).

Synchronous or Asynchronous: Clocked (preferred) or ripple (beware of race).

Edge or Level Sensitive: Most common is edge.

Protocol and Control

•

•

State Machines: Controlled order of operations.

Clock: Embedded, separate or async.

Communications

•

•

•

Baud and BPS: Physical signal rate (symbols) vs. payload data rate.

Single-ended or Differential: Fast, slow, susceptible to noise?

Overhead: Packet info, framing, scrambling (encoding), encryption.

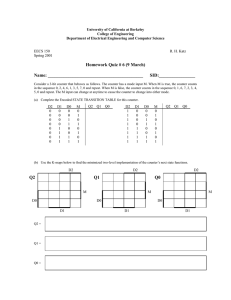

State Machines &

Timing Diagrams

Reset

State

Trigger

Q1

Q2

1

Wait for

trigger

1

2

Pulse

Q1

2

3

Wait for

trigger

3

4

Pulse

Q2

4

or

1

1

Logic Families

Family

Supply

Low (0)

High (1) ~Speed

Vdd/Vee Vcc

Vl

Vh

Tp

TTL

+5V

<+0.7V

>2.0V

5nS

LVTTL

+1.8V to +3.3V

<+0.7V

>2.0V

5nS

CMOS

~+3V to ~+15V

<20% Vdd

>80% Vdd

~10nS

[N]ECL

5.2V

~-1.5V

~-0.8V

250pS

[LV]PECL

+3.3V to +5.2V

Vdd–1.25V

- 0.2V

Vdd–1.25V

+ 0.2V

250pS

GaAs

& ASIC

Undefined

Undefined

Undefined

>10GHz

LVDS

(Differential

communications)

1.25±1 + 0.1V

1.25±1 - 0.1V

4GHz

CML

(Differential

communications)

2±1V + 0.1V

2±1V - 0.1V

15GHz

Microprocessors

μP, μC, DSP: Execute sequential instructions on data and I/Os.

• μP (microprocessor): CPU with external memory(s).

• μC (microcomputer): Small self-contained CPU and memories with I/Os.

• DSP: Specialized micro for signal processing.

Ultimately runs assembler (machine) language, transparent to C.

• CISC (Complex Instruction Set): Many assembler instructions, slow, versatile.

• RISC (Reduced Instruction Set): Less assembler instructions, fast, good.

Various programming languages

• Assembler (AKA machine): lowest level, hardest and slowest to code but can give

fastest execution, also used for special I/Os.

• C et al: Most common high level language, either proprietary or ANSI standard.

Dedicated or changeable function

• PC, MAC and SUN et al are most common “computers”.

• Embedded software is ubiquitious and often hidden: fuel injection to air bags,

oscilloscopes to optical power meter.

Loose Logic

•

AND, NAND, OR, NOR, XOR, XNOR, AND/OR, Buffer, Invert, Transceiver,

Counter, Divider, Shift Register, Selector/Mux, Decoder, Register, Flip-Flop,

Latch, Adder, Comparator, Parity Encoder/Decoder, Switch, etc.

•

Used for small or specialized tasks. Use programmable logic (FPGA) if

need greater functionality.

•

Available in most logic families.

•

Inputs can have Schmitt trigger (hysterisis).

•

Outputs can be totem pole or open drain/collector.

•

Outputs can have strobe (latch) and/or enable.

Programable

Logic (FPGA)

•

Large generic digital blocks with firmware determining function.

•

From 100’s to 100K’s of gates, may contain RAM, PLL, Layer 2 hardware.

•

Fast and large devices are volatile and use separate configuration device.

Cheaper and smaller devices have built-in non-volatile memory.

•

Most operations are synchronous to master clock(s), synchronous operations

can be executed concurrently or sequentially.

•

Programmed in C-like Verilog or VHDL languages, freeware.

•

Can embed processor, DSP, any protocol (IP cores).

•

Complex development environments, requires lots of development time.

•

Main vendors: Altera (used here in Physics), Lattice and Xilinx.

Verilog Example

Module’s name and I/Os

module Counters_Serializers (APD_A, APD_B, Clk, USBdata, USBinst);

input APD_A, APD_B;

//two APD inputs.

input Clk;

// a synchronizing laser input.

output [7:0] USBdata;

Local register //data bus out to USB device.

input [7:0] USBinst;

//command bus input from USB.

reg

[39:0] Counter [4:0];

//the internal array of counters.

assign APDs = {APD_B, APD_A};

//concatenate APDs.

Combinational logic (asynchronous)

/**************** MAIN “ALWAYS” EVENT FUNCTION *************************/

always @(posedge Clk) begin

On every +ve Clk edge, do this…

case (USBinst[1:0])

Non-blocking (do next line now too)

0: begin

//COUNT MODE.

Counter[APDs] <= Counter[APDs] + 1'b1;

State

Counter[4] <= Counter[4] + 1'b1;

end

Machine

Blocking (do this then next line)

1:

Counter[4] = 0;

//Reset main counter.

2:

USBdata = Counter[4][7:0];

//Read low byte of main counter.

3:

endcase

endmodule

USBdata = Counter[1][7:0];

//Read low byte first counter.

End of digital electronics.

Start of electronics potpourri.

TLAs

(Three Letter Acronyms)

• MOSFET: Metal Oxide Semiconductor [Shield] Field Effect Transistor

• CMOS: Complimentary MOSFET architecture

• RF: Radio Frequency

• FPGA: Field Programmable Gate Array (A.K.A. PLD, CPLD, PL)

• Verilog-HDL, VHDL: Hardware Definition Languages

• µC, µ P: Microcomputer, Microprocessor.

• EEPROM, E2: Electrically Erasable Programmable Read Only Memory

• Flash: Functionally similar to EEPROM.

• TTL: Transistor-Transistor Logic

• ECL, PECL: [Positive] Emitter Coupled Logic

• ASIC: Application Specific IC

• SMT: Surface Mount Technology

• DIP: Dual In-line Pins

Vendors & Suppliers

Vendors (Manufacturers), no particular order.

• Analog Devices www.analog.com (linear, DSP – good, cheap)

• Linear Technology www.linear-tech.com (linear – good, expensive)

• Maxim www.maxim-ic.com (linear, digital – diverse, good, serious supply issues)

• National Semiconductor www.national.com (linear, some digital - good)

• ON Semiconductors www.onsemi.com (Motorola linear - good)

• Texas Instruments www.ti.com (linear, digital – good, murky website)

• Altera www.altera.com (FPGAs)

Distributors, preferred first.

• Digikey www.digikey.ca (fast, cheap, reliable, <8PM = next AM)

• Electro-sonic www.e-sonic.com (okay speed, cheap, local, not always reliable)

• Active Surplus, Supreme Electronics (Queen St., College St., very questionable)

• Newark www.canada.newark.com (okay speed, customs issues)

• Allied www.aliedelec.com (okay speed, customs issues)

Up-to-date bookmark list on www.physics.utoronto.ca/~astummer

Spice

• Simulation of linear or hybrid circuits using numeric integration.

• Uses text models for components and ICs supplied by vendors.

• Various analysis:

• Dynamic (transient): similar to ‘scope.

• DC, Bias: biasing, static state.

• Frequency response: sweep a signal, observe effects.

• Temperature effects: test at different temperatures (not common).

• Monte Carlo: random component values inside given ranges.

Bypassing & Grounding

Bypassing

•

•

•

•

•

•

Bypass all ICs as close as possible to the IC with at least 0.1uF.

If more than several cm from supply, bypass ICs with 10uF “bulk” capacitor.

If IC has high frequency components (>10MHz), add 100-1000pF bypass.

Bypass all regulators with 0.1uF at input and output, or as per data sheet.

Be generous with bypass caps!

Fuse all supplies if can draw lots of current on failure.

Ground loop: anywhere ground connections can be followed in a circle.

•

•

•

Be aware of effects of ground currents on analog measurements: are you

measuring the signal or signal plus ground errors?

On PCBs or handwired boards, use a central ground point if possible – Star.

Avoid connecting a ‘scope if not needed – shields are grounded.

Sample Ground Loops

Tek

B&K

Ω The End Ω

Next:

4. Sample Circuits

5. Spice simulations

Then: More in depth on anything? Suggestions?