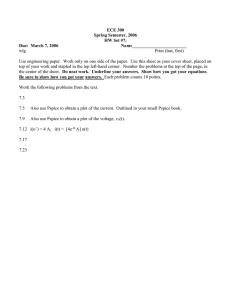

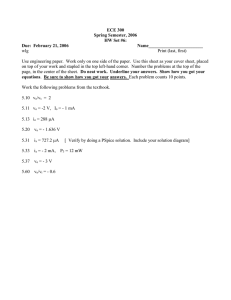

EE 42 Homework and Reading No. 6

advertisement

EE 42 Homework and Reading No. 6 Homework assigned Thursday 3 March 2005; due at 5:30 pm Thursday 10 March 2005 in the box labeled EE 42 in Room 240 Cory Hall. Note: your graded homeworks will be returned in your discussion section; your GSI will keep your homework until you pick it up to maintain privacy. Reading: Howe and Sodini (Copy Central Reader) Secs. 2.1 through 2.4.1 A. Problems in Howe and Sodini (the Copy Central Reader) [10 points each] 1. E2.1 (doped silicon electron and hole concentrations) 2. E2.3 (adding a different dopant to an already doped wafer) Note: this process is called “compensation”. It is done when you are building a transistor or diode and you want to have, say, a p-type region in the middle of an n-type region. 3. E2.5 (compensation again) 4. E2.7 (points out a problem when integrated circuit parts get very small) Note: VLSI stands for very large scale integration (i.e., hundreds of thousands of small transistors and other components in an IC). 5. E2.9 (charge carrier motion in silicon) B. Problems to be done with Orcad/Pspice. (Follow the instructions at http://inst.eecs.berkeley.edu/~ee42/sp05/pdf/hw-pspice.pdf.) 1. Attach a printout of the PSpice output file from a bias point simulation of P2.47 from Hambley. 2. Attach a printout of a plot of vc(t) from t = 0 to t = 1s for a transient simulation of P4.19 from Hambley.