Nasty Realities – Lab6 EECS 150 Spring 2001

advertisement

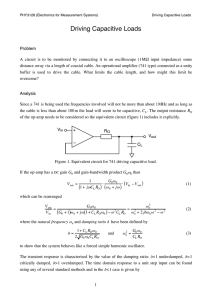

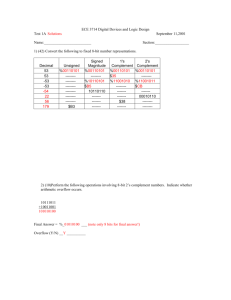

Nasty Realities EECS 150 – Lab6 Spring 2001 By Steve Fang Topics • Capacitive loading vs. Propagation delay • Reflection vs. Termination • Capacitive coupling Ideal vs. Reality Ideal Reality Components (1) • Breadboard • Connected underneath with metal contacts • Know how to make parallel resistors Figure 1a Breadboard connections Components (2) • Ribbon Cable with 16-pin Dip connector Figure 1b Ribbon cable DIP plug Components (3) • Resistors and Capacitors • Lab handout has some examples of how to identify a resistor and a capacitor • Example: red-black-brown = 200 ohm (red=2, black=0, brown=1) Components (4) • 74F04PC hex inverter chip • It has 6 inverters in it • Don’t forget to ground pin 7 and connect pin 14 to Vdd Figure 2b 74F04PC hex inverter pinouts Propagation delay (1) • What is it??? • It is defined to be the time between the 50% transition points of the input and output Propagation delay (2) • TpLH and TpHL together define the total propagation delay Tp = (TpLH + TpHL) / 2 • What causes the delay??? Capacitive Loading • Treat capacitor as a water bucket • The bigger the capacitor, the bigger the bucket • Treat inverter as a faucet • Filling the bucket takes time Capacitive Loading vs. Propagation Delay • Bigger fanout means lumping more capacitors at the output and thus longer time to fully charge up the capacitor Ring Oscillator • An odd number of inverters in a circular chain • No stable operation point exists; thus oscillates • Oscillates with a period T = 2 * Tp * N • In the lab, you will see that the frequency is dependent on the capacitive load at the output of the inverter Figure 2a 5-stage ring oscillator Transmission Line (1) Figure 3 More realistic model of a wire • A more realistic and accurate model of a wire is with inductance, resistance, and capacitance • As the wire gets longer, the effect can dominate the speed of the signal Transmission Line (2) • First major problem is that signals with high frequencies might get smeared out • Second major problem is that signals might reflect back and forth on the wire, taking a long time to settle down to a definite value Termination • Wire has a characteristic impedance • Your job is to match that impedance at the end of the wire • Example: If the ribbon cable has a characteristic impedance of 100 ohms, then you should have 100 ohms at the output end of the cable Capacitive Coupling Figure 4 Capacitive Coupling • In between two wires, there is always capacitive coupling which introduces an interference called cross-talk • We need to eliminate the cross-talk Shielding • Shield the wires with either Gnd or Vdd Note • In this lab, you will not need to use Xilinx • The lab is really easy and so you should spend more time studying for the midterm