(868 kB PowerPoint)

advertisement

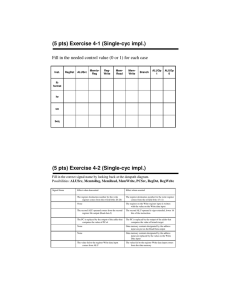

Pyxis April Lewis Aaron Martin Steve Sherk Pyxis1600 General-purpose 16-bit RISC microprocessor 16 16-bit registers 16-bit address bus Up to 64KB of addressable memory 2 Registers 16 registers 3 special purpose – $r0 – zero – $r14 – stack pointer – $r15 – return address 13 general purpose – $r1 - $r13 Status register (sr) – 8 bits – carry (c), overflow (o), negative (n), zero (z), interrupt enable (i), less than (l), 2 bits unused Program counter (pc) Accumulator high (ah) and accumulator low (al) – Used for multiply and divide Interrupt Return Address (IRA) – Register to hold return address from interrupt 3 Instruction Formats 15 R-type opcode 98 7 ext 43 rd 15 0 rs 0 Displacement / Immediate B-type 15 13 12 98 opcode branch type 0 address 16-bit instructions 7-bit opcode 1 bit to indicate information in next word rd is source and target rs is source Branch instructions use special format 4 Instruction Set Category Opcode [15:9] Opcode [8] Instruction Example Meaning add add <rd>,<rs> 0000001 0 r3 = r3 + r4 add immediate addi <rd>, #100 0000001 1 r3 = r3 + 100 subtract sub <rd>, <rs> 0000010 0 r3 = r3 - r4 subtract immediate subi <rd>, #200 0000010 1 r3 = r3 - 200 divide div <rd>, <rs> 0000100 0 <ah, al> = r3 / r4 divide immediate divi <rd>, #4 0000100 1 <ah, al> = r3 / 4 multiply mult <rd>, <rs> 0000011 0 <ah, al> = r3 * r4 multiply immediate multi <rd>, #6 0000011 1 <ah, al> = r3 * 6 move from al mal <rd> 1010000 x r4 = (al) move from ah mah <rd> 1011111 x r4 = (ah) load word lw <rd>, 100(<rs>) 0011111 1 r3 = Memory[r4 + 100] store word sw 200(<rd>), <rs> 0010000 1 Memory[r3 + 200] = r4 and and <rd>, <rs> 0000100 0 r3 = r3 & r4 andi andi <rd>, #4 0000100 1 r3 = r3 & 4 or or <rd>, <rs> 0000101 0 r3 = r3 | r4 ori ori <rd>, #4 0000101 1 r3 = r3 | 4 nor nor <rd>, <rs> 0000110 0 r3 = ~(r3 | r4) nori nori <rd>, #4 0000110 1 r3 = ~(r3 | 4) comp comp <rd>, <rs> 1111111 0 set sr bits after compare shl shl <rd>, #10 0000111 0 r3 = r3 << 10 shr shr <rd>, #10 0001000 0 r3 = r3 >> 10 Arithmetic Data Transfers Logical 5 Instruction Set Category Conditional Branch Unconditional Branch Opcode [15:9] Opcode [8] Instruction Example Meaning beq beq #100 1110000 x if sr[z] = 1, go to PC + 100 bne bne #100 1110001 x if sr[z] = 0, go to PC + 100 blt blt #100 1110010 x if sr[l] = 1, go to PC + 100 bgt bgt #100 1110011 x if (sr[l] = 0) & (sr[z] = 0), go to PC + 100 jmp jmp 2500 100xxxx 1 go to 2500 jmpl jmpl 2500 011xxxx x r15 = PC + 2, go to 2500 jmpr jmpr <rd> 010xxxx x go to r4 reti reti 001001 x enables interrupts and reloads PC no operation nop 0000000 x stall for one clock cycle Other Assembly to Machine Code Example add comp beq r3, r4; r10, r4; #25; jmpr r9; 0000001 0 0011 0100 1111111 1 1010 0100 1110000 x xxxx xxxx 0000 0000 0001 1001 010xxxx x 1001 0000 6 Addressing Modes Register direct Register indirect plus displacement – Use r0 for absolute addressing PC-relative Immediate 7 Datapath 8 Control Signals Signal Name PCWrite IorD MemRead MemWrite IRWrite MemToReg RegR/W PCCond PCSrc Actions of 1-bit Control Signals Effect When Deasserted Effect When Asserted The PC counter is updated to the value on the None bus ALUOut is used to supply the address to the The PC is used to supply the address to memory memory unit Contents of the memory at the location specified by the Address input is put on Memory data None output Memory contents at the location specified by the Address input is replaced by value on Write None data input None The output of memory is written into the IR The value fed to the register file Write Data input The value fed to the register file Write Data input comes from ALUOut comes from the Memory Data Register The general-purpose register selected by the Rs register number is written with the value of the None Write Data input The PC is written if the Zero output of the ALU is None active The output of the ALU (PC+4) is sent to the PC The PC is written with the value from the for writing Memory Data Register 9 Control Signals Actions of n-bit Control Signals Signal Name ALUSrcA ALUSrcB ALUOp Effect When Deasserted Effect When Asserted 00 The first input to the ALU is the contents of the A register 01 The first input to the ALU is the contents of the Memory Data Register 10 The first input to the ALU is the value of the PC 11 None 00 The second input to the ALU is the contents of the B register 01 The second input to the ALU is the contents of the Memory Data Register 10 The second input to the ALU is the value 2 11 The second input to the ALU is the value of the Instruction Register [8:0] 000 Add 001 Subtract 010 AND 011 OR 100 NOR 101 Set on less than 110 Multiply 111 Divide 10 State Transition Diagram 0 Fetch 1 IorD=0 MemRead=1 MemWrite=0 ALUOp=ADD ALUSrcA=2 ALUSrcB=2 PCSrc=0 PCWrite=1 RegWrite=0 Decode IRWrite=1 RegWrite=0 PCWrite=0 R-type (ext=1) Fetch Immediate 4 R-type (ext=0) 2 Execute ALUSrcA=0 ALUSrcB=0 ALUOp=OP IRWrite=0 RegWrite=0 PCWrite=0 Arithmetic Instructions Write to Reg from ALU Load from Memory Write to Memory Calc EA Write-back ALU to Reg RegWrite=1 MemtoReg=0 ALUOp=OFF IRWrite=0 Memory Read PCWrite=0 6 3 Write-back Mem to Reg RegWrite=1 MemtoReg=1 ALUOp=OFF IRWrite=0 PCWrite=0 IorD=0 MemRead=1 MemWrite=0 IRWrite=0 ALUOp=ADD ALUSrcA=2 ALUSrcB=2 PCSrc=0 PCWrite=1 RegWrite=0 7 Calc EA or Immediate IorD=1 MemRead=1 ALUOp=OFF RegWrite=0 IRWrite=0 PCWrite=0 ALUSrcA=1 ALUSrcB=0 ALUOp=OP IRWrite=0 RegWrite=0 PCWrite=0 8 5 ALUSrcA=0 ALUSrcB=1 ALUOp=ADD IRWrite=0 RegWrite=0 PCWrite=0 Memory Write 9 IorD=1 MemWrite=1 ALUOp=OFF RegWrite=0 IRWrite=0 PCWrite=0 To State 0 15 Check Interrupt 11 State Transition Diagram 0 Fetch 1 Decode IRWrite=1 RegWrite=0 PCWrite=0 IorD=0 MemRead=1 MemWrite=0 ALUOp=ADD ALUSrcA=2 ALUSrcB=2 PCSrc=0 PCWrite=1 RegWrite=0 R-type Jump &Link B-type 13 10 Compare ALUSrcA=0 ALUSrcB=0 ALUOp=SUB IRWrite=0 RegWrite=0 PCWrite=0 11 ALUSrcA=2 ALUSrcB=3 ALUOp=ADD PCCond=1 PCSrc=0 PCWrite=1 IRWrite=0 RegWrite=0 R-type Jump (ext=0) Update PC 12 Jump to Reg Addr ALUSrcA=0 ALUSrcB=0 ALUOp=ADD PCSrc=0 PCWrite=1 IRWrite=0 RegWrite=0 R-type Jump (ext=1) Save Return Addr RegWrite=1 MemtoReg=1 ALUOp=OFF IRWrite=0 PCWrite=0 14 Jump PCSrc=1 PCWrite=1 IorD=0 MemRead=1 MemWrite=0 ALUOp=OFF RegWrite=0 IRWrite=0 Conditional Branch Jump to Register Address Jump to Register Address and Link Jump to Immediate and Link Jump to Immediate To State 15 12 Interrupts Interrupts will be checked at the completion of each instruction An interrupt will trigger some extra states that send the processor to an Interrupt Service Routine (ISR), pre-programmed in code memory. These states will perform the following: – Save the processor’s state – Disable interrupts – Jump to the ISR The ‘RETI’ instruction will return the processor from the ISR 13 Virtex XCV300 FPGA XCV300 FPGA - 322,970 logic gates - 8 KB on-chip RAM - Block SelectRAM - Fast arithmetic carry - Clock Speed 10MHZ - Multiple I/O standards (LVTTL, LVCOMS2) 14 Input / Output Serial Interface UART Transmitter and Receiver Macros UART_TX 8-bit 16 Byte FIFO BUFFER UART_RX Serial 8-bit 16 Byte FIFO BUFFER Serial These macros are fully compatible with standard UART communications protocols such as to a PC, providing level shifting components are employed to generate RS232 signaling. The buffers will be interrupt driven. 15 Memory Timing Diagrams 32KB FLASH (AT29C256-70PC) Total access time is 70ns (tACC) 70ns 16 Memory Timing Diagrams 32KB SRAM (K6x0808C1D-DF70) Total access time is 70ns (tAA) 17 32KBx8 off-chip SRAM 32KBx8 off-chip FLASH 18 Parts List Item Vitex development board (PQ240-100 prototype Platform) Flash Memory 32KB x 8 SRAM 32KB x 8 Perf Board Level Shfters DIP sockets Max3232E RS232 cable Ribbon Cable and Headers QTY 1 2 2 1 5 10 1 1 3 19 Roles and Responsibilities Aaron – Logic design – Verilog programming – Hardware implementation April – Logic design – Verilog programming – Assembler Steve – Logic design – Verilog programming – Hardware implementation All – Test programs – Integration and Test – Documentation 20 Schedule 21 Questions