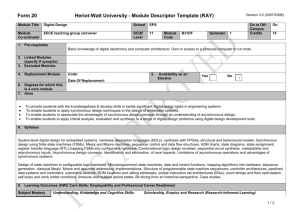

Lecture 34

advertisement

Lecture #34: data transfer • Last lecture: – Example circuits – shift registers – Adders – Counters • This lecture – Communications synchronous / asynchronous – Buses – Start transmission lines 11/19/2004 EE 42 fall 2004 lecture 34 1 Data transfer • In addition to computation, it is necessary to transmit information from one place to another. • Buses are used to move data from one logic device to another in parallel • If the devices are close together, the delay is the RC time to charge the capacitance. • If the devices are further apart, need to consider propagation velocity, distortion, crosstalk. 11/19/2004 EE 42 fall 2004 lecture 34 2 Multiplexer vs tri-state/bus • To send information to several different destinations, you can just run wires to each of the destinations. • But to have information from several sources go to the same destination, you need to control which device drives the destination, can not tolerate pulling up and down on the same wire. • This can be done using multiplexers, or by using tri-state drivers in a bus architecture 11/19/2004 EE 42 fall 2004 lecture 34 3 Multiplexer For example, if you have four inputs, you would need a 2 selector 4 input multiplexer for each bit of output. I1 I2 I3 I4 A B 11/19/2004 O 2 input decoder EE 42 fall 2004 lecture 34 4 Bus with tri-state drivers • To efficiently route information from many source, a bus can be driven by tri-state drivers. The logic must ensure that only one driver is active at a time. 11/19/2004 EE 42 fall 2004 lecture 34 5 Bus • A bus may be synchronous, to a clock edge for example, or asynchronous with handshaking and control lines Data 0 Data 1 Data 2 Data 3 Data 4 Data 5 Data 6 Data 7 Clock 11/19/2004 EE 42 fall 2004 lecture 34 6 Synchronous v. Asynchronous Clock Signal Synchronous Circuit Asynchronous Circuit Handshake Control 11/19/2004 EE 42 fall 2004 lecture 34 7 Synchronous • In a synchronous circuit, there is an explicit global synchronization through the clock signal. • The clock period is chosen to be longer than the worst case delay (gate delays + transmission delays) 11/19/2004 EE 42 fall 2004 lecture 34 8 Asynchronous circuit Ack R Logic R Logic Logic R R Req Synchronization with Req / Ack handshakes 11/19/2004 EE 42 fall 2004 lecture 34 9 asynchronous • Asynchronous design is often unavoidable: – User interfaces – Different speed devices – Clocks are difficult to distribute over long distances • More difficult to design, design tools generally have been synchronous only, but asynchronous design tools are being developed. • Most current devices us synchronous logic inside local blocks, and asynchronous communication between blocks. • What constitutes a “block” is shrinking as logic speeds increase. – Currently making jump to chips with multiple independent blocks, or fully asynchronous logic. 11/19/2004 EE 42 fall 2004 lecture 34 10 Metastability and Asynchronous inputs • Clocked synchronous circuits – Inputs, state, and outputs sampled or changed in relation to a common reference signal (called the clock) – E.g., master/slave, edge-triggered • Asynchronous circuits – Inputs, state, and outputs sampled or changed independently of a common reference signal (glitches/hazards a major concern) – E.g., R-S latch • Asynchronous inputs to synchronous circuits – Inputs can change at any time, will not meet setup/hold times – Dangerous, synchronous inputs are greatly preferred – Cannot be avoided (e.g., reset signal, memory wait, user input) 11/19/2004 EE 42 fall 2004 lecture 34 11 Synchronous communication 1 1 0 0 1 0 • Clock edges determine the time instants where data must be sampled • Data wires may glitch between clock edges (data must be stable for set–up/hold times) 11/19/2004 EE 42 fall 2004 lecture 34 12 Handling Asynchronous Inputs (cont’d) • What can go wrong? – Input changes too close to clock edge (violating setup time constraint) In In is asynchronous and fans out to D0 and D1 Q0 one FF catches the signal, one does not Q1 State of Q0 and Q1 is inconsistent CLK 11/19/2004 EE 42 fall 2004 lecture 34 13 Synchronization Failure • Occurs when FF input changes close to clock edge – FF may enter a metastable state – neither a logic 0 nor 1 – – May stay in this state an indefinite amount of time – Is not likely in practice but has some probability logic 1 logic 0 logic 1 small, but non-zero probability that the FF output will get stuck in an in-between state 11/19/2004 logic 0 oscilloscope traces demonstrating synchronizer failure and eventual EE 42 fall 2004 lecture 34 decay to steady state 14 Dealing with Synchronization Failure • Probability of failure can never be reduced to 0, but it can be reduced – (1) slow down the system clock: this gives the synchronizer more time to decay into a steady state; synchronizer failure becomes a big problem for very high speed systems – (2) use fastest possible logic technology in the synchronizer: this makes for a very sharp "peak" upon which to balance – (3) cascade two synchronizers: this effectively synchronizes twice (both would have to fail) asynchronous input D Q D synchronized input Q Clk 11/19/2004 EE 42 fall 2004 lecture 34 15 synchronous system Edge-Triggered Flip-Flops • More efficient solution: only 6 gates – sensitive to inputs only near edge of clock signal (not while high) holds D' when clock goes low R Q Clk=1 S Q’ holds D when clock goes low D 11/19/2004 EE 42 fall 2004 lecture 34 negative edge-triggered D flip-flop (D-FF) 4-5 gate delays must respect setup and hold time constraints to successfully capture input characteristic equation Q(t+1) = D 16 Definition: Set up time/hold time Tsu Th data D Q D Q input clock clock stable changing data clock To ensure that the data signal is captured accurately, the data must be stable for an time tsu (set up) before the edge, and kept constant for a time th (hold) after the edge. 11/19/2004 EE 42 fall 2004 lecture 34 17 Handling Asynchronous Inputs • • If you have to deal with an input which could change at any time, not under you control, what do you do? Never allow asynchronous inputs to fan-out to more than one flipflop – Synchronize as soon as possible and then treat as synchronous signal Clocked Synchronous System Async Input D Q Synchronizer Q0 Async Input D Q D Q Clock Clock D Q Q1 Clock 11/19/2004 EE 42 fall 2004 lecture 34 Q0 D Q Q1 Clock 18 Asynchronous Logic Ack R Logic R Logic Logic R R Req Current practice is starting to embrace asynchronous logic design even on a single chip 11/19/2004 EE 42 fall 2004 lecture 34 19 Key Design Differences • Synchronous logic design: – Does not need to take timing correctness (hazards) into account in many cases – Combinational logic and memory latches are built separately – Static timing analysis of the logic is sufficient to determine the max delay and the required clock period. 11/19/2004 EE 42 fall 2004 lecture 34 20 Difficulties with asynchronous design • Synchronous logic: – Only functional correctness aspect must be verified and tested • Asynchronous logic: – In addition to functional correctness, timing must be analyzed – Operation may change for each different operation and operation rate – Testing is more difficult – Most circuit designers learn only synchronous design. – Most CAD tools only support synchronous design. – Asynchronous circuit CAD tools are being developed. 11/19/2004 EE 42 fall 2004 lecture 34 21 Clock skew • A major difficulty with synchronous communications is the fact that the clock must also travel some distance. • The clock being different from one place in a circuit to another is called clock skew. • For communications over a distance of a meter or so, parallel busses are being abandoned in favor of higher speed asynchronous serial communications. • Examples parallelUSB PCI PCI express 11/19/2004 EE 42 fall 2004 lecture 34 22 Serial transmission • Parallel-to-serial conversion for serial transmission parallel outputs parallel inputs serial transmission 11/19/2004 EE 42 fall 2004 lecture 34 23 Long signal paths • Signal delay – Component delay + interconnection delay • Signal integrity • • • • 11/19/2004 Reflections Waveform distortion Signal attenuation Crosstalk EE 42 fall 2004 lecture 34 24 Gate delay • So far, the only delay that we have considered is the time needed to charge up the capacitance due to lines, and due to the capacitance of the gates of the next stage. • This implies that if we could only push enough current, we can make the delay as short as we like. R Wire 11/19/2004 EE 42 fall 2004 lecture 34 Gates 25 Gate delay • If we want to speed up logic, we can increase the drive – reduce the pull up and pull down resistance • or we can reduce the capacitance. – Shorter lines, narrower lines, reduced dielectric constant of dielectric between wires. This is limited, however by the speed of light 11/19/2004 EE 42 fall 2004 lecture 34 26 Light speed • With lines that are long enough, or switching speeds are high enough, then we can not consider the delay to be simply that due to charging up the capacitance. The signal will propagate along a wire at the speed of light (in the dielectric, which is slower than that in air or vacuum) • Quite a bit of current is necessary to pull up a line that fast, for a 1 volt signal, 10-20 milliamps are required. 11/19/2004 EE 42 fall 2004 lecture 34 27 Transmission Line • When a signal wire is driven with that fast a rise time compared to its length, a signal will travel along the wire at the speed of light in the media. • It is even possible to turn off the current, and have the pulse that is already on the line continue to propagate toward the destination • So you don’t have to wait for one bit to arrive before you send the next 11/19/2004 EE 42 fall 2004 lecture 34 28 Transmission Line • As the voltage pulses propagate down the line, there is a current pulse which travels down the line with them. • The current is always balanced between two conductors, for example forward in one conductor, and backward in the other 11/19/2004 EE 42 fall 2004 lecture 34 29 Transmission Line • Voltage • Current in (+) signal line • Current in (-) signal line, or current in ground • If the signal is conducted in a pair of lines, it is called a balanced line. If the return path is through a ground, it is called unbalanced 11/19/2004 EE 42 fall 2004 lecture 34 30 Transmission line impedance • The ratio of the voltage of propagating pulses to the current the carry is a constant, called the impedance of the line Z0 Vpulse I pulse • A typical transmission line impedance is 50-100 ohms. • When a line is being used in this fashion, it can not be split into two, because for a given voltage, twice as much current would be needed • So digital transmission lines do not branch, there is only one path from one end to another. 11/19/2004 EE 42 fall 2004 lecture 34 31 Transmission line termination • Since a transmission line carries pulses of voltage and current, there must be somewhere for the current to go. • FET devices are very high impedance, so they don’t absorb that current • All that is required to absorb the current at the end of the transmission line is a resistor which has the same resistance as the impedance of the line Rtermination=Z0 11/19/2004 EE 42 fall 2004 lecture 34 32