BJT Common Emitter Amplifier 1 Intro David Baird

advertisement

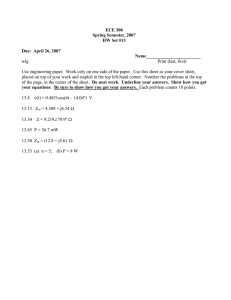

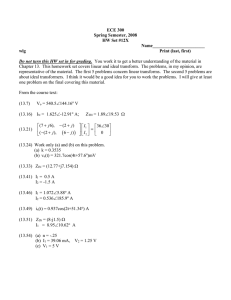

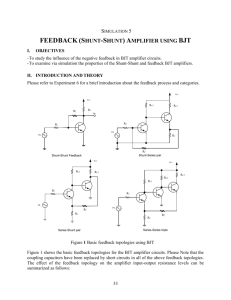

BJT Common Emitter Amplifier David Baird 2002 Nov 4 1 Intro I intend to build a two stage BJT common emitter amplifier. Here are my design constraints: Accept a source resistance of 10kΩ and voltage of 40mVp−p Drive a 2kΩ load Have a gain near 200 2 Setup +15V IEE2 4mA C4 100µF RCC1 22k 4.7V -4.7V VBB1 Rs 10k Vi VCC1 4V ZIN -7V VCC2 22k Vo -5.4V VEE1 5.6k 2x 2N3906 Ree1 1k C2 10µF 82Ω 5.4V 2N3904 C1 .47µF 10k Ree2 VEE2 IEE1 .4-.6mA C5 10µF 2k ZOUT RCC2 2k Re2=25mV/4.5mA = 5.56Ω C3 10µF -15V Re1=25mV/.5mA = 50Ω David Baird xcircuit Drawing Lab 9, Final Circuit EE321 Figure 1: BJT amplifier with theoretical DC bias values Figure 1 shows the setup I used. I used current sources to greatly simplify the biasing of the transistors. The first BJT stage has a gain of about 20 and the second has a gain of about 10. The first stage input is bootstrapped. The goal of this is to make the resistor divider bias disappear at high frequency so that the signal source only sees the (β + 1)(re + Ree ), which should be much larger than Rs = 10kΩ. The second BJT stage uses a darlington to unload the first stage. Most of my calculations assume the input impedance to the transistor is negligible. 1 +15V .51mA 100k 470Ω 4.7k 13.1V -12.3V 12.4V -13V 22k 3.9k 22k 4mA -15V Figure 2: Current sources used in the amplifier All the capacitors form high pass filters with a 3dB point at 20Hz or less. The following table shows the R and C values, and the 3dB frequency for each capacitor: Capacitor C1 C2 C3 C4 C5 R [Ω] > 100k 3k 1k 82 4k (?) C [µF ] .47 10 10 100 10 f3dB [Hz] < 3.4 5.3 16 19 4.0 The emitter bypassing required the largest capacitors, as you can see, because they had the smallest source resistances. The amplifier gains are determined approximately by Rcc /(Ree + Re ). This gives stages 1 and 2 gains of 22k/(1k + 50) = 21 and 1k/(82 + 5.6) = 11.4. The composite gain should then be 21 · 11.4 = 239. ...so, the gain is a little greater than 200. 3 3.1 Data DC values Honestly, the actual values were so close to my expected values that I didn’t really care to investigate the exact reasons for deviation. 2 Parameter Vsup+ 15 Vsup− -15 VBB1 VCC1 VEE1 VCC2 VEE2 IEE1 IEE2 3.2 Expected -4.7 4 -5.4 -7 5.4 .51 4 Comment f=10kHz f=10kHz f=10kHz f=10kHz Vop−p /Vip−p Vo /Vs Expected 21 11.4 239 Actual 45.6 35.2 .840 8.24 23.9 9.81 234 181 Unit mV mV V V - AC gains f [Hz] 100 1k 10k 3.4 Unit V V V V V V V mA mA AC values Parameter Vs p-p Vi p-p Vee1 p-p Vo p-p Av1 Av2 Av AlternateAv 3.3 Actual 14.86 -14.82 -4.7 4.12 -5.25 -6.64 5.35 .50 4.0 Vs [mV] 40 40 40 Vi [mV] 36 36 36 Vo [V] 7.4 7.76 8.24 Av = Vo /Vi 206 216 229 Vo /Vs 185 194 206 AC Impedances Figure 3 shows the setups I used to measure ZIN and ZOU T . To measure ZIN , I kept adding resistance to the input until the output decreased by a factor of 2. At this point, the total input resistance must be equal to the resistance looking into the amplifier. The process for finding Z OU T is similar: decrease output resistance until the output voltage decreases by a factor of two. This resistance must then be the resistance looking into the output of the amplifier. ZIN is the only value that deviated much from what I had expected. I’m not totally sure why, but I would guess that the bootstrap I made isn’t working as well as expected. I expect the AC resistance looking into the base of the BJT should be over 100kΩ, which means the AC resistance of the bootstrap must be around 150kΩ (if base=150kΩ) in order for ZIN = 76kΩ. Then again, considering that the bias network goes from about 10k at DC to 150k (factor of 15) at AC makes bootstrapping a pretty neat trick! RL [kΩ] inf 2.0 1.0 Vo [Vp−p ] 15.2 7.68 5.16 3 (a) 39.2mV p-p 17mV p-p 10k 56k 4.88V p-p 1kHz (b) 10k 36mV p-p RL 1kHz Figure 3: Circuits used when (a) determining ZIN , (b) determining ZOU T Parameter ZIN ZOU T 4 Comment Expected > 100 2 Actual 76 2.0 Unit kΩ kΩ Conclusions I built an amplifier with 2 common emitter BJT stages. I used bootstrapping for my first time and found that it works quite nicely. It increased the input impedence of the bias network by a factor of 15 for AC signals. I also found that using current sources at the transistor emitters helps to simplify biasing because I no longer had to consider emitter DC resistors. I found the input impedance to be a little less than 100k and the output impedence to be equal to the collector resistor (2k). I had some blunders along the way. I learned that you cannot simply replace the collector resistors with current sources in a common emitter amplifiers to achieve very high gain. A better way to get high gain is to use a differential input stage with a current source on one side and take negative feedback from the output. I was having trouble getting my experimental circuits (differential + follower) to have enough open loop gain (I think) to work well for a closed loop gain around 200 (they worked great for 20!). 4