SignalProbe Compilation Enables Fast System

Debugging with the Quartus II Software

Technical Brief 82

September 2002, ver. 2.1

Introduction

Hardware verification options help designers reduce design cycles and time-to-market for

system-on-a-programmable-chip (SOPC) designs. Quick, easy access to internal device

signals is important in debugging a programmable logic device (PLD) design. It is also

important that this access not affect the design’s functionality or performance.

Altera Corporation

101 Innovation Drive

San Jose, CA 95134

The Altera® Quartus® II software version 2.0 introduces the SignalProbeTM incremental

(408) 544-7000

routing feature, which allows designers to quickly route signals to I/O pins for efficient

http://www.altera.com

https://websupport.altera.com signal verification without affecting the design. Starting with a fully routed design, the

designer selects and routes signals for debugging to either previously reserved or currently

unused I/O pins.

Hardware Verification Methods

After place-and-route, signal debugging methods in a design can include:

■

■

■

Manually assigning signals to I/O pins and performing a full recompilation

Using the Quartus II software’s SignalTap® Logic Analyzer and performing a full

recompilation

Using the Quartus II software’s SignalProbe feature

The following paragraphs describe the benefits and drawbacks of these methods. See

Table 1 for a summary of these benefits and drawbacks.

Manual Signal Assignment to I/O Pins and Full Recompilation

Designers can debug signals through manual assignment of signals to I/O pins and a full

design recompilation. This method involves placement and routing changes to the design

to accommodate the I/O pin assignments and can raise the following issues:

■

■

■

Total recompilation can take a long time.

The new routing can affect the signals being debugged.

The design operation can change and affect the design’s functionality or performance.

SignalTap Logic Analyzer

Designers can also use the SignalTap Logic Analyzer, available in the Quartus II software,

for hardware verification. Through the routing of internal signals to pins or the use of

internal device memory resources and the Joint Test Action Group (JTAG) interface,

designers can access internal design nodes. However, using the SignalTap Logic Analyzer

requires a full design recompilation.

When device memory resources are limited or the device board does not have JTAG port

connections, designers can use the SignalProbe feature to perform signal debugging.

f

Altera Corporation

TB-082-2.1

For more information on the SignalTap Logic Analyzer, go to “Overview: Using the

SignalTap Logic Analyzer” in the Quartus II Help or see Application Note 175 (SignalTap

Analysis in the Quartus II Software Version 2.0).

1

TB 82: SignalProbe Compilation Enables Fast System Debugging with the Quartus II Software

SignalProbe Feature

Designers can also use the SignalProbe feature for hardware verification. The

SignalProbe feature performs the re-routing of signals in about 5% of the time required

by a full design recompilation. The incremental routing process preserves results of the

prior compilation, which does not affect the signals’ behavior or the design’s operation.

Table 1. Comparison of Signal Debugging Methods

Method

Benefits

Drawbacks

SignalProbe feature

The SignalProbe feature’s compilation completes in about 5% Signals may not always find successful reof the time required by a full design recompilation and re-routed route.

signals do not affect signal behavior or design operation.

SignalTap Logic

Analyzer

Does not require using any device I/O pins for analysis.

Requires device memory resources and full

compilation to configure the SignalTap Logic

Analyzer.

Full compilation

The Quartus II software has more flexibility to re-route the

signals.

Time-consuming and the design can

change, potentiality affecting design

functionality and performance.

Using the SignalProbe Feature

Following are the general steps required to use the SignalProbe feature:

1.

Before using the SignalProbe feature, perform a full design compilation with the

Quartus II software’s Smart compilation option turned on.

2.

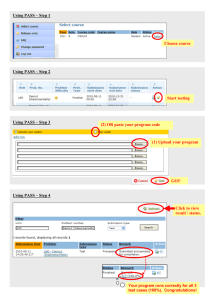

Use Assign Pins in the Target Device section of the Chips and Devices tab of the

Compiler Settings dialog box (Processing menu) to select signals for debugging

(and the reserved or currently unused I/O pins to which to route them), specify

nodes to re-route to I/O pins, and turn on the SignalProbe feature. Figure 1 shows

the Assign Pins dialog box.

Figure 1. Assign Pins Dialog Box

Altera Corporation

2

TB 82: SignalProbe Compilation Enables Fast System Debugging with the Quartus II Software

3.

Recompile the design. There are two ways to recompile the design:

(a) Use Start SignalProbe (Processing menu) to run a compilation independent

of the normal compilation process. The SignalProbe compilation can complete in

as little as 5% of the time required for a full recompilation.

(b) Turn on “Automatically route SignalProbe signals during compilation” in the

Mode tab of the Compiler Settings dialog box (Processing menu). Use Start

Compilation (Processing menu) to perform a normal compilation of the project.

1

If a selected signal cannot be re-routed without affecting the current

design operation, the Quartus II software does not re-route the signal and

displays a warning message.You can specify the compiler to have

flexibility in modifying the latest fitting results by turning on Modify

latest fitting results during SignalProbe compilation (see Figure 2).

Figure 2. Compiler Settings

4.

Load the Altera device with the new programming data to examine the signals.

1

5.

Altera Corporation

Guarantee specific pins are available for use by the SignalProbe feature

by reserving them before the initial compilation.

Repeat the procedure for further analysis on different signals or click Disable All

SignalProbe Routing to remove the SignalProbe routing from the design (see

Figure 1).

3

TB 82: SignalProbe Compilation Enables Fast System Debugging with the Quartus II Software

SignalProbe Feature Requirements

The following are SignalProbe feature requirements:

■

■

■

■

Supported devices—StratixTM, CycloneTM, APEXTM II, APEX 20KE, APEX 20KC,

APEX 20K, and ExcaliburTM devices.

Compiler settings—Initial compilation must be done with smart compilation

turned on and a synthesis tool specified.

Pins for analysis—Must not already be assigned for use in the design and cannot

be an Excalibur Stripe I/O pin, an output pin, a group, or bus, and cannot have a

carry or cascade fan-out.

Nodes for analysis—Must be post-compilation and cannot be carry-out or cascadeout signals, groups, or output signals.

For more information on using the SignalProbe feature, go to “Performing a

SignalProbe Compilation on a Design” in the Quartus II Help.

Conclusion

Using the SignalProbe feature, the signal re-routing process can complete in as little as

5% of the time required for a full recompilation. The SignalProbe feature gives quick

access to internal design signals to Altera designers for system-level debugging.

®

101 Innovation Drive

San Jose, CA 95134

(408) 544-7000

http://www.altera.com

4

Copyright © 2002 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific

device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the

trademarks and service marks of Altera Corporation in the U.S. and other countries.* All other product or service names are the property of

their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights,

and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard

warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or

liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing

by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

Altera Corporation