ATM Cell Processor

622 Mbps MegaCore

Function (CP622)

August, 2001; ver. 1.01

Data Sheet

■

■

■

■

Features

■

■

■

Typical

Applications

Full-duplex processing capability

Up to 622.08 megabits per second (Mbps) transmission rate

Easy-to-use MegaWizard® Plug-In generates MegaCore® variants

Quartus® software and OpenCore® feature allow place-and-route,

and static timing analysis of designs prior to licensing

Secure register transfer level (RTL) simulation models allow

simulation with user design in third-party simulators

Optimized for the Altera® APEXTM 20KE device architecture

Complies with all applicable standards, including:

–

International Telecommunications Union, Recommendation,

ISDN User Network Interfaces, ITU-T I.432, March 1993

–

ATM Forum, Utopia, An ATM-PHY Interface Specification, Level 2,

Version 1.0, af-phy039.000, June 1995

–

Altera Corporation, AtlanticTM Interface Functional Specification.

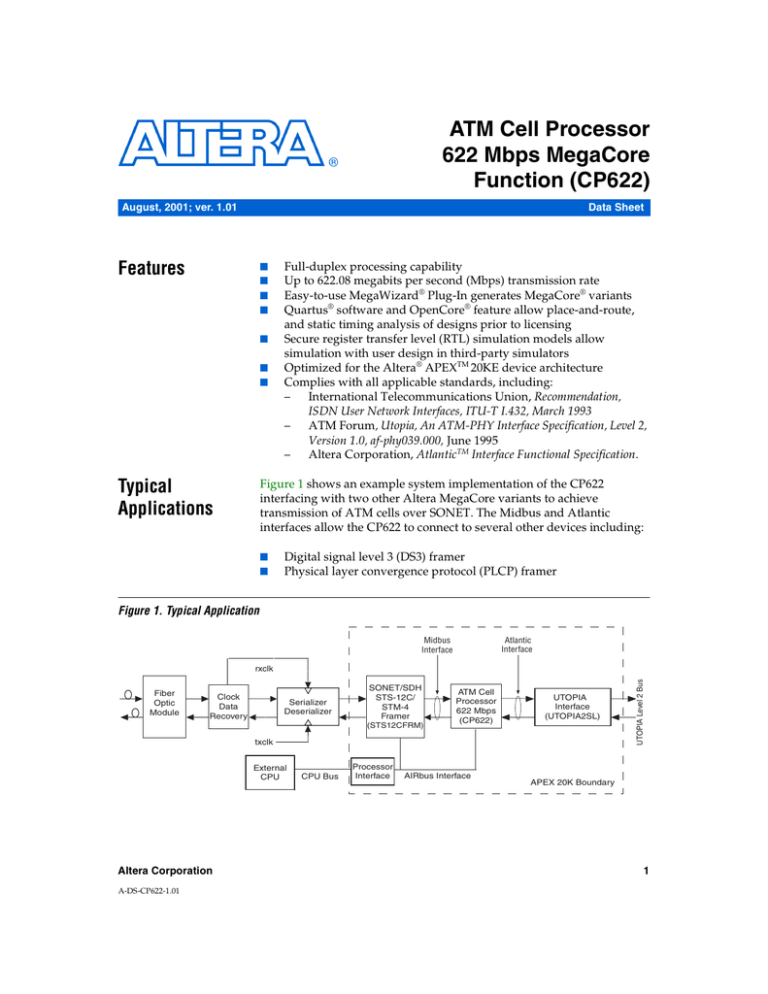

Figure 1 shows an example system implementation of the CP622

interfacing with two other Altera MegaCore variants to achieve

transmission of ATM cells over SONET. The Midbus and Atlantic

interfaces allow the CP622 to connect to several other devices including:

■

■

Digital signal level 3 (DS3) framer

Physical layer convergence protocol (PLCP) framer

Figure 1. Typical Application

Atlantic

Interface

Midbus

Interface

Fiber

Optic

Module

Clock

Data

Recovery

Serializer

Deserializer

SONET/SDH

STS-12C/

STM-4

Framer

(STS12CFRM)

ATM Cell

Processor

622 Mbps

(CP622)

UTOPIA

Interface

(UTOPIA2SL)

txclk

External

CPU

Altera Corporation

A-DS-CP622-1.01

CPU Bus

Processor

Interface

AIRbus Interface

UTOPIA Level 2 Bus

rxclk

APEX 20K Boundary

1

ATM Cell Processor 622 Mbps MegaCore Function (CP622) Data Sheet

Functional

Description

The CP622 is capable of performing all of the operations required to

support the transmission convergence (TC) layer of an ATM Physical

(PHY) device. It operates in full-duplex mode, and comprises two blocks,

as illustrated in Figure 2.

■

■

2

The following list of functions is based on a full-feature CP622.

See Table 2 for all possible options.

ATM transmission convergence receiver (RXATC)

–

ATM cell delineation

Byte alignment (software programmable)

Loss of cell delineation indication

–

Header single-bit error correction, and multi-bit error detection

(software programmable)

–

External ATM cell generic flow control (GFC) extraction

(software programmable)

–

Payload descrambling (software programmable)

–

Discarding of operations, administration, and maintenance

(OAM) cells and selectable cell filtering

–

Cell insertion and extraction through AIRbus interface

–

Performance monitoring of received corrected, corrupted, and

filtered cells

–

ATM cell formatting (8 to 16 bits)

ATM transmission convergence transmitter (TXATC)

–

ATM cell formatting (16 to 8 bits)

–

Discarding of OAM cells and selectable cell filtering

–

Cell insertion and extraction through AIRbus interface

–

Performance monitoring of transmitted corrected, corrupted,

and filtered cells

–

Internal header error control (HEC) generation and insertion

(software programmable)

–

External ATM cell GFC insertion (software programmable)

–

Payload scrambling (software programmable)

–

Cell rate decoupling with programmable idle cell header and

payload

Altera Corporation

ATM Cell Processor 622 Mbps MegaCore Function (CP622) Data Sheet

Interfaces &

Protocols

Three interfaces support the CP622: the middle interface (Midbus), the

access to internal registers (AIRbus) interface, and the Atlantic interface.

Midbus Interface

The Midbus interface is a simple synchronous full-duplex data path bus.

The CP622 Midbus runs at 77.76 MHz over a single byte lane in each

direction. In the receive direction (RX), data is transferred from the

Midbus master to the slave (CP622). In the transmit direction (TX), data is

transferred from the slave (CP622) to the master. In each direction, the

Midbus can carry eight bits per clock cycle. It includes Midbus receive

data (mrxdat[7:0]) and Midbus receive enable (mrxena) lines to

indicate valid data transfers in the RX direction, and Midbus transmit data

(mtxdat[7:0]) and Midbus transmit enable (mtxena) lines to indicate

valid data requests in the TX direction. Since the CP622 is a slave to the

Midbus it can work with any Midbus master.

AIRbus Interface

The AIRbus interface provides access to internal registers using a simple

synchronous internal bus protocol. This consists of separate read data

(rdata[15:0]) and write data (wdata[15:0]) buses, a data transfer

acknowledge (dtack) signal, and a select (sel) signal. An address

(addr[7:1]) bus and read (read) signal indicate the location and type of

access within the block. The rdata buses and dtack signals can be

merged from multiple blocks using a simple OR function. The dtack

signal is sustained until the block sel is removed (four-way

handshaking) meaning the AIRbus can cross clock domain boundaries.

The CP622 is an AIRbus slave with a data width of 16 bits.

Atlantic Interface

The Atlantic interface is a full-duplex synchronous bus protocol

supporting both packets and cells. The CP622 is an Atlantic interface

master using a 16-bit wide data path to deliver cells to the slave. An

example of a slave is the UTOPIA interface MegaCore variant shown in

Figure 1. The UTOPIA interface MegaCore variant includes a multi-cell

first-in first-out (FIFO) buffer for crossing the clock domain.

B

Altera Corporation

More detailed information on the Midbus, AIRbus, and Atlantic interfaces

is available from the Altera web site at http://www.altera.com.

3

ATM Cell Processor 622 Mbps MegaCore Function (CP622) Data Sheet

Figure 2. Block Diagram

CP622

rxclk

rxreset_n

Midbus

Interface

GFC

Extraction

Interface

arxena

RXATC

arxdav

mrxdat[7:0]

mrxena

arxdat[15:0]

rxgfcclk

arxsop

rxgfcfp

arxeop

rxgfc

lcd

arxerr

Atlantic

Interface

rxcp

atxena

txclk

txreset_n

Midbus

Interface

GFC

Insertion

Interface

atxdav

TXATC

mtxdat[7:0]

atxval

mtxena

atxdat[15:0]

txgfcclk

atxsop

txgfcfp

atxeop

txgfc

atxerr

irq

dtack

rdata[15:0]

wdata[15:0]

addr[7:1]

read

sel

txcp

AIRbus Interface

I/O Signals

The following is a port list for the CP622. The signal direction is indicated

by (I) for input, or (O) for output.

RX Clock Domain Signals: rxclk (I), rxreset_n (I); Midbus Signals:

mrxdat[7:0] (I), mrxena (I); GFC Extraction Signals: rxgfcclk (O),

rxgfcfp (O), rxgfc (O); Miscellaneous Signals: lcd (O), rxcp (O);

Atlantic Signals: arxena (O), arxdav (I), arxdat[15:0] (O), arxsop

(O), arxeop (O), arxerr (O).

AIRbus Signals: sel (I), read (I), addr[7:1] (I), wdata[15:0] (I),

rdata[15:0] (O), dtack (O), irq (O).

TX Clock Domain Signals: txclk (I), txreset_n (I); Midbus Signals:

mtxdat[7:0] (O), mtxena (I); GFC Insertion Signals: txgfcclk (O),

txgfcfp (O), txgfc (I); Miscellaneous Signal: txcp (O); Atlantic

Signals: atxena (O), atxdav (I), atxval (I), atxdat[15:0] (I),

atxsop (I), atxeop (I) atxerr (I).

4

Altera Corporation

ATM Cell Processor 622 Mbps MegaCore Function (CP622) Data Sheet

Performance

Table 1 shows the required speed and estimated gate count of the CP622

in an APEX 20KE device.

Table 1. Performance

Note (1)

LEs

ESBs

fMAX (MHz)

1,917 – 4,834

0–4

77.76 required to support 622.08 Mbps

Notes:

(1)

Generating

Variants

The numbers for the logic elements (LEs) and the embedded system blocks (ESBs)

are approximate as of August 2001. They reflect the range from the basic to the fullfeature variant.

Table 2 shows the optional features available to generate all variants.

Table 2. Optional Features

Options

Parameters

Choices

Generic cell filters (1)

FILT

0,1,4

Cell insertion and extraction to processor interface (2)

CIE

Y/N

Performance monitoring of—received or

transmitted—corrected, corrupted, and filtered cells

(3)

PM

Y/N

Basic Configuration

Notes:

(1)

(2)

(3)

Licensing

An OAM cell filter is included in the base core design to filter OAM cells.

Requires one or four generic cell filters.

Yes allows all performance monitor counts: received cells, transmitted cells,

discarded cells, corrected HECs, uncorrected HECs, HEC error cells, Atlantic error

cells, OAM cells, and generic filtered cells. No allows only a count of errored cells.

A license is not required to perform the following trial operations using

your own custom logic:

■

■

■

■

Instantiation

Place-and-route

Static timing analysis

Simulation on a third-party simulator

Only when you are ready to generate programming files, do you need to

obtain licenses through your local Altera sales representative.

Altera Corporation

All current variants use a single license with ordering code:

PLSM-CP622.

5

ATM Cell Processor 622 Mbps MegaCore Function (CP622) Data Sheet

Deliverables

The following elements are provided with the CP622 package:

■

■

■

■

■

■

101 Innovation Drive

San Jose, CA 95134

(408) 544-7000

http://www.altera.com

Applications Hotline:

(800) 800-EPLD

Customer Marketing:

(408) 544-7104

Literature Services:

lit_req@altera.com

6

Data sheet

User guide

Midbus, AIRbus, and Atlantic interface functional specifications

MegaWizard Plug-In

–

Encrypted gate level netlist

–

Place-and-route constraints (where necessary)

–

Secure RTL simulation model

Demo testbench

Access to problem reporting system

Copyright © 2001 Altera Corporation. Altera, The Programmable Solutions Company, the stylized Altera logo,

specific device designations, and all other words and logos that are identified as trademarks and/or service

marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and

other countries. All other product or service names are the property of their respective holders. Altera products

are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and

copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance

with Altera’s standard warranty, but reserves the right to make changes to any products

and services at any time without notice. Altera assumes no responsibility or liability arising

out of the application or use of any information, product, or service described herein except

as expressly agreed to in writing by Altera Corporation. Altera customers are advised to

obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services. All rights reserved.

Altera Corporation