®

Stratix GX

The Low-Risk Path to 3.125-Gbps Transceiver Applications

October 2002

The Low-Risk Path to 3.125-Gbps

Tranceiver Applications

Today’s high-speed applications need

a reliable data transfer technology

that transmits information from source

to destination in nanoseconds. To meet this need, Altera

introduces the Stratix™ GX device family. Stratix GX

FPGAs incorporate Altera's second-generation transceiver

technology and provide a low-risk path to 3.125-Gbps

transceiver applications.

Stratix GX FPGAs integrate a highly optimized 3.125-Gbps

transceiver that includes customer-defined features such as

a 40-inch drive strength capability, receiver equalization

circuitry, channel alignment, and embedded 8B/10B encoding

and decoding. In addition, the high I/O bandwidth provided

by the Stratix GX transceiver blocks is complemented by

support for an embedded silicon implementation of dynamic

phase alignment (DPA) to enable source-synchronous

operation at up to 1 Gbps.

Using Stratix GX devices, system architects have a powerful

fusion of the innovative Stratix device architecture and a

high-performance, multi-gigabit transceiver. They can use

these features for a wide range of applications: from communications to high-end consumer electronics to mass storage

systems. Table 1 describes some of the highlights of Stratix GX

devices, and Table 2 shows the wide range of Stratix GX

device features and available packages.

High-Bandwidth I/O Standards & HighSpeed Interfaces

Many industries today are driven by the need for high-speed

communication in both chip-to-chip and backplane applications. Stratix GX devices incorporate dedicated gigabit

transceiver blocks with encoded clock data recovery (CDR)

technology to receive and transmit high-speed serial data

streams for easy-to-use access to 3.125-Gbps transceiver

technology. These second-generation transceivers build upon

the industry-leading 1.25-Gbps CDR transceivers available

in Altera's Mercury™ devices. Stratix GX devices also feature

an embedded silicon implementation of DPA for high-speed

source-synchronous parallel interfaces to complement the

transceiver capabilities.

Stratix GX Gigabit Transceiver Blocks

Each Stratix GX transceiver block features four independent,

full-duplex channels that are capable of serial bit rates from

622 Mbps to 3.125 Gbps. Each transceiver channel contains

dedicated circuitry for speed-critical and logic-intensive

physical layer functions, as shown in Figure 1. The dedicated

circuitry includes a word aligner, rate matcher, channel

aligner, and 8B/10B encoder/decoder. Together, these features

simplify standard protocol implementation.

The Stratix GX gigabit transceiver channels support the

1.5-V PCML electrical standard, programmable differential

output voltage (VOD), pre-emphasis, receiver equalization,

and on-chip termination. These channels can drive up to

40 inches of FR4 backplane with two backplane connectors at

3.125 Gbps. The gigabit transceiver channels are designed

to operate with devices from leading transceiver vendors.

Stratix GX devices provide support for many high-speed

serial interface protocols, as shown in Table 3 on page 4.

The multi-gigabit transceiver channels seamlessly connect

to the programmable logic through 8-, 10-, 16-, or 20-bit

interfaces. Altera offers a variety of optimized intellectual

property (IP) cores for physical and media access control

(MAC) layer functions for these protocols. Combined with

dedicated loopback and built-in self-test (BIST) circuitry,

Stratix GX devices provide a complete solution for high-speed

communication applications.

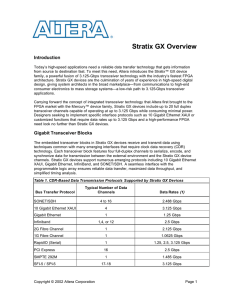

Table 1. Stratix GX Highlights

Feature

Benefit

3.125-Gbps Transceiver Blocks

Embedded transceiver blocks including 8B/10B encoder/decoder circuitry provide support for high-speed

applications such as 10 Gigabit Ethernet XAUI, Gigabit Ethernet, InfiniBand, 1G and 2G Fibre Channels,

Serial RapidIO™, SONET/SDH, SFI-5, SPI-5, PCI Express, and SMPTE 292M standards

40-Inch Drive Strength

Capability

Transceiver capabilities, embedded programmable pre-emphasis, and embedded receiver equalization combine

to enable a 40-inch signal drive capability across an FR4 backplane and two backplane connectors

Low Power Consumption

450-mW power consumption per 4-channel transceiver block simplifies board design

Optimal Channel-to-Logic Ratio

Device densities ensure sufficient logic for system implementation

Source-Synchronous Differential

I/O Signaling with DPA (1)

Support for high-speed I/O standards and high-speed interfaces such as 10 Gigabit Ethernet XSBI, SFI-4,

SPI-4 Phase 2 (POS-PHY Level 4), HyperTransport™, RapidIO, and CSIX streaming standards at up to 1 Gbps

to complement transceiver bandwidth

High-Performance Stratix

Device-Based Architecture

Highly optimized FPGA architecture provides innovative routing architecture for block-based design and

maximum system performance. Features such as TriMatrix™ memory, digital signal processing (DSP) blocks,

Terminator™ technology, and clock management circuitry enable full system implementation

Note: (1) DPA can be bypassed for protocols disallowing skews such as UTOPIA IV.

2

Altera Corporation

Table 2. Stratix GX Family Overview

Feature

Logic Elements (LEs)

EP1SGX10C

EP1SGX10D

EP1SGX25C

EP1SGX25D

EP1SGX25F

EP1SGX40D

EP1SGX40G

10,570

10,570

25,660

25,660

25,660

41,250

41,250

Transceiver Channels (1)

4

8

4

8

16

8

20

Source-Synchronous

Channels (1)

22

22

39

39

39

45

45

M512 RAM Blocks

94

94

224

224

224

384

384

M4K RAM Blocks

60

60

138

138

138

183

183

M-RAM Blocks

1

1

2

2

2

4

4

Total RAM Bits

920,448

920,448

1,944,576

1,944,576

1,944,576

3,423,744

3,423,744

DSP Blocks

6

6

10

10

10

14

14

Embedded Multipliers (2)

48

48

80

80

80

112

112

PLLs

4

4

4

4

4

8

8

Maximum User I/O Pins

Available Packages

328

328

424

540

540

542

542

672-Pin

FineLine BGA®

672-Pin

FineLine BGA

672-Pin

FineLine BGA

672-Pin

FineLine BGA

1,020-Pin

FineLine BGA

1,020-Pin

FineLine BGA

1,020-Pin

FineLine BGA

1,020-Pin

FineLine BGA

Notes:

(1) Number of full-duplex transceiver or source-synchronous channels.

(2) Total number of embedded 9x9 multipliers. To obtain the total number of 18x18 multipliers per device, divide the total number of 9x9 multipliers by 2. To obtain the

total number of 36x36 multipliers per device, divide the total number of 9x9 multipliers by 8.

Source-Synchronous Differential I/O

Channels with DPA

Stratix GX devices include a full suite

of source-synchronous differential I/O

channels to complement the transceiver

blocks. To simplify timing issues for

high-speed parallel interfaces, Stratix GX

devices incorporate dedicated serializer/

deserializer (SERDES) and DPA circuitry

into the differential I/O channel. The DPA

circuitry in Stratix GX devices continuously removes timing variations introduced by unmatched board trace lengths,

jitter, and other skew-inducing effects.

Figure 1. Transceiver Channel Architecture

Serial-toParallel

Pattern

Detector &

Word Aligner

Clock

Recovery Unit

Reference

Clock

Rx PLL

Reference

Clock

Tx PLL

Parallelto-Serial

Stratix GX devices provide up to 45

receiver and 45 transmitter high-speed

differential I/O channels, each running at up to 1 Gbps, and

support LVDS, LVPECL, 3.3-V PCML, and HyperTransport

source-synchronous differential I/O standards. Stratix GX

devices can implement a wide array of high-speed interface

standards, including the 10 Gigabit Ethernet XSBI, SFI-4,

SPI-4 Phase 2 (POS-PHY Level 4), HyperTransport, RapidIO,

and CSIX streaming standards. Designers can use Altera® IP

cores to bridge the high-speed source-synchronous interface

and transceiver interface, as shown in Figure 2 on page 4.

Stratix GX devices also support various single-ended I/O

standards and can interface with advanced memory devices

including single data rate (SDR) SDRAM, double data rate

Altera Corporation

Recovered

Clock to

Programmable Logic

Rate Matcher

& Channel

Aligner

Synchronizer

8B/10B

Decoder

Receive

Transmit

8B/10B

Encoder

Synchronizer

(DDR) SDRAM, DDR FCRAM, zero-bus turnaround (ZBT)

SRAM, quad data rate (QDR) SRAM, and QDRII SRAM.

High-Performance Architecture

Stratix GX devices are built on the same innovative architecture and 1.5-V, 0.13-µm, all-layer-copper process as Stratix

devices, with densities ranging from 10,570 to 41,250 LEs.

The Stratix GX family offers up to 3.3 Mbits of embedded

RAM with its TriMatrix memory structure, which is optimized

for high memory bandwidth and large memory storage

requirements. Stratix GX devices include up to 14 DSP

blocks, ideal for implementing complex applications that

require high data processing throughput. Stratix GX devices

3

Table 3. Stratix GX Transceiver Applications

Protocol

Number of Channels

Channel Speed

10 Gigabit

Ethernet XAUI

4

3.125 Gbps

Gigabit Ethernet

1

1.25 Gbps

1, 4, or 12

2.5 Gbps

Fibre Channel

1

1.0625, 2.125 Gbps

Serial RapidIO

1 or 4

1.25, 2.5, 3.125 Gbps

SONET/SDH

Up to 16

2.488 Gbps

SFI-5

17 or 18

2.488 to 3.125 Gbps

SPI-5

17 or 18

2.488 to 3.125 Gbps

InfiniBand

PCI Express

16

2.5 Gbps

SMPTE 292M

1

1.485 Gbps

Up to 20

0.622 to 3.125 Gbps

Custom

also feature a complete clock management solution with a

hierarchical clock structure and up to eight PLLs, as well as

on-chip Terminator technology to reduce reflection, improve

signal integrity, and simplify board layout.

Altera SOPC Solutions

Successful transceiver applications require more than just a

transceiver on an FPGA. Altera delivers a complete design

platform that includes Stratix GX silicon, the industry-leading

Quartus® II software, pre-optimized IP—including the Nios®

embedded processor—and a comprehensive support infrastructure. Together with third-party synthesis and simulation

tools, system designers can design, test, and optimize complex

high-speed designs faster and easier than ever before.

Contact Altera Today

Figure 2. Stratix GX Implements Bridging Functions

SPI-4

Phase 2

Interface

XAUI

Backplane

Interface

The Stratix GX device family provides the ideal

solution for your 3.125-Gbps transceiver

applications. Visit the Altera web site today to

learn more about the Stratix GX device family

and its high-bandwidth I/O solutions at

www.altera.com/stratixgx.

8

Clk

Ctrl

Clk

3.125 Gbps

Transceivers

Ctrl

10-Gbps

Backplane IP

32

3.125 Gbps

3.125 Gbps

3.125 Gbps

To Backplane

Clk

Data

128

Custom Logic

Ctrl

Data

SPI-4 Phase 2

Interface Core

16

Source Synchronous

To Network Processor

& Other Functions

Data

®

The Programmable Solutions Company ®

Altera Offices

Altera Corporation

101 Innovation Drive

San Jose, CA 95134

USA

Tel: (408) 544-7000

www.altera.com

Altera U.K., Ltd.

Holmers Farm Way

High Wycombe,

Buckinghamshire

HP12 4XF

United Kingdom

Tel: (44) 1 494 602 000

Altera Japan, Ltd.

Shinjuku i-Land Tower 32F

6-5-1, Nishi-Shinjuku

Shinjuku-ku, Tokyo 163-1332

Japan

Tel: (81) 3 3340 9480

www.altera.co.jp

Altera International, Ltd.

2102 Tower 6

The Gateway, Harbour City

9 Canton Road

Tsimshatsui, Kowloon

Hong Kong

Tel: (852) 2945-7000

Copyright © 2002 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos

that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. HyperTransport is

a trademark of the HyperTransport Consortium. RapidIO is a trademark of the RapidIO Trade Association. All other trademarks are the property of their respective owners and may be registered in certain jurisdictions. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights.

GB-STXGX-1.0