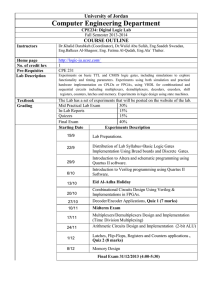

User’s Manual Digital Design and Implementation with Field Programmable Devices 1

advertisement

User’s Manual Digital Design and Implementation with Field Programmable Devices 1 1 Software on the CD In addition to “Quartus II Software Starter Suite” that is distributed by Altera, this CD contains the ModelSim Simulator and designs of the book, “Digital Design and Implementation with Field Programmable Devices”. 1.1 Quartus II Quartus II Web Edition is included on this CD. This software that is distributed by Altera is used for design entry, synthesis, post synthesis simulation and device programming. Install this software from the QUARTUS directory of this CD. License for running this software can be obtained from Altera by following instructions that appear later in this manual. 1.2 ModelSim ModelSim is full HDL simulator that is distributed by Mentor Graphics. ModelSim-Altera is customized for Altera to be used for Altera devices. Install this software from the MODELSIM directory of this CD. License for running this software can be obtained from Altera by following instructions that appear later in this manual. 1.3 Designs Complete files of all the designs discussed in the book are included in the DESIGNS subdirectory of this CD. The complete source code for these designs, their project definition, simulation run results and programming files are includes in this directory. In addition to designs of the book, several other designs are included in this subdirectory. 1.4 Licensing You need a network card and an NIC number to obtain a license for Quartus II and ModelSim. 2 On your PC enter the command mode and type ipconfig/all. This will display the Physical Address of your Ethernet Adapter that is the NIC required by Altera. The NIC number is this 12-digit hex number without the dashes. In the Altera site, (www.altera.com) click on Licensing and then click on MAX+PLUS II software for students & universities. This will bring you to http://www.altera.com/support/licensing/lic-university.html. In this window, select Quartus II Web Edition software for Verilog CBT Users, Version 1.1, and click on Continue. This will bring up a small window that requires you to enter your 12 digit NIC number and the Verilog CBT code from Page 7 of this manual. After entering this information, a license file and necessary instructions will be sent to you from Altera. A license file will be sent to you (license.dat) that contains license for Quartus II and ModelSim. Place this file in the flexlm directory of your C:\ drive and direct Quartus II and ModelSim to use this file for their licensing file. 3 2 Book Contents The focus of this book is on a practical knowledge of digital system design for programmable devices. The book covers all necessary topics under one cover, and covers each topic just enough that is actually used by an advanced digital designer. In the three parts of the book, we cover digital system design concepts, use of tools, and systematic design of digital systems. In the first chapter, design methodologies, use of simulation and synthesis tools and programming programmable devices are discussed. Based on this automated design methodology, the next four chapters present the necessary background for logic design, the Verilog language, programmable devices, and computer architectures. Presenting design and use of design tools based on the methodology discussed in the first part of the book becomes meaningful, only if a real industrial tool is used. For this purpose, the second part of the book presents design of small components using simulation, synthesis and design entry tools provided by Altera’s Quartus II design environment. While practicing design methodology of the first part of the book, this part familiarizes readers with the use of Quartus II integrated design environment. The third part of the book discusses RT level system design. A top-down systematic approach is presented for design of relatively complex systems. This part shows how a design is partitioned into its lower-level components, how synthesis tools or predefined parts are used for implementation of RT level components, and how a complete system is put together and used for programming a programmable device. The book can be used by hardware design practitioners who are already familiar with basics of logic design and want to move into the arena of automated design and design implementation using filed programmable devices. For this audience, this book provides a recap of digital design topics and computer architectures and shows the Verilog language for synthesis. In addition, for an industrial setting, the book shows how existing design components are used in upper level designs, and how user libraries are formed and utilized. Using Altera’s UP2 programmable device development board with this book helps engineers test and debug their designs before programming their programmable devices on production boards. In an educational setting, the book can be used as a complementary book for the basic logic design course, or a laboratory book for the sophomore logic design lab, or as a textbook for senior level design courses. Using Altera’s UP2 programmable device education board with this book helps students see their designs being implemented and tested, and thereby get a down-to-wire understanding of how things work. For students in other fields of engineering 4 like mechanical and chemical engineering, the book is a useful tool for design and implementation of controllers and interfaces. 2.1 1 Book Contents PLD Based Design ........................................................................................3 1.1 1.2 1.3 1.4 1.5 1.6 2 Logic Design Concepts................................................................................17 2.1 2.2 2.3 2.4 2.5 2.6 2.7 2.8 3 Read Only Memories ...................................................................... 105 Programmable Logic Arrays............................................................ 113 Complex Programmable Logic Devices ............................................ 122 Field Programmable Gate Arrays .................................................... 128 Summary....................................................................................... 137 Computer Architecture...............................................................................139 5.1 5.2 5.3 5.4 6 Design with Verilog .......................................................................... 59 Combinational Circuits .................................................................... 64 Sequential Circuits .......................................................................... 78 Writing Testbenches......................................................................... 97 Synthesis Issues ............................................................................ 102 Summary....................................................................................... 103 Programmable Logic Devices ....................................................................105 4.1 4.2 4.3 4.4 4.5 5 Number Systems.............................................................................. 17 Binary Arithmetic ............................................................................ 19 Basic Gates...................................................................................... 21 Designing Combinational Circuits .................................................... 26 Storage Elements ............................................................................. 39 Sequential Circuit Design................................................................. 45 Memories ......................................................................................... 56 Summary......................................................................................... 58 Verilog for Simulation and Synthesis ...........................................................59 3.1 3.2 3.3 3.4 3.5 3.6 4 Design Flow ....................................................................................... 3 Design Entry...................................................................................... 4 Simulation ......................................................................................... 8 Compilation ..................................................................................... 12 Device Programming ........................................................................ 14 Summary......................................................................................... 16 Computer System .......................................................................... 139 Computer Software ........................................................................ 141 CPU Design.................................................................................... 145 Summary....................................................................................... 158 Tools for Design and Prototyping...............................................................161 6.1 6.2 6.3 Design with Quartus II................................................................... 161 Hardware Description Language Based Design ............................... 173 UP2 Development Board ................................................................ 178 5 6.4 7 Gate Level Combinational Design .............................................................187 7.1 7.2 7.3 7.4 8 Element Design.............................................................................. 187 Iterative Structures ........................................................................ 190 Testing the Design ......................................................................... 197 Summary....................................................................................... 198 Designing Library Components..................................................................199 8.1 8.2 8.3 8.4 8.5 8.6 9 Summary....................................................................................... 185 Library Organization ...................................................................... 199 Switch Debouncing – Schematic Entry ........................................... 199 Single Pulser – Gate Level .............................................................. 205 Debouncing Two Pushbuttons – Using Completed Parts ................. 207 Hexadecimal Display – Using Verilog .............................................. 208 Summary....................................................................................... 212 Design Reuse ............................................................................................213 9.1 9.2 9.3 9.4 Design Description......................................................................... 213 Project Definition ........................................................................... 213 Design Implementation .................................................................. 214 Summary....................................................................................... 218 10 HDL Based Design ....................................................................................219 10.1 10.2 10.3 High Level Description and Simulation ........................................... 219 Design Implementation .................................................................. 222 Summary....................................................................................... 225 11 Sequential Multiplier ..................................................................................229 11.1 11.2 11.3 11.4 11.5 11.6 Sequential Multiplier Specification ................................................. 229 Shift-and-Add Multiplication .......................................................... 230 Sequential Multiplier Design .......................................................... 232 Multiplier Testing........................................................................... 239 Multiplier Prototyping .................................................................... 242 Summary....................................................................................... 245 12 VGA Adapter..............................................................................................247 12.1 12.2 12.3 12.4 VGA Driver Operation .................................................................... 247 Character Display .......................................................................... 251 UP2 Prototyping ............................................................................. 255 Summary....................................................................................... 258 13 Keyboard Interface ....................................................................................259 13.1 13.2 13.3 13.4 13.5 Data Transmission......................................................................... 259 Codes and Commands ................................................................... 262 Keyboard Interface Design.............................................................. 264 Keyboard Interface Prototyping....................................................... 267 Summary....................................................................................... 268 14 Design of SAYEH Processor .....................................................................269 6 14.1 14.2 14.3 14.4 14.5 14.6 CPU Description ............................................................................ 269 SAYEH Verilog Description............................................................. 274 SAYEH Testing............................................................................... 285 Sorting Test Program ..................................................................... 287 FPGA Programming........................................................................ 288 Summary....................................................................................... 288 The Verilog CBT Code is in the diagram of Page 47 of the book ☺ 7 3 Support The book, “Digital Design and Implementation with Field Programmable Devices” is published by Kluwer Academic Publishing. The Quartus II software provided with this book is supplied and supported by Altera. The ModelSim software is provided by Mentor Graphics through Altera. Software updates will be announced by Altera and you will be informed of the changes. You will be entered in their mailing list when registering your software. For the design projects and contents of the DESIGNS directory, please contact the author if you find bugs or you have updates. If there are designs you wish to contribute and share with others, please generate a short document of your design and send to the author at navabi@ece.neu.edu. The UP2 board is supported by Altera. The university support email of Altera is: university@altera.com. Please contact them for issues related to UP2. 8