Telecommunication Engineering M.S.RAMAIAH INSTITUTE OF TECHNOLOGY Department

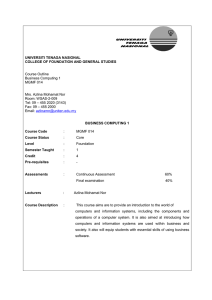

advertisement