p Metal-insulator-semiconductor structures on -type GaAs with low interface state density

advertisement

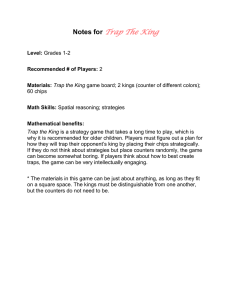

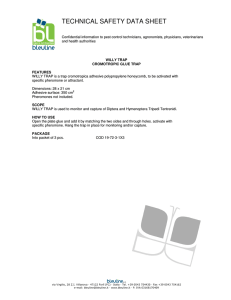

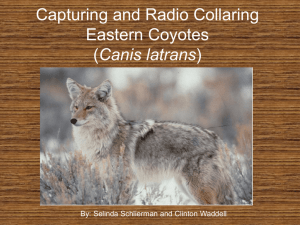

Metal-insulator-semiconductor structures on p -type GaAs with low interface state density Zhi Chen, Dae-Gyu Park, Francke Stengal, S. Noor Mohammad, and Hadis Morkoça) Coordinated Science Laboratory and Materials Research Laboratory, University of Illinois at Urbana— Champaign, 1101 West Springfield Avenue, Urbana, Illinois 61801 ~Received 18 January 1996; accepted for publication 6 May 1996! Interfacial properties of in situ deposited Si3 N4 /Si/p-GaAs metal-insulator-semiconductor structures have been investigated. Conductance loss measurements show that a minimum interface trap density as low as 5.531010 cm21 eV21 has been achieved on p-type GaAs by using a high quality strained Si interlayer. The quasistatic and high-frequency capacitance-voltage measurements as well as the theoretical high-frequency capacitance-voltage calculation clearly demonstrate the accumulation, depletion, and inversion regions. The interface trap density as a function of the band-gap energy near the midgap has been determined with the conductance method. The reduced band bending ~0.84 V! may be mainly caused by the narrower band gap of the strained Si interlayer. © 1996 American Institute of Physics. @S0003-6951~96!04828-0# Despite many advantages offered by a low gate leakage technology in GaAs, such as metal insulator structures, functional GaAs metal-insulator-semiconductor field-effect transistors ~MISFET! has not yet been realized. The critical task in developing the MISFET devices is to obtain a nearly ideal interface between the insulator and GaAs. Efforts have been made to improve the interface between the insulator and GaAs for decades without much success. In recent years, two approaches have been found to be effective in passivating the surface of GaAs. One is to incorporate a thin Si interlayer ~;10 Å! in the interface between the insulator and GaAs,1–3 and the other one is the surface treatment using sulfides.4–6 The sulfide passivation only provides us with a limited improvement with the interface trap density of ;531012 cm22 eV21 .6 On the other hand, the interface passivation using a thin Si interlayer has demonstrated a significant improvement with reported interface trap densities in the upper 1010 cm22 eV21 .7–9 In addition, Huang et al.10 passivated the ~110! GaAs surface using an approach which combines the above two methods, i.e., the sulfide treatment and the subsequent Si interlayer growth, and obtained an interface trap density of 131012 cm22 eV21 . However, all of the above attempts utilizing the thin Si interlayer are based on the n-type GaAs. The high quality MIS structures on p-type GaAs, which are crucial for the demonstration and development of the inversion or the enhancement mode MISFETs, have not yet been realized. In this letter, we report the first successful fabrication of p-type MIS capacitors obtained through the use of in situ deposited Si3 N4 /Si/p-GaAs. The results from these devices clearly demonstrate the accumulation, depletion, and inversion regions with a minimum trap density of 5.531010 cm22 eV21 determined by the conductance method. The Si and dielectric depositions were carried out in an electron cyclotron resonance ~ECR! enhanced remote plasma chemical vapor deposition ~CVD! chamber connected with a molecular beam epitaxy ~MBE! chamber through a transfer a! On sabbatical at Wright Laboratory, Wright-Patterson AFB, OH 45433, under a University Resident Research Program funded by AFOSR. tube maintained at 231029 Torr. Both chambers were maintained at the ultrahigh vacuum ~UHV! ~;1029 Torr! prior to the growth. First, p-GaAs with a doping level of 331016 cm23 was grown by MBE on an ~100! p 1 -GaAs substrate. The sample was then transferred to the CVD chamber through the UHV transfer tube without exposing it to any oxygen and other contaminants. In the CVD chamber, an appropriate amount of SiH4 and He were introduced when the substrate temperature reached 350 °C. 10 Å Si layer was then grown on the as-grown p-GaAs at a plasma power of 60 W. A 200-Å-thick Si3 N4 layer was subsequently deposited at 250 W and 350 °C. No in situ annealing was performed before the Si3 N4 growth. After growth, the sample was annealed by rapid thermal annealing ~RTA! at 550 °C for 30 s. Finally, a 1200-Å-thick aluminum was thermally evaporated on the top of the sample and patterned by photolithography to form the metal-insulator-semiconductor capacitors with a diameter of 300 mm. The high-frequency capacitancevoltage (C – V) measurements were carried out on HP 4284A Precision LCR meter, and the quasistatic C – V measurements were performed on HP 4140B pA meter/dc voltage source with a ramp rate of 50 mV/s scanned from the positive to the negative bias. Figure 1 shows the measured C – V characteristics of the MIS capacitors ~Si3 N4 /Si/p-GaAs! and the theoretically calculated high-frequency capacitance-voltage ~HFCV! curve (Si3 N4 /p-GaAs!. The theoretical HFCV was calculated using the approach described in Ref. 12. There are several outstanding features to be noted. First, the quasistatic C – V ~QSCV! curve dips significantly, indicative of a good interface between the insulator and p-GaAs. The theoretical HFCV is almost coincident with the experimental HFCV, indicating that the capacitor is not in deep depletion. Inversion is clearly demonstrated by the QSCV curve. The maximum frequency dispersion of 120 mV and a hysteresis of 70 mV are demonstrated by the 1 MHz and 1 kHz curves. These results are comparable with those on the n-type GaAs reported in Ref. 9 and much better than those on n-type GaAs reported in Ref. 11. The 100 Hz curve ~not shown here! is located almost at the same position of the 1 kHz curve, and 230 Appl. Phys. Lett. 69 (2), 8 July 1996 0003-6951/96/69(2)/230/3/$10.00 © 1996 American Institute of Physics Downloaded¬20¬May¬2009¬to¬128.163.42.33.¬Redistribution¬subject¬to¬AIP¬license¬or¬copyright;¬see¬http://apl.aip.org/apl/copyright.jsp FIG. 2. Dependence of G m / v on v at various gate voltages. FIG. 1. Capacitance-voltage measurements of a Si3 N4 /Si/p-GaAs metalinsulator-semiconductor capacitors at 1 MHz, 1 kHz, and quasistatic state. The theoretically calculated high-frequency capacitance-voltage ~HFCV! curve. The thickness of the Si3 N4 is 200 Å and the area of the capacitor is 731024 cm2 . the QSCV is very close to the high-frequency C – V curves in the accumulation and depletion ~prior to inversion! regimes, suggesting a low density of slow states. The discrepancy of the oxide capacitance in accumulation and inversion regions is caused by the longer minority-carrier response time in GaAs than in Si. The minority-carrier response time t r }1/n i . 12,15 For GaAs, n i is small. This leads to a larger t r . Thus even in quasistatic condition, the minority carriers may not fully respond to the signal. This causes the discrepancy of the oxide capacitance in accumulation and in inversion. Another evidence is that, at 20 Hz, the CV curve looks like the HFCV curve. The minority carriers in GaAs do not respond to the signal at 20 Hz, while those in Si do respond to it at 20 Hz. According to Sze,13 the ideal flat-band voltage ~without fixed charges in the insulator! for p-GaAs is 21.32 V. Our experimental curve shifts 10.77 V, corresponding to a negative charge density of 1.631012 cm22 in the insulator. It is important to extract the interface trap density accurately and adequately. Basically, there are two established approaches for such deduction, i.e., the low-high-frequency capacitance method and the conductance method.12 The conductance method is much more accurate and sensitive in extracting the interface trap density for low densities. For the capacitance method, the minimum detectable interface trap density is 331010 cm22 eV21 for a doping level of 1 31016 cm23 , and for the conductance method, it is possible to detect the interface trap densities at least a decade lower independent of the doping level.12 This suggests that the conductance method is a more reliable one especially when the interface trap density reaches the 1010 cm22 eV21 range. In order to accurately extract the interface trap density, a distribution of the interface trap levels should be considered. The equivalent parallel capacitance C p and conductance G p are given by12 C it tan21 ~ v t p ! , vtp ~1! C it Gp 5 ln@ 11 ~ v t p ! 2 # , v 2vtp ~2! C p 5C D 1 where C D is the capacitance in depletion, C it is the interface trap capacitance, t p is the interface trap response time, and v is the angular frequency. However, the measured conductance G m and the measured capacitance C m are not equal to the equivalent conductance G p and capacitance C p . The influence of the insulator capacitance C N should be eliminated to obtain the real parallel conductance G p as given by12 v C 2N G m Gp 5 2 , v G m 1 v 2 ~ C N 2C m ! 2 ~3! where C N is equal to the capacitance in strong accumulation. In the frequency and gate voltage range which we are interested in, v (C N 2C m )@G m and Eq. ~3! can be further reduced to S CN Gp 5 v C N 2C m D 2 Gm . v ~4! Since the insulator capacitance can be determined in accumulation, the real parallel conductance G p can be obtained from the measured conductance G m using Eq. ~4!. Another factor which influences the accuracy of the calculation is the series resistance of the bulk. However, because our sample is grown on a p 1 substrate, this series resistance is very small and it is non consequential. Figure 2 shows the dependence of G m / v on v at various gate voltages, which can be well described by Eqs. ~2! and ~4!. From Eq. ~2!, the interface trap density can be calculated at the peaks of the curves of G p / v vs v plots ~not from the peaks of the plot of G p / v vs V G !, using the following relation12: Gp 50.4qAD it , v ~5! Appl. Phys. Lett., Vol. 69, No. 2, 8 July 1996 Chen et al. 231 Downloaded¬20¬May¬2009¬to¬128.163.42.33.¬Redistribution¬subject¬to¬AIP¬license¬or¬copyright;¬see¬http://apl.aip.org/apl/copyright.jsp FIG. 3. Interface trap density vs band-gap energy near the midgap, determined by the conductance measurements from the Si3 N4 /Si/ p-GaAs capacitors. where D it is the interface trap density and A is the area of the capacitor. From Fig. 2, the peak value of G m / v at 0.05 V is 1.61 pF, which leads to a minimum interface trap density of 5.531010 cm22 eV21 calculated using Eqs. ~4! and ~5!. This is the lowest interface trap density on p-GaAs ever reported. The minimum interface trap density on n GaAs calculated from the conductance measurements in Ref. 11 is 131011 cm22 eV21 . Note that the value reported in Ref. 11 is 331010 cm22 eV21 obtained by the low-frequency capacitance method which, as mentioned earlier, is not a very accurate method at these low interface state densities. Figure 3 shows the interface trap density distribution over the band-gap energy near the midgap. This is derived from the conductance measurements in Fig. 2. ~The interface trap density near the midgap can be accurately extracted by the conductance method.! From Fig. 3, it can be seen that the interface trap density increases as the Fermi level moves toward the valence-band edge. However, it is obvious that the very low interface trap density is indeed available near the midgap. In order to evaluate the quality of the interface in the whole band gap, the total band bending is calculated by integrating the QSCV curve from accumulation to inversion: DC s 5 E S inv Vg accu Vg 12 D C LF dV, CN ~6! where C LF is the QS capacitance, and C N is the capacitance of the insulator. From the measured QSCV curve, we obtained the total band bending DC s of 0.84 V, which is substantially smaller than the band gap potential of GaAs ~1.42 V!. This smaller band bending, on one hand, may be due to the higher interface trap density near the bandage. From our experimental results of Si3 N4 /Si and SiO2 /Si MIS capacitors with the interface trap density less than 231010 cm22 eV21 in the midgap, we found that the band bending of Si3 N4 /Si interface is only 0.81 V, while that of SiO2 /Si is 1.06 V. This indicates that the interface of Si3 N4 /Si near the bandage is not as good as that of the SiO2 /Si. On the other hand, the reduced band bending may be caused by the strained Si interlayer. Recently, we calculated the band structure of the strained Si layer using the empirical pseudopotential method and proposed a band structure for the Si/GaAs heterostructure.14 The band gap of the strained Si interlayer is 0.7 eV. The conduction band offset DE c is 0.33 eV and the valence-band offset DE v is 0.39 eV. For the Si3 N4 /Si/GaAs structure, a quantum well forms. There is a confined energy level in the Si conduction band and another one in the valence band. Therefore, the actual gap of the two energy levels should be larger than 0.7 eV, but smaller than 1.42 eV. ~This problem is under investigation and the detailed results will be published elsewhere.! This reduced band bending may be the reflection of the quantum size effect. If the later case is true, the accumulation and inversion may be achieved on the strained Si layer, which may have a significant influence on the MISFET devices. The real situation would be understood only if the inversion mode MISFETs are fabricated. In summary, the MIS structure on p-GaAs with a minimum interface trap density of 5.531010 cm22 eV21 near the midgap has been obtained by using a high quality strained Si interlayer. The quasistatic and high-frequency C – V measurements together with the theoretical HFCV data indicate that the accumulation and inversion have been achieved. The reduced band bending ~0.84 V! may be mainly caused by the narrower band gap of the strained Si interlayer. This research is supported by Air Force Office of Scientific Research through Contract No. F49620-95-1-0298, Department of Energy through Contract No. DEFG02-96ER45439, and National Science Foundation through Contract No. NSF DMR 93-12422. The authors are grateful to A. E. Botchkarev, M. Tao, A. Salvador, and D. Jeffers for their assistance. 1 G. G. Fountain, S. V. Hattangady, D. J. Vitkavage, R. A. Rudder, and M. J. Markunas, Electron. Lett. 24, 1134 ~1988!. 2 S. Tiwari, S. L. Wright, and J. Battey, IEEE Electron Device Lett. 9, 488 ~1988!. 3 J. L. Freeouf, D. A. Buchanan, S. L. Wright, T. N. Jackson, and B. Robinson, Appl. Phys. Lett. 57, 1919 ~1990!. 4 E. Yablonovitch, C. J. Sandroff, R. Bhat, and T. Gmitter, Appl. Phys. Lett. 51, 439 ~1987!. 5 C. J. Sandroff, R. N. Nottenburg, J. C. Bischoff, and R. Bhat, Appl. Phys. Lett. 51, 33 ~1987!. 6 Z. Chen, W. Kim, A. Salvador, S. N. Mohammad, Ö. Aktas, and H. Morkoç, J. Appl. Phys. 78, 3920 ~1995!. 7 D. S. L. Mui, H. Liaw, A. L. Demirel, S. Strite, and H. Morkoç, Appl. Phys. Lett. 59, 2847 ~1991!. 8 Z. Wang, D. S. L. Mui, A. L. Demirel, D. Biswas, J. Reed, and H. Morkoç, Appl. Phys. Lett. 61, 1826 ~1992!. 9 M. Tao, A. E. Botchkarev, D. G. Park, J. Reed, S. J. Chey, J. E. Van Nostrand, D. G. Cahill, and H. Morkoç, J. Appl. Phys. 77, 4113 ~1995!. 10 L. J. Huang, W. M. Lau, S. Ingrey, D. Landheer, and J.-P. Nöel, J. Appl. Phys. 76, 8192 ~1994!. 11 Z. Wang, M. E. Lin, B. Mazhari, N. Teraguchi, Z. Fan, X. Gui, and H. Morkoç, Appl. Phys. Lett. 62, 2977 ~1993!. 12 E. H. Nicollian and J. R. Brews, MOS Physics and Technology ~Wiley, New York, 1982!. 13 S. M. Sze, Physics of Semiconductor Devices ~Wiley, New York, 1981!. 14 Z. Chen, S. N. Mohammad, and H. Morkoç, Phys. Rev. B 53, 3879 ~1996!. 15 S. C. Witczak, J. S. Suehle, and M. Gaitan, Solid-State Electron. 35, 345 ~1992!. 232 Appl. Phys. Lett., Vol. 69, No. 2, 8 July 1996 Chen et al. Downloaded¬20¬May¬2009¬to¬128.163.42.33.¬Redistribution¬subject¬to¬AIP¬license¬or¬copyright;¬see¬http://apl.aip.org/apl/copyright.jsp