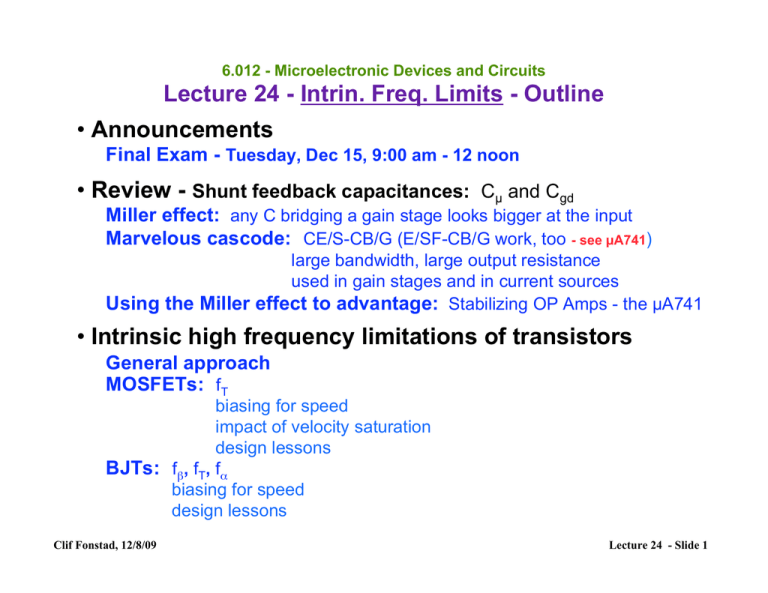

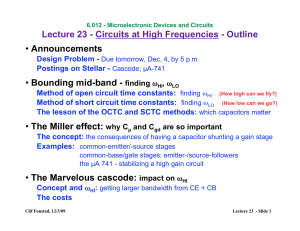

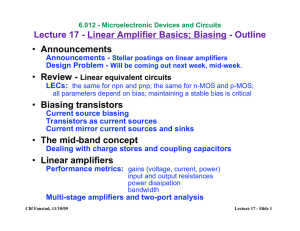

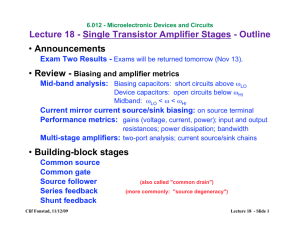

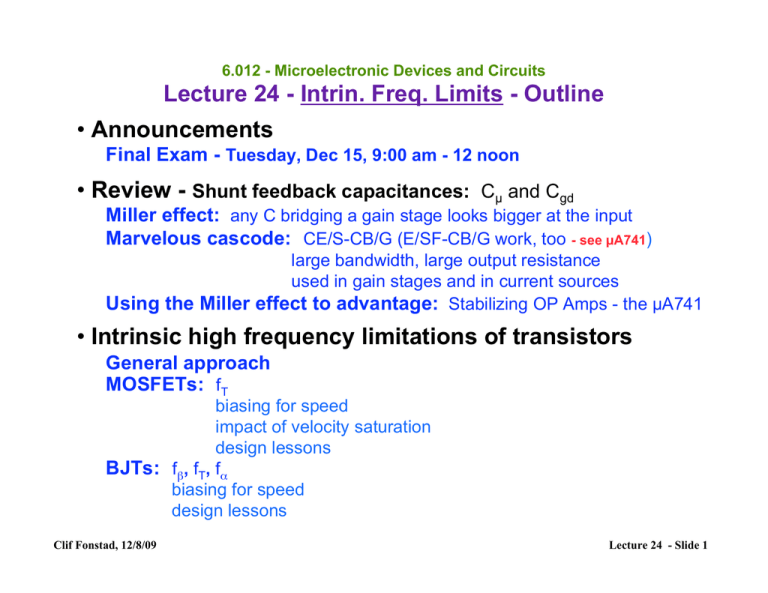

6.012 - Microelectronic Devices and Circuits

Lecture 24 - Intrin. Freq. Limits - Outline

• Announcements

Final Exam - Tuesday, Dec 15, 9:00 am - 12 noon

• Review - Shunt feedback capacitances: Cµ and Cgd

Miller effect: any C bridging a gain stage looks bigger at the input

Marvelous cascode: CE/S-CB/G (E/SF-CB/G work, too - see µA741)

large bandwidth, large output resistance

used in gain stages and in current sources

Using the Miller effect to advantage: Stabilizing OP Amps - the µA741

• Intrinsic high frequency limitations of transistors

General approach

MOSFETs: fT

biasing for speed

impact of velocity saturation

design lessons

BJTs: fβ, fT, fα

biasing for speed

design lessons

Clif Fonstad, 12/8/09

Lecture 24 - Slide 1

Summary of OCTC and SCTC results

log |A

vd |

Mid-band Range

!LO

!b

!a !d

!c

!LO *

!HI * !HI

!4

log !

!5 !2!1 !3

• OCTC:

1.

2.

3.

an estimate for ωHI

ωHI* is a weighted sum of ω's associated with device capacitances:

(add RC's and invert)

Smallest ω (largest RC) dominates ωHI*

Provides a lower bound on ωHI

• SCTC:

1.

2.

3.

an estimate for ωLO

ωLO* is a weighted sum of w's associated with bias capacitors:

(add ω's directly)

Largest ω (smallest RC) dominates ωLO*

Provides a upper bound on ωLO

Clif Fonstad, 12/8/09

Lecture 24 - Slide 2

The Miller effect (general)

Consider an amplifier shunted by a capacitor, and consider

how the capacitor looks at the input and output terminals:

Cm

+

vin

-

Av

iin = Cm

+

!vin

-

+

vout

d [(1" Av )v in ]

dt

(1-Av)Cm

Cin looks much

bigger than Cm

(1-Av)vin

iin +

+

+

vin Cm vout = A vvin

= (1" Av )Cm

Cm

dv in

dt

Note: Av is negative

+

vout

-

Cm

(1" Av )

Av

# Cm

Cout looks like Cm

Clif Fonstad, 12/8/09

Lecture 24 - Slide 3

!

The cascode when the substrate is grounded:

High frequency issues:

L.E.C. of cascode: can't use equivalent transistor idea here

because it didn't address the issue of the C's!

ro2

Cgd1

g1

+

vgs1

gm1vgs1

s1,b1,b2

Cgs1

ro1

Voltage gain ≈ -1 so

minimal Miller effect.

d2

+

d1,s2,b2

-

(gm2+gmb2 )vgs2

Cgd2 +Cbd2

Cdb1 +Cgs2 +Cbs2

vgs2

+

s1,b1,g2,b2

vout

rl

g2,b2

Voltage gain ≈ gmrl,

without Miller effect.

Common-source gain without the Miller effect penalty!

Clif Fonstad, 12/8/09

Lecture 24 - Slide 4

Multi-stage amplifier analysis and design: The µA741

Figuring the circuit out:

Emitter-follower/

common-base "cascode"

differential gain stage

EF

CB

The full schematic

© Source unknown. All rights reserved.

This content is excluded from our Creative Commons license.

For more information, see http://ocw.mit.edu/fairuse .

Current mirror load

Push-pull

output

Simplified schematic

Darlington commonemitter gain stage

Clif Fonstad, 12/8/09

© Source unknown. All rights reserved.

This content is excluded from our Creative Commons license.

For more information, see http://ocw.mit.edu/fairuse.

Lecture 24 - Slide 5

Multi-stage amplifier analysis and design: Understanding the µA741

input "cascode"

Begin with the BJT building-block stages:

i

s in

iout

+

iin

! go /!

v in

!(gm+g! )

g,b

rt

iout

+

+

vt

-

v out

-

b

iin

+

v in

e

b

Clif Fonstad, 12/8/09

+

v!

-

gmv !

g!

+

v out

g,b

iout

c

go

+

v out

-

Common emitter

iin

+

v in

c

Common base

d

r" +

!/gl

+

-

v in

iout

gsl +

!/(rt +r! )

Emitter follower

iin

+

v in

-

rl = 1/gl

e

e

+

v out

c

Relative sizes:

gm: large

gπ: medium

go: small

gt, gl: cannot

generalize

Lecture 24 - Slide 6

Multi-stage amplifier analysis and design: Two-port models

Two different "cascode" configurations, this time bipolar:

rt

iout

b

iin

+ +

v out v in

- -

+

vt

-

iout

+

v!

-

e

rt

iout

b

iin

+

+

v out v in

- -

+

vt

-

e

rt

iout

b

gmv !

g!

+

+

vt

-

+

v out v in

- c

Clif Fonstad, 12/8/09

c

go

Common emitter

iin

r" +

!/gl

+

-

!v in

iout

! !/(rt +r! )

Emitter follower

go

Common emitter

iout

+

v!

-

gmv !

g!

s

+

+

v out v in

-

e

g,b

e

s

!(gm+g! )

iin

g,b

d

! go /!

+ +

v out v in

Common base

!(gm+g! )

iin

iout

-

iin

+

+

v out v in

-

rl = 1/gl

e

iin

+ +

v outv in

- -

c

iin

c

iin

Common base

rl = 1/gl

-

g,b

iin

iout

d

! go /!

+ +

v out v in

-

rl = 1/gl

-

g,b

In a bipolar cascode, starting with an emitter follower still reduces the

gain, but it also gives twice the input resistance, which is helpful.

Lecture 24 - Slide 7

Multi-stage amplifier analysis and design: MOSFET 2-port models

Reviewing our building-block stages:

iin

s

+

v in

g,b

rt

iout

g

+

+

vt

-

v out

-

(gm+

g o gt

gmb )v in gm+gmb +gt

Common gate

iin

iout

s,g

Common source

iin

d

d

go

gm+go +gl

Source follower

+

v out

-

iin

+

v in

-

rl = 1/gl

s,g

iout

gmv in

-

g,b

gmv in

+

v in

-

d

+

v out

+

v in

g

Clif Fonstad, 12/8/09

gm+

gmb

iout

s,b

+

v out

-

Relative sizes:

gm, gmb: large

go: small

gt, gl: cannot

generalize

d

Lecture 24 - Slide 8

Multi-stage amplifier analysis and design: Two-port models

Two different "cascode" configurations:

rt

+

vt

-

rt

+

vt

-

rt

+

vt

-

iout

g

iout

g

iin

iout

+ +

v outv in

- -

gmv in

s,g

Common source

iin

s,g

Common source

iin

+ +

v outv in

- d

d s

iout

gmv in

g

go

gm+go +gl

Source follower

s,b s

-

iin

++

vvoutin

- -

iout

gm+

gmb

(gm+

g o gt

gmb )v in gm+gmb +gt

Common gate

d g,b

iin

- -

d

iin

+ +

v out

v in

(gm+

g o gt

gmb )v in gm+gmb +gt

Common gate

rl = 1/gl

g,b

iout

gm+

gmb

d

+ +

v out

v in

iin

++

vvoutin

- -

rl = 1/gl

s,g

s,gg,b

iout

gmv in

go

iin

+ +

v outv in

-

+ +

v outv in

- -

iout

d

rl = 1/gl

- -

g,b

With MOSFETs, starting a cascode with a source follower costs a factor of two in gain

because rout for an SF is small, so it isn't very attractive.

Clif Fonstad, 12/8/09

Lecture 24 - Slide 9

Multi-stage amplifier analysis and design: The µA741

The circuit: a full schematic

C1 is in

a Miller

position

across

Q16

Clif Fonstad, 12/8/09

The monolithic capacitor made the µA741

"complete" and a big success. Why is it

needed? What does it do?

© Source unknown. All rights reserved.

This content is excluded from our Creative Commons license.

For more information, see http://ocw.mit.edu/fairuse.

Lecture 24 - Slide 10

Multi-stage amplifier analysis and design: The µA741

Why is there a capacitor in the circuit?: the added capacitor

introduces a low

frequency pole

that stabilizes

the circuit.

Without it the gain

is still greater than 1

when the phase shift

exceeds 180˚ (dashed

curve). This can result

in positive feedback

and instability.

Clif Fonstad, 12/8/09

Low

frequency

pole

With it the gain

is less than 1 by

the time the phase

shift exceeds 180˚

(solid curve).

Lecture 24 - Slide 11

Intrinsic performance - the best we can do

We've focused on ωHI, the upper limit of mid-band, but even when ω > ωHI

the |Av| > 1, and the circuit is useful. For example, for the common

source stage we had

#gt ( gm # j"Cgd )

Av ( j" ) =

2

( j" ) CgsCgd + j" [(gl + go )Cgs + ( gl + go + gt + gm )Cgd ] + ( gl + go ) gt

{

}

log |Av,oc |

gm /(g l +go )

!

A Bode plot of

Av is shown

to the right:

log !

1

!1

!2 !3

!1 gm /(gl +go )

When we look for a metric to compare the ultimate

performance limits of transistors, we make note of

this and ask how high can a device in isolation have

provide voltage or current gain?

Clif Fonstad, 12/8/09

Lecture 24 - Slide 12

Intrinsic performance - the best we can do, cont.

Consider the two possibilities shown below, one for a voltage input and

output where the metric would be the open circuit voltage gain, Av,oc,

and the other for a current input and output with the metric being the

short circuit current gain, Ai,sc (commonly written βsc):

Cgd

g

+

Cgs

v gs

-

+

v in

-

s,b

g

iin

+

Cgs

v gs

s,b

d

go

gmv gs

+

v out

-

gm $ j#Cgd

v out ( j# )

Av,oc ( s) "

= $

v in ( j# )

go $ j#Cgd

s,b

Cgd

d

!

gmv gs

go

iout

" sc ( j# ) $

gm % j#Cgd

id ( j# )

=

ig ( j# )

j# (Cgs + Cgd )

s,b

Of these two alternatives, βsc is the more useful. Av,oc is derived with a

! something that doesn't give a meanvoltage source driving a capacitor,

ingful result and leads to ever increasing input power. It also does not

involve gm and Cgs. Consequently, short circuit current gain is used as

the intrinsic high frequency performance metric for transistors.

Clif Fonstad, 12/8/09

Lecture 24 - Slide 13

Intrinsic ωHI's for MOSFETs - short-circuit current gain

Cgd

g

+

Cgs

v gs

ig

d

gmv gs

id

go

s

s

The common-source short-circuit current gain is:

" sc ( j# ) $

gm % j#Cgd

id ( j# )

=

ig ( j# )

j# (Cgs + Cgd )

there is one pole at ω = 0, and one zero, ωz:

"z =

!

gm

Cgd

The short circuit current gain, βsc, is infinite at DC (ω = 0) , and

its magnitude decreases linearly with increasing frequency.

!

Clif Fonstad, 12/8/09

Lecture 24 - Slide 14

Intrinsic ωHI's for MOSFETs - short-circuit current gain, cont.

Cgd

g

d

+

Cgs

v gs

ig

id

go

gmv gs

s

s

The magnitude of βsc decreases with ω, but it is still greater

than one for a wide range of frequencies.

" sc ( j# ) =

2

gm2 + # 2Cgd

# 2 (Cgs + Cgd )

2

The transistor is useful until |βsc| is less than one. The

frequency at!which this occurs is called ωt. Setting = 1 and

solving for ωt yields:

2

"t =

Clif Fonstad, 12/8/09

[

gm

(Cgs + Cgd ) # Cgd2

2

]

$

gm

(Cgs + Cgd )

Lecture 24 - Slide 15

!

MOSFET short-circuit current gain, βsc(jω), cont.

Note: ωz > ωt

log |" sc |

Low frequency value:

infinity

Zero, ωz :

ωz = gm/Cgd

!z

log !

!t

No 3dB point, ωb.

Unity gain point, ωt :

Clif Fonstad, 12/8/09

ωt @ gm/(Cgs+Cgd)

Lecture 24 - Slide 16

MOSFET short-circuit current gain, βsc(jω), cont.

Can we bias to maximize ωt?

log |" sc |

" t (MOSFET) =

gm

g

# m

(Cgs + Cgd ) Cgs

W

*

µCh Cox

VGS $ VT

L

=

2

*

W L Cox

3

3 µCh VGS $ VT

=

2

L2

Maximize VGS.

!

!z

log !

!t

What is the ultimate limit?

" t (MOSFET) =

VDS

3 µCh VGS # VT

3

3

3 sCh

1

=

µ

=

µ

E

=

=

Ch

Ch Ch

2

L2

2L

L

2L

2 L

$ Ch

Channel

transit

time!

Lessons: Bias at well above VT; make L small, use n-channel.

Clif Fonstad, 12/8/09

!

Lecture 24 - Slide 17

An aside: looking back at CMOS gate delays

CMOS: switching speed; minimum cycle time (from Lec. 15)

Gate delay/minimum cycle time:

For MOSFETs operating in strong inversion, no velocity saturation:

" Min Cycle

12nL2minVDD

=

2

µe [VDD # VTn ]

Comparing this to the channel transit time:

!

" Ch Transit =

Lmin

Lmin

Lmin

=

=

se,Ch

µe #Ch

µe (VDD $ VTn ) Lmin

We see that the cycle time is a multiple of the transit time:

!

" Min Cycle =

12nVDD

" Channel Transit = n' " Channel Transit

(VDD # VTn )

When velocity saturation dominated, we found the same thing:

!" Min.Cycle #

Clif Fonstad, 12/8/09

LminVDD

= n' " ChanTransit

ssat [VDD $ VTn ]

where

" ChanTransit

L

=

ssat

Lecture 24 - Slide 18

Intrinsic ωHI's for MOSFETs - βsc(jω) and ωt w. velocity saturation

What about the intrinsic ωHI of a MOSFET operating with full

velocity saturation?

The basic result is unchanged; we still have:

"t =

[

gm2

(Cgs + Cgd ) # Cgd2

2

]

$

gm

g

$ m

(Cgs + Cgd ) Cgs

However, now gm is different:

*

gm = W ssat Cox

! this we have:

With

*

gm

W ssat Cox

ssat

1

"t #

=

=

=

*

W L Cox

L

$ Ch

! Cgs

In the case where velocity saturation dominates, we once again find

that it is the channel transit time that is the ultimate limit.

!

Do you care to speculate on the intrinsic ωHI of a BJT?

Clif Fonstad, 12/8/09

Lecture 24 - Slide 19

Intrinsic ωHI's for BJTs - short-circuit current gain

Cµ

b

+

v!

ib

C!

g!

c

gmv !

ic

go

e

e

The common-emitter short-circuit current gain is:

" sc ( j# ) $

gm % j#Cµ

ic ( j# )

=

ib ( j# )

g& + j# (C& + Cµ )

[

]

there is one pole, call it ωp, and one zero, ωz:

!

"p =

g#

,

(C# + Cµ )

"z =

gm

Cµ

Of these two, ωp is much smaller and this is the 3dB point of

the common-emitter short-circuit current gain. We give it the

g$

name ωβ: !

" =

#

Clif Fonstad, 12/8/09

(C

$

+ Cµ )

Lecture 24 - Slide 20

Intrinsic ωHI's for BJTs - short-circuit current gain, cont.

Cµ

b

+

v!

ib

c

C!

g!

gmv !

ic

go

e

e

The magnitude of βsc decreases above ωb, but it is still

greater than one initially:

" sc ( j# ) =

[

gm2 + # 2Cµ2

g$2 + # 2 (C$ + Cµ )

2

]

The transistor is useful until |βsc| is less than one. The

frequency at! which this occurs is called ωt. Setting = 1 and

solving for ωt yields:

2

2

"t =

Clif Fonstad, 12/8/09

[

(g

#

+ gm )

(C# + Cµ ) $ Cµ2

2

]

%

gm

(C# + Cµ )

Lecture 24 - Slide 21

!

BJT short-circuit current gain, βsc(jω), cont.

Note: ωz > ωt >> ωβ (= ωt /βF)

log |" sc |

Low frequency value: βF

"F

Zero, ωz : ωz = gm/Cµ

!z

log !

!t

!"

3dB point, ωb: ωb = gπ/(Cπ+Cµ)

Unity gain point, ωt : ωt @ gm/(Cπ+Cµ)

Clif Fonstad, 12/8/09

Lecture 24 - Slide 22

BJT short-circuit current gain, βsc(jω), cont.

log |" sc |

Can we bias to maximize ωt?

"t #

"F

qIC

kT

gm

=

C

+

C

( $ µ ) ,.%' qIC (*+ b + Ceb,dp + Ccb,dp /1

-& kT )

0

Maximize IC.

Used C$ = gm + b + Ceb,dp

!z

!"

!

log !

!t

In the limit of large IC: limI C "# $ t %

Base

transit

time

2Dmin,B

2µmin,BVthermal

1

=

=

&b

w B2

w B2

Base transit time

Lessons: Bias at large IC; make wB small, use npn.

Clif Fonstad, 12/8/09

!

Lecture 24 - Slide 23

6.012 - Microelectronic Devices and Circuits

Lecture 24 - Intrinsic Limits of Transistor Speed - Summary

• Intrinsic high frequency limits for transistors

General approach: short-circuit current gains

• Limits for MOSFETs:

Metric - CS short-circuit current unity gain pt: ωT = gm/[(Cgs+Cgd)2 -Cgd2]1/2

ωT is approximately gm/Cgs = 3µe(VGS-VT)/2L2

gm = (W/L)µeCox*(VGS-VT) and Cgs = (2/3)WLCox

*

so ωT ≈ 3µe(VGS-VT)/2L2 = 1/τch

Design lessons: bias at large ID

minimize L (win as L2; as L in velocity saturation)

use n-channel rather than p-channel (µe >> µh)

• Limits for BJTs:

Metrics - CE short-circuit current gain 3B pt: ωb = gp/(Cπ + Cµ)

CE short-circuit current gain unit gain pt: ωT = gm/(Cπ + Cµ)

ωT approaches 1/τb as Ic increases and τb = wB2/2Dmin,B

so ωT ≈ 2Dmin,B/wB2 = 2µeVt/wB2 = 1/τb

CB short-circuit current gain unit gain pt: ωα = gm/Cπ

Design lessons: bias at high collector current

minimize wB (win as wB2)

use npn rather than pnp

(µe >> µh)

Clif Fonstad, 12/8/09

Lecture 24 - Slide 24

MIT OpenCourseWare

http://ocw.mit.edu

6.012 Microelectronic Devices and Circuits

Fall 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.