Document 13578648

advertisement

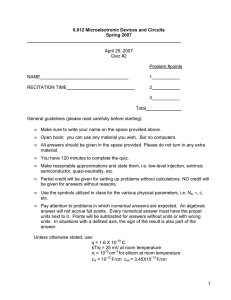

6.012 - Microelectronic Devices and Circuits - Fall 2005 Lecture 14-1 Lecture 14 - Digital Circuits (III) CMOS October 27, 2005 Contents: 1. Complementary MOS (CMOS) inverter: introduction 2. CMOS inverter: noise margins 3. CMOS inverter: propagation delay 4. CMOS inverter: dynamic power Reading assignment: Howe and Sodini, Ch. 5, §5.4 Announcements: • Cadence tutorial by Kerwin Johnson in place of regular recitations on Friday 10/28 6.012 - Microelectronic Devices and Circuits - Fall 2005 Lecture 14-2 Key questions • How does CMOS work? • What is special about CMOS as a logic technology? • What are the key design parameters of a CMOS inverter? • How can one estimate the propagation delay of a CMOS inverter? • Does CMOS burn any power? Lecture 14-3 6.012 - Microelectronic Devices and Circuits - Fall 2005 1. Complementary MOS (CMOS) Inverter Circuit schematic: VDD VIN VOUT CL Basic operation: •VIN = 0 ⇒ VOU T = VDD VGSn = 0 < VT n ⇒ NMOS OFF VSGp = VDD > −VT p ⇒ PMOS ON •VIN = VDD ⇒ VOU T = 0 VGSn = VDD > VT n ⇒ NMOS ON VSGp = 0 < −VT p ⇒ PMOS OFF Lecture 14-4 6.012 - Microelectronic Devices and Circuits - Fall 2005 Output characteristics of both transistors: IDn -IDp VGSn VSGp VGSn=VTn VSGp=-VTp 0 0 0 VDSn 0 VSDp Note: VIN = VGSn = VDD − VSGp ⇒ VSGp = VDD − VIN VOU T = VDSn = VDD − VSDp ⇒ VSDp = VDD − VOU T IDn = −IDp Combine into single diagram of ID vs. VOU T with VIN as parameter. Lecture 14-5 6.012 - Microelectronic Devices and Circuits - Fall 2005 VDD ID VIN VOUT VDD-VIN VIN CL 0 0 VOUT no current while id idling ling in any lo logic gic state state.. Transfer function: NMOS cutoff PMOS triode VOUT NMOS saturation PMOS triode VDD NMOS saturation PMOS saturation NMOS triode PMOS saturation NMOS triode PMOS cutoff 0 0 VTn VDD+VTp VDD VIN ail-to-rail” lo ”r ”rail-to-rail” logic: gic: lo logic gic levels are 0 and VDD high |Av | around logic threshold ⇒ good noise margins 6.012 - Microelectronic Devices and Circuits - Fall 2005 Lecture 14-6 Transfer characteristics of CMOS inverter in WebLab: Lecture 14-7 6.012 - Microelectronic Devices and Circuits - Fall 2005 2. CMOS inverter: noise margins VOUT NML VDD Av(VM) VM 0 0 VILVM VIH VDD VIN NMH • Calculate VM • Calculate Av (VM ) • Calculate N ML and N MH 2 Calculate VM (VM = VIN = VOU T ) At VM both transistors saturated: 1 Wn IDn = µnCox (VM − VT n)2 2 Ln −IDp = 1 Wp µpCox (VDD − VM + VT p )2 2 Lp Lecture 14-8 6.012 - Microelectronic Devices and Circuits - Fall 2005 Define: kn = Wn Wp µnCox, kp = µpCox Ln Lp Since: IDn = −IDp Then: 1 1 kn(VM − VT n )2 = kp(VDD − VM + VT p )2 2 2 Solve for VM : VM = VT n + � � � kp � kn (VDD + VT p ) 1+ � � � kp � kn Usually, VT n and VT p fixed and VT n = −VT p ⇒ VM engineered through kp/kn ratio Lecture 14-9 6.012 - Microelectronic Devices and Circuits - Fall 2005 • Symmetric case: kn = kp VM = VDD 2 This implies: kp =1= kn Wp µC Lp p ox Wn Ln µn Cox Wp µ Lp p Wn Ln 2µp Wp Wn ⇒ 2 Lp Ln Since usually Lp Ln ⇒ Wp 2Wn. VOUT VDD VIN=VOUT kn=kp 0 0 VTn VM VDD+VTp VDD VIN Lecture 14-10 6.012 - Microelectronic Devices and Circuits - Fall 2005 • Asymmetric case: kn kp , or Wn Ln Wp Lp VM VT n NMOS turns on as soon as VIN goes above VT n . • Asymmetric case: kn kp , or Wn Ln Wp Lp VM VDD + VT p PMOS turns on as soon as VIN goes below VDD + VT p . Can engineer VM anywhere betw between een VT n and VDD + VT p . VOUT VDD VIN=VOUT kn>>kp kn=kp kn<<kp 0 0 VTn VM VDD+VTp VDD VIN Lecture 14-11 6.012 - Microelectronic Devices and Circuits - Fall 2005 2 Calculate Av (VM ) VDD Small-signal model: VIN S2 + vsg2=-vin - + vin - + gmpvsg2 rop G2 D2 G1 D1 + vgs1 gmnvgs1 vout ron - - S1 G1=G2 D1=D2 + vin + gmnvin - gmpvin ron//rop vout - S1=S2 Av = −(gmn + gmp )(ron //rop ) This can be rather large. VOUT Lecture 14-12 6.012 - Microelectronic Devices and Circuits - Fall 2005 2 Noise margins VOUT NML VDD Av(VM) VM 0 0 VILVM VIH VDD VIN NMH • Noise-margin-low: VIL VDD − VM = VM − |Av | Therefore: N ML = VIL − VOL = VIL = VM − In the limit of |Av | → ∞: N ML → VM VDD − VM |Av | Lecture 14-13 6.012 - Microelectronic Devices and Circuits - Fall 2005 • Noise-margin-high: VOUT NML VDD Av(VM) VM 0 0 VILVM VIH VDD VIN NMH VIH = VM (1 + 1 ) |Av | and N MH = VOH − VIH 1 = VDD − VM (1 + ) |Av | In the limit of |Av | → ∞: N MH → VDD − VM When VM = VDD 2 ⇒ N ML = N MH = VDD 2 Lecture 14-14 6.012 - Microelectronic Devices and Circuits - Fall 2005 3. CMOS inverter: propagation delay Inverter propagation delay: time delay between input and output signals; key figure of merit of logic speed. Typical propagation delays: < 1 ns. Complex logic system has 20-50 propagation delays per clock cycle. Estimation of tp : use square-wave at input VIN VDD tCYCLE 0 VOUT t tPHL tPLH VDD 50% tCYCLE 0 t Average propagation delay: 1 tp = (tP HL + tP LH ) 2 Lecture 14-15 6.012 - Microelectronic Devices and Circuits - Fall 2005 2 Propagation delay high-to-low: VDD VOUT: HI LO VIN: LO HI CL VDD VIN=0 VDD VDD VOUT=VDD VOUT=0 VIN=VDD VIN=VDD VOUT=VDD CL CL t=0- t=0+ CL t During early phases of discharge, NMOS is saturated and PMOS is cut-off. Time to discharge half of CL: tP HL 1 2 charge of CL@t = 0− discharge current Lecture 14-16 6.012 - Microelectronic Devices and Circuits - Fall 2005 Charge in CL at t = 0−: QL(t = 0−) = CLVDD Discharge current (NMOS in saturation): IDn = Wn µnCox (VDD − VT n )2 2Ln Then: tP HL CLVDD Wn 2 Ln µnCox (VDD − VT n ) ID VDD-VIN VIN 0 0 VOUT Lecture 14-17 6.012 - Microelectronic Devices and Circuits - Fall 2005 2 Propagation delay low-to-high: VDD VOUT: LO HI VIN: HI LO CL VDD VDD VDD VOUT=0 VIN=VDD VOUT=VDD VIN=0 VIN=0 VOUT=0 CL CL t=0- t=0+ CL t During early phases of charge, PMOS is saturated and NMOS is cut-off. Time to charge half of CL: tP LH 1 2 charge of CL@t = ∞ charge current Lecture 14-18 6.012 - Microelectronic Devices and Circuits - Fall 2005 Charge in CL at t = ∞: QL(t = ∞) = CLVDD Charge current (PMOS in saturation): −IDp Wp = µp Cox(VDD + VT p )2 2Lp tP LH CLVDD Wp 2 µ C (V + V ) p ox DD T p Lp Then: ID VDD-VIN VIN 0 0 VOUT 6.012 - Microelectronic Devices and Circuits - Fall 2005 Key dependencies of propagation delays: • VDD ↑⇒ tp ↓ Reason: VDD ↑⇒ Q(CL) ↑, but also ID ↑ Trade-off: VDD ↑, more power usage. • L ↓⇒ tp ↓ Reason: L ↓⇒ ID ↑ Trade-off: manufacturing costs! Lecture 14-19 6.012 - Microelectronic Devices and Circuits - Fall 2005 Lecture 14-20 Components of load capacitance CL: • following logic gates: must add capacitance presented by each gate of every transistor the output is connected to • interconnect wire that connects output to input of following logic gates • own drain-to-body capacitances CL = CG + Cwire + CDBn + CDBp VDD VIN VOUT Cwire [See details in Howe & Sodini §5.4.3] 6.012 - Microelectronic Devices and Circuits - Fall 2005 Lecture 14-21 4. CMOS inverter: dynamic power • In any of the two logic states: one transistor always OFF ⇒ zero static power dissipation. • Dynamic power? Every complete transient, CL is charged up to VDD and then discharged to 0 ⇒ energy dissipated ⇒ clock frequency ↑ ⇒ dissipated power ↑ Lecture 14-22 6.012 - Microelectronic Devices and Circuits - Fall 2005 2 Dynamic power dissipated while charging load VDD VOUT iDD(t)=iC(t) VIN=HI LO VOUT=LO CL VDD HI 0 t 0 1. Energy provided by battery during transient: ES = = � dvOU T ∞ ∞ dt V i (t)dt = V C DD C DD 0 L 0 dt � VDD 2 CLVDD 0 dvOU T = CLVDD � = 2. Energy stored in capacitor during transient: 1 2 ∆EC = EC (t = ∞) − EC (t = 0) = CL VDD 2 3. Energy dissipated in PMOS during transient: 1 2 EP = ES − ∆EC = CLVDD 2 Lecture 14-23 6.012 - Microelectronic Devices and Circuits - Fall 2005 2 Dynamic power dissipated while discharging load VDD iDD(t)=0 VOUT VDD VIN=LO HI VOUT=HI iC(t) LO CL 0 0 1. Energy provided by battery during transient: ES = � ∞ 0 VDD iDD (t)dt =0 2. Energy removed from capacitor during transient: 1 2 ∆EC = EC (t = 0) − EC (t = ∞) = CL VDD 2 3. Energy dissipated in NMOS during transient: 1 2 EN = ∆EC = CLVDD 2 t 6.012 - Microelectronic Devices and Circuits - Fall 2005 Lecture 14-24 2 Energy dissipated in complete cycle 2 ED = EP + EN = ΣES = CLVDD 2 Power dissipation If complete switching cycle takes place f times per second: 2 PD = f ED = f CLVDD Fundamental F undamental trade-off between switching switching speed speed ant power power dissipation! Key dependencies in dynamic power: • f ↑⇒ PD ↑, charge and discharge CL more frequently • CL ↑⇒ PD ↑, more charge being shuttled around • VDD ↑⇒ PD ↑, more charge being shuttled around 6.012 - Microelectronic Devices and Circuits - Fall 2005 Lecture 14-25 Key conclusions • Key features of CMOS inverter: – no current while idling in any logic state – ”rail-to-rail” logic: logic levels are 0 and VDD – high |Av | around logic threshold ⇒ good noise margins • CMOS inverter logic threshold and noise margins engineered through Wn/Ln and Wp/Lp . • Key dependences of propagation delay: – VDD ↑ ⇒ tp ↓ – L ↓ ⇒ tp ↓ • Dynamic power dissipated in CMOS: 2 PD = f ED = f CLVDD Fundamental trade-off between switching speed and power dissipation.