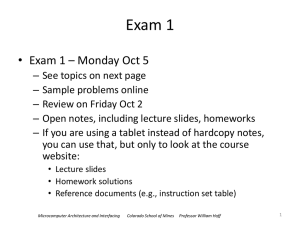

Analog-to-Digital Conversion (Part 2)

advertisement

Analog-to-Digital Conversion (Part 2) Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff Charge redistribution network • Instead of a resistor ladder for the D/A converter, the microcontroller uses an-all capacitor system to generate the known voltages • It is like a capacitor ladder, instead of a resistor ladder • An advantage is that it allows the unknown voltage to be sampled and “held”, while the comparisons are taking place • Recall basic formulas for capacitors: + + V C V - C1 C2 Q = CV Microcomputer Architecture and Interfacing Q = C 1V + C 2V Colorado School of Mines Professor William Hoff 2 Sample and hold • Sample mode comparator Total charge is Qs = 16 Vx assume VL = 0 • Hold mode Qh = (0 – Vi)16 = -16 Vi = Qs by charge conservation -16 Vi = 16 Vx so Vi = -Vx Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 3 Conversion • Now, let’s switch the largest capacitor up to VH • The total charge on the capacitors is still the same Q = 8(VH – Vi) + 8(0 – Vi) = 8 VH – 16 Vi = 16 Vx (charge conservation) so Vi = (8/16)VH - Vx • The comparator compares Vi against VL = 0; if Vi < 0 it outputs a 1 • Or, it outputs a 1 if Vx > (1/2) VH Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 4 Conversion (continued) • Let’s say that the unknown voltage is Vx > (1/2) VH • Next step is to switch the next largest capacitor up to VH Q = (8+4)(VH – Vi) + 4(0 – Vi) = 12 VH – 16 Vi = 16 Vx (charge conservation) so Vi = (12/16)VH - Vx • The comparator compares Vi against VL = 0; if Vi < 0 it outputs a 1 • Or, it outputs a 1 if Vx > (3/4) VH Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 5 Conversion (continued) • Each step switches the next largest capacitor up to VH • The output of the comparator determines if the capacitor remains at VH or is returned to VL • Continue for a total of n steps (for n bit conversion) Vi = ? Vi = ? Example 3rd step Microcomputer Architecture and Interfacing Example 4th step Colorado School of Mines Professor William Hoff 6 Successive approximation method • • • • Analog switches are transistors To get resistance as low as possible, the voltage on the gates must be high To get a high voltage (7 to 8V), a charge pump is used That’s why you only turn on the A/D converter if you need it Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 7 Quantization error Output code • Statistically, a quantization error of ±½ is better than 01 error • To offset by ½ bit, a fixed capacitor of value ½ is used 2n-1 VDD/2n VDD Voltage Figure 12.3 Output characteristic of an ideal n-bit A/D converter Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 8 8 bit A/D • To avoid needing a wide range of capacitor values, the ladder is split into two, with a small capacitor in series Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 9 HCS12 A/D Converter • The HCS12 uses a successive approximation A/D converter, with either 8 or 10 bit resolution • The highest frequency of the conversion clock is 2 MHz (period is 0.5 microseconds) • A/D conversion time is the sum of the converter time and the sample time – At 2 MHz ATD clock frequency, an 8-bit conversion takes 8 clock steps, or 4 microseconds – The sample time takes two clock steps (to charge the sample capacitor) and an additional 2, 4, 8, or 16 cycles (to store the charge in the storage node) Table 12.8 ATD conversion timings ATD clock frequency resolution converter time 2+2 sample clocks 2+4 sample clocks 2+8 sample clocks 2+16 sample clocks 2 MHz 2 MHz 500 KHz 500 KHz 8-bit(1) 10-bit(2) 8-bit 10-bit 4 s 5 s 16 s 20 s 2 s 3 s 5 s 9 s 8 s 12 s 20 s 36 s Note. 1. The fastest 8-bit resolution conversion time is 4 s + 2 s = 6 s. 2. The fastest 10-bit resolution conversion time is 5 s + 2 s = 7 s. Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 10 HCS12 A/D Converter • • • • You can generate an interrupt when conversion is done, or just poll a flag You can select from among 8 analog inputs Conversion is started by writing a value to a control register The conversion result can be right-justified unsigned, left-justified signed, and left-justified unsigned Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 11 • • An HCS12 can have two A/D converters Our chip (the C version) has only one • VRH, VRL (reference high and reference low) usually tied to Vcc and gnd • VDDA, VSSA are power supply inputs for the A/D (tie to Vcc and gnd) From the MC9S12C Family Reference Manual Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 12 Bus clock Clock prescaler Conversion complete interrupt • • Results are always stored in order, in the result registers starting with ATD 0 (ATDDR0) Confusing: the result from say, input AN2 doesn’t necessarily go into result register ATD 2 ATD clock Mode and timing control results VRH VRL VDDA VSSA Successive apparoximation Register (SAR) and DAC ATD 0 ATD 1 ATD 2 ATD 3 ATD 4 ATD 5 ATD 6 ATD 7 AN7/PAD7 AN6/PAD6 AN5/PAD5 AN4/PAD4 AN3/PAD3 AN2/PAD2 AN1/PAD1 AN0/PAD0 sample and hold 1 Analog MUX 1 + comparator ATD input enable register Port AD data register Figure 12.8 The HCS12 ATD block diagram Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 13 Channel Selection • • • • • CC, CB, and CA (ATD0CTL5) select channel (storing starts conversion) MULT bit: 0=single input, 1=multiple inputs SCAN bit: 1=scan continuously, 0=do once As each conversion completes and is stored into a result register, the corresponding CCF bit in ATD0STAT1 is set When all conversions complete, the SCF bit in ATD0STAT0 is set Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 14 Multiple Inputs Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 15 A/D registers • Each A/D module has the following registers: – – – – – – Four control registers: ATDxCTL2 - ATDxCTL5 Two status registers: ATDxSTAT0 and ATDxSTAT1 Two testing registers: ATDxTEST0 and ATDxTEST1 One input enable register: ATDxDIEN One port data register: PTADx Eight 16-bit result registers ATDxDR0~ATDxDR7 • where x = 0 or 1 • In our chip (the C version) we only have one module, so the “x” is not needed Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 16 A/D Control Registers • ATDCTL2 – ADPU – power up ATD system – AFFC – fast flag clear reset: 7 6 5 ADPU AFFC AWAI 0 0 0 1 0 ETRIGLE ETRIGP ETRIGE ASCIE ASCIF 0 0 0 4 0 3 2 0 ADPU: ATD power down bit 0 = power down ATD 1 = normal ATD operation AFFC: ATD fast flag clear all bit 0 = ATD flag is cleared normally, i.e., read the status register before reading the result register 1 = any access to a result register will cause the associated CCF flag to clear automatically if it is set at the time AWAI: ATD power down in wait mode bit 0 = ATD continues to run when the HCS12 is in wait mode 1 = halt conversion and power down ATD during wait mode ETRIGLE: External trigger level/edge control This bit controls the sensitivity of the external trigger signal. Details are shown in Table 12.1. ETRIGP: External trigger polarity This bit controls the polarity of the external trigger signal. See Table 12.1 for details. ETRIGE: External trigger mode enable 0 = disable external trigger on ATD channel 7 1 = enable external trigger on ATD channel 7 ASCIE: ATD sequence complete interrupt enable bit 0 = disables ATD interrupt 1 = enables ATD interrupt on sequence complete (ASCIF = 1) ASCIF: ATD sequence complete interrupt flag 0 = no ATD interrupt occurred 1 = ATD sequence complete interrupt pending Figure 10.9 ATD control register 2 (ATDxCTL2, x = 0 or 1) Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 17 A/D Control Registers • ATDCTL3 (S8C..S1C): successive conversions are placed into successive result registers Examples: • 1 conversion: result always goes into ATDDR0 • 4 conversions: successive results go into ATDDR0..ATDDR3 reset: 7 6 5 4 3 2 1 0 0 S8C S4C S2C S1C FIFO FRZ1 FRZ0 0 0 0 0 0 0 0 0 S8C,S4C,S2C,S1C: Conversion sequence limit 0000 = 8 conversions 0001 = 1 conversion 0010 = 2 conversions 0011 = 3 conversions 0100 = 4 conversions 0101 = 5 conversions 0110 = 6 conversions 0111 = 7 conversions 1xxx = 8 conversions FIFO: Result register FIFO mode 0 = conversion results are placed in the corresponding result register up to the selected sequence length 1 = conversion results are placed in consecutive result registers (wrap around at end) FRZ1 and FRZ0: background debug (freeze) enable bit 00: continue conversions in active background mode 01: reserved 10: finish current conversion, then freeze 11: freeze immediately when background mode is active Figure 10.10 ATD control register 3 (ATDxCTL3, x = 0 or 1) Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 18 A/D Control Registers 7 6 SRES8 SMP1 reset: • ATDCTL4 – PRS3:PRS0: The maximum clock is 2 MHz – So if we have a 24 MHz E clk, should set this to 5 (24 MHz/6 = 2 MHz) • SMP1:SMP0 determine sample time – The sample time is 2 clock periods, but you can add time for more accuracy Microcomputer Architecture and Interfacing 0 0 5 4 3 2 1 0 SMP0 PRS4 PRS3 PRS2 PRS1 PRS0 0 0 0 1 0 1 SRES8: ATD resolution select bit 0 = 10-bit operation 1 = 8-bit operation SMP1 and SMP0: select sample time bits These bits are used to select the length of the second phase of the sample time in units of ATD conversion clock cycles. See Table 12.2. PRS4--PRS0: ATD clock prescaler bits These five bits are the binary value prescaler value PRS. The ATD conversion clock frequency is calculated as follows: ATDclock = [bus clock] PRS + 1 0.5 The ATD conversion frequency must be between 500KHz and 2 MHz. The clock prescaler values are shown in Table 12.3. Figure 12.11 ATD control register 4 (ATDxCTL4, x = 0 or 1) Table 12.2 Sample time select SMP1 SMP0 0 0 1 1 0 1 0 1 Colorado School of Mines Length of 2nd phase of sample time 2 A/D conversion clock periods 4 A/D conversion clock periods 8 A/D conversion clock periods 16 A/D conversion clock periods Professor William Hoff 19 A/D Control Registers 7 DJM reset: • ATDCTL5 – Set SCAN=1 to do continuous conversions – Set MULT=0 to convert only one input – CC,CB,CA selects input Table 12.4 Analog input channel select code CC CB CA analog input channel 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 AN0 AN1 AN2 AN3 AN4 AN5 AN6 AN7 Microcomputer Architecture and Interfacing 0 6 5 4 DSGN SCAN MULT 0 0 0 3 2 1 0 0 CC CB CA 0 0 0 0 DJM: Result register data justification 0 = left justified data in the result registers 1 = right justified data in the result registers DSGN: Result register data signed or unsigned representation 0 = unsigned data representation in the result registers 1 = signed data representation in the result registers (not available in right justification) SCAN: Enable continuous channel scan bit 0 = single conversion sequence 1 = continuous conversion sequences (scan mode) MULT: Enable multichannel conversion bit 0 = sample only one channel 1 = sample across several channels CC, CB, and CA: Channel select code The channel selection is shown in Table 12.4. Figure 12.12 ATD control register 5 (ATDxCTL5, x = 0 or 1) Colorado School of Mines Professor William Hoff 20 A/D Status Registers reset: • ATDSTAT0 – SCF: Use to check when sequence is complete – CC2:CC0: indicates the number of the result register that will hold the result 7 6 SCF 0 0 0 5 4 ETORF FIFOR 0 0 3 2 1 0 0 CC2 CC1 CC0 0 0 0 0 SCF: Sequence complete flag 0 = conversion sequence not completed 1 = conversion sequence has completed ETORF: External trigger overrun flag 0 = no external trigger overrun has occurred 1 = external trigger overrun has occurred FIFOR: FIFO overrun flag 0 = no overrun has occurred 1 = an overrun has occurred CC2, CC1, CC0: conversion counter The conversion counter points to the result register that will receive the result of the current conversion. In non-FIFO mode, this counter is reset to 0 at the begin and end of the conversion. In FIFO mode, this counter is not reset and will wrap around when its maximum value is reached. Figure 12.13 ATD status register 1 (ATDxSTAT0, x = 0 or 1) Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 21 A/D Status Registers • ATDSTAT1 – Conversion complete flags for all channels – You can poll this to find out when conversion is done – If fast flag clear is selected, the flag is cleared by reading the result register reset: Microcomputer Architecture and Interfacing 7 6 5 4 3 2 1 0 CCF7 CCF6 CCF5 CCF4 CCF3 CCF2 CCF1 CCF0 0 0 0 0 0 0 0 0 CCFx: conversion complete flag x (x = 7~0) 0 = conversion number x not completed 1 = conversion number x has completed, result in ATDyDRx Figure 12.15 ATD status register 1 (ATDxSTAT1, x = 0 or 1) Colorado School of Mines Professor William Hoff 22 Summary of A/D Registers • Red - used for initialization • Green - for interrupt configuration • Black = for channel selection and making measurements Register 7 6 5 4 ATD0CTL2 ADPU AFFC AWAI ETRIGLE ETRIGP ETRIGE ASCIE ASCIF ATD0CTL3 0 S8C S4C S2C S1C FIFO FRZ1 FRZ0 ATD0CTL4 SRES8 SMP1 SMP0 PRS4 PRS3 PRS2 PRS1 PRS0 ATD0CTL5 DJM DSGN SCAN MULT 0 CC CB CA ATD0STAT0 SCF 0 ETORF FIFOR 0 CC2 CC1 CC0 ATD0STAT1 CCF7 CCF6 CCF5 CCF4 CCF3 CCF2 CCF1 CCF0 Microcomputer Architecture and Interfacing Colorado School of Mines 3 2 Results go into ATDDR0..ATDDR7 Professor William Hoff 1 0 23 Initialization • ADPU bit enables the ATD module (is disabled by default to conserve power) • Takes 10 microseconds for the ATD to become operating after setting the ADPU • Example: – Set up A/D to digitize continuously on channel 2 ATDCTL2 = 0xc0; // turn on ATD and enable fast flag clear ATDCTL3 = 0x08; // set the ATD for 1 channel conversion ATDCTL4 = 0x85; // set the ATD for 2 MHz,2 sample clks,8 bits ATDCTL5 = 0xa2; // right justified, continuous conversions of AD2 /* A/D results appear in ATDDR0L */ Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 24 Example • Set up A/D to convert and average 4 successive voltage readings on channel 3, using 10 bits ATDCTL2 = 0xc0; // turn on ATD and enable fast flag clear : //wait 10 microseconds to power up ATDCTL3 = 0x20; ATDCTL4 = 0x05; // set the ATD for 4 conversions // set the ATD for 2 MHz,2 sample clks,10 bits // Start the conversion ATDCTL5 = 0x83; // right justified, single conversion of AD3 while (!(ATDSTAT0 & 0x80)) ; // wait for SCF = 1 // Read and average the four measurements result = (ATDDR0 + ATDDR1 + ATDDR2 + ATDDR3)/4; Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 25 A to D Converter Types • • • • • Successive Approximation Tracking A/D Converter Dual-slope A/D Converter Parallel (flash) A/D Converter Two-stage parallel A/D Converter Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 26 Tracking A/D Converter • Very fast digitization as long as signal changes slowly Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 27 Dual-Slope A/D Converter • Integrate input voltage for a fixed time T1 • Then discharge it, and time how long it takes to reach zero • Can be very accurate where speed isn’t a concern (e.g., a multimeter) • If you have periodic noise (e.g., 60Hz), can cancel it by making T1 equal to the period Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 28 Flash A/D Converter • Very fast, but expensive Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 29 Summary / Questions • The HCS12 uses a successive approximation A/D converter. A “charge redistribution network” (composed of capacitors) is used to generate known voltages. • Why does a 10-bit conversion take longer than an 8bit conversion? Microcomputer Architecture and Interfacing Colorado School of Mines Professor William Hoff 30