Lecture 20 Transistor Amplifiers

advertisement

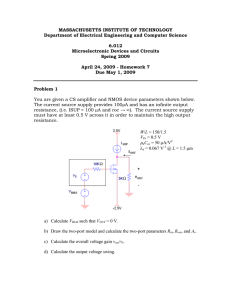

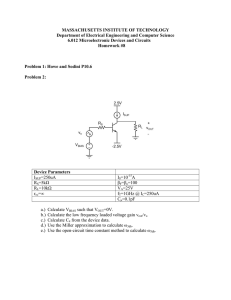

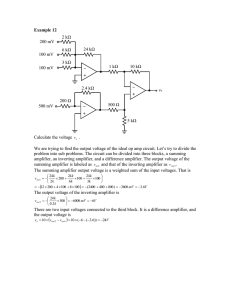

Lecture 20 Transistor Amplifiers (II) Other Amplifier Stages Outline • Common­drain amplifier • Common­gate amplifier Reading Assignment: Howe and Sodini; Chapter 8, Sections 8.7-8.9 6.012 Spring 2009 1 1. Common­drain amplifier VDD signal source RS + vs iSUP vOUT signal load RL VBIAS VSS • • • • • • A voltage voltage buffer takes the input input voltage voltage which may which may have a relatively large Thevenin resistance and replicates the voltage at the output port, which has a low output resistance Input signal is applied to the gate Output is taken from the source To first order, voltage gain ≈ 1 Input resistance is high Output resistance is low – Effective voltage buffer stage How does it work? • vgate ↑⇒ iD cannot change ⇒ vsource ↑ – Source follower 6.012 Spring 2009 2 Biasing the Common­drain amplifier VDD signal source RS VSS + vs iSUP vOUT signal load RL VBIAS VSS • Assume device in saturation; neglect RS and RL; neglect CLM (λ = 0) • Obtain desired output bias voltage – Typically set VOUT to”halfway” between VSS and VDD. • Output voltage maximum VDD­VDSsat • Output voltage minimum set by voltage requirement across ISUP. VBIAS = VGS + VOUT VGS = VTn (VSB ) + 6.012 Spring 2009 I SUP W µn Cox 2L 3 Small­signal Analysis Unloaded small­signal equivalent circuit model: + D G gmvgs vin ro S + roc vout - - + + vgs - vin + gmvgs ro//roc - vout - vin = v gs + vout vout = gm v gs (ro // roc ) Then: Avo = 6.012 Spring 2009 gm 1 gm + ro // roc ≈1 4 Input and Output Resistance Input Impedance : Rin = ∞ Output Impedance: + + vin RS it + vgs - gmvgs ro//roc - - vt vin = 0; vt = ­vgs effectively: resistance of value 1/gm Rout = it + gmvt 1 gm + 1 ro // roc ro//roc ≈ - vt 1 gm Small! Loaded voltage gain: RL RL Av = Avo ≈ ≈1 1 R L + Rout R + L gm 6.012 Spring 2009 5 Effect of Back Bias If MOSFET was not fabricated in an isolated p­well, then body is tied to wafer substrate (connected to VSS) VDD signal source RS VSS + vs iSUP vOUT signal load RL VBIAS VSS Two consequences: • Bias is affected – VT depends on VBS – VBS = VSS – VOUT ≠ 0 • Small signal figures of merit affected – Signal shows up between B and S – vbs = ­vout 6.012 Spring 2009 6 Small­signal Analysis (with back­bias) See text pp.523­527 for details D G + gmvgs gmbvbs ro S vin + roc - vout B - vbs=-vout + vgs - + vin + gmvgs gmbvout ro//roc - Avo = vout - gm g m + g mb + 1 ro // roc gm ≈ <1 g m + g mb Also: Rout = 6.012 Spring 2009 1 1 g m + gmb + ro // roc ≈ 1 g m + gmb 7 Common­Drain Two­Port Model 1 (gm + gmb) + vin + + − gm (gm + gmb) vin − vout − • Open circuit voltage gain ~ 1 • Input resistance ~ CS Amplifier – We want a large input resistance because the controlled generator is voltage controlled • Output resistance << CS Amplifier – We want a low output resistance to deliver most of the output voltage to the load 6.012 Spring 2009 8 Relationship between circuit parameters and device parameters: W gm = 2I D µ nCox L gmb = γ 2 −2φ p − VBS gm Circuit Parameters Device* Parameters |Avo| gm g m + g mb Rin ∝ Rout 1 g m + g mb ISUP ↑ ­ ­ ↓ W↑ ­ ­ ↓ µnCox ↑ ­ ­ ↓ L↑ ­ ­ ↑ * VBIAS is adjusted so that none of the other parameters change Common Drain amplifier is often used as a voltage buffer to drive small output loads (in multistage amplifiers, other stages provide the voltage gain). 6.012 Spring 2009 9 2. Common­Gate Amplifier: VDD iSUP iOUT VSS signal load RL signal source is RS IBIAS VSS • A current buffer takes the input current which may have a relatively small Norton resistance and replicates the current at the output port, which has a high output resistance • Input signal is applied to the source • Output is taken from the drain • To first order, current gain ≈ 1 – is ≈ ­iout.(Current Buffer) • Input resistance is low • Output resistance is high – Effective current buffer stage 6.012 Spring 2009 10 Biasing the Common­Gate Amplifier: Assume device in saturation; neglect RS and RL; neglect CLM (λ = 0) VDD ISUP IOUT VSS IBIAS I SUP + IOUT + I BIAS = 0 VSS Select bias such that IOUT=0 ⇒ VOUT = 0. Assume MOSFET in saturation (no channel modulation): W 2 ID = µ nCox (VGS − VT ) = I SUP = −I BIAS 2L But VT depends on VBS: VT = VTo + γ n ( −2φp − VBS − −2φ p ) Must solve these two equations iteratively. 6.012 Spring 2009 11 Small­signal equivalent circuit (unloaded) iout D + G vgs gmvgs gmbvbs ro - S roc B is vbs=vgs iout - it i s vgs gmvgs gmbvgs ro + iout it is it = −iout ­1 gm ­1 gmb ro iout ⇒ Aio = = −1 it Aio is the short circuit current gain. Not surprising, since in a MOSFET: ig = 0 6.012 Spring 2009 12 Input Resistance + vgs gmbvgs gmvgs ro - roc + it RL vt - vgs=-vt + gmvt it gmbvt ro vt roc//RL - Do KCL on input node: v t − it (roc // R L ) it − g mv t − gmb v t − =0 ro Then: r // RL 1 + oc ro vt 1 Rin = = ≈ it g + g + 1 gm + g mb m mb ro 6.012 Spring 2009 13 Output Resistance + vgs gmvgs gmbvgs it ro - + roc - vt RS + vgs gmvgs gmbvgs it ' ro + - - vt' RS Do KCL on input node: vt′ + v gs it′ − g mv gs − gmb v gs − =0 ro Notice also: v gs = −it′ Rs Then: Rout 1 = roc // ro 1+ Rs gm + gmb + ro Rout ≈ roc //[ro (1+ gm Rs )] ≈ roc //[(gm ro )Rs ] 6.012 Spring 2009 14 Common­Gate Two­Port Model iin i out 1 gm + gmb −iin roc ⎢⎢(ro + gmroRS) • The output resistance depends on the source resistance – The CG current buffer is not unilateral • Input resistance << CS Amplifier – We want a small input resistance because the controlled generator is current controlled • Output resistance >> CS Amplifier – We want a large output resistance to deliver most of the output current to the load 6.012 Spring 2009 15 Relationship between circuit figures of merit and device parameters: W gm = 2I D µ nCox L γ gmb = gm 2 −2φ p − VBS ro ≈ 1 λn I D Circuit Parameters Device* Parameters |Aio| Rin Rout ­1 1 g m + g mb roc //[ro (1+ g m R s )] ISUP ↑ ­ ↓ ↓ W↑ ­ ↓ ↑ µnCox ↑ ­ ↓ ↑ L↑ ­ ↑ ↑ * VBIAS is adjusted so that none of the other parameters change Common Gate amplifier is often used as a current buffer i.e. transform a current source with medium source resistance to an equal current with high source resistance (in multistage amplifiers, other stages provide the current gain). 6.012 Spring 2009 16 What did we learn today? Summary of Key Concepts • Common­source amplifier: good voltage amplifier better transconductance amplifier – Large voltage gain – High input resistance – Medium / high output resistance • Common­drain amplifier: good voltage buffer – Voltage gain ≈ 1 – High input resistance – Low output resistance • Common­gate amplifier: good current buffer – Current gain ≈ 1 – Low input resistance – High output resistance 6.012 Spring 2009 17 MIT OpenCourseWare http://ocw.mit.edu 6.012 Microelectronic Devices and Circuits Spring 2009 For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.