Document 13383752

advertisement

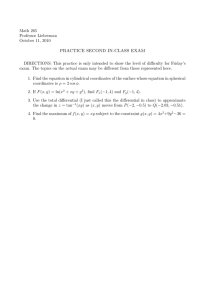

MASSACHUSETTS INSTITUTE OF TECHNOLOGY Department of Electrical Engineering and Computer Science 6.301 Solid State Circuits Fall Term 2010 Problem Set 3 Issued : Sept. 17, 2010 Due : Friday, Sept. 24, 2010 Suggested Reading: Read as many of the following as you can. All of the recommended references are on reserve at Barker Library. 1. Lundberg sections 4 and 5. 2. Grebene section 5.1. 3. Gray and Meyer section 3.5. Problem 1: Find the mid-band gain for each circuit below. Assume that β = 400, VBE,ON = 0.6V, and ignore ro . (a) Circuit a +5V +5V +5V +5V 1.2k 1.3k vo 1k Q1 Q2 vi 1uF 1k 1.3k 1uF 2.6V (b) Circuit b +5V +5V 2k 1k +5V 1.4k 1.3k 1uF vo Q2 Q1 vi +5V Q3 3.0k 3k 2.4k 1uF 2.4k 1 1uF Problem 2: Simulate the CE-EF-CE amplifier in Circuit 1b (above) with HSPICE. Use the following data for your simulations: IS = 10−15 A, βF = 200, VA =100, τF = 0.1ns, cjeo = 10pF, and cjco = 2pF. Turn in your HSPICE input file, and an Awaves plot showing the low and high frequency roll-offs. Problem 3: For the differential amplifier shown below: VCC RC RC vo1 vo2 RL vi1 Q1 vi2 Q2 RE IEE IEE -VEE (a) Find the differential voltage gain avd and the common mode voltage gain avc . (b) Find both the differential and common mode input and output resistances (Rin,d , Rin,c , Rout,d , and Rout,c ). 2 Problem 4: For the single-ended differential amplifier shown below, assume that β = 200 and VBE,ON = 0.6V for both transistors, and that the DC common mode input voltage is zero. Neglect ro for this problem. VCC =15V RL RL vo vi1 Q1 Q2 vi2 RE -VEE =-15.6V (a) Express the differential voltage gain avd as a function of the voltage drop VL across RL . (b) If VCE,SAT = 0.3V, what is the maximum avd possible? (c) Select RL and RE so that Rin,d = 1MΩ and avd = 300. What is the common mode rejection ratio (CMRR)? 3 Problem 5: For each circuit below, find the transfer function vo /vi , and draw the Bode plot (magnitude and phase). (a) Circuit a + − vi R1=100k R2=100k C1=0.1uF C2=1uF vo (b) Circuit b R1=100k + − vi C1=0.1uF C2=1uF vo R2=100k (c) Circuit c C1=1uF R1=10k vi + − R2=90k 4 vo C2=4uF MIT OpenCourseWare http://ocw.mit.edu 6.301 Solid-State Circuits Fall 2010 For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.