× A 128 128 Floating Gate Imager with Self-Adapting Fixed Pattern Noise Reduction

advertisement

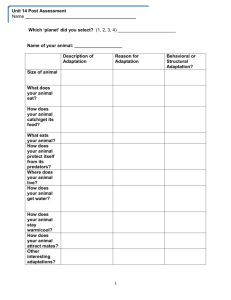

A 128×128 Floating Gate Imager with Self-Adapting Fixed Pattern Noise Reduction Yanyi Liu Wong, Marc H. Cohen and Pamela A. Abshire yanyi.wong/marc.cohen/pamela.abshire@ieee.org Institute for Systems Research, University of Maryland, College Park, MD 20742, U.S.A. Abstract— We present a novel CMOS current-mode imager that uses nonvolatile floating gate charge storage in the pixel for automatic cancellation of fixed-pattern noise (FPN). We demonstrate the ability to reduce the variance of the initial FPN over a range of incident light intensities. Each pixel incorporates a unique circuit that uses pFET hot-electron injection to adapt out the FPN for each pixel in parallel. The design has been fabricated in a commercially available 0.5µm process. Experimental results confirm the ability to reduce the FPN variance by a factor of 98.23 at the intensity at which adaptation was performed, and by a factor of 9.22 over 5 orders of magnitude of intensity. The adaptation takes ∼ 6 minutes and the 128 × 128 image can be read at 7 frames/sec. The chip consumes 43.3mW. I. I NTRODUCTION Imagers are transducers that convert optical images into electrical signals. Fabrication process variations cause fixed pattern noise that creates unwanted artifacts in the image and compromises the maximum dynamic range of an imager. Both deterministic and random variations impose severe limitations on the dynamic range and picture quality of CMOS imagers. A common approach used in active pixel imagers is to cancel offset with correlated double sampling (CDS) [1]. CDS often produces satisfactory results for imagers that perform the relatively simple job of transducing. However, CDS is difficult to implement in current-mode imagers that offer wide dynamic range or for smart sensors that perform sophisticated computation on the image plane such as motion detection, edge enhancement, or feature extraction [2]. Massively parallel high dynamic range image plane computation is best performed in current mode continuous time image sensors [2]. Since FPN is a static characteristic of each pixel comprising an imager, it seems natural to reduce it by using nonvolatile analog storage of a fixed charge on a floating gate in each pixel. The floating gate technique has long been used for adaptation and calibration purposes. It has been used to trim current sources [3]–[5], to autozero amplifiers [6], [7], to store/cancel offset in comparators [8], and to correct nonuniformity in imagers [9]. In [9], an external comparator is used to compare the randomly selected pixel readout and that of the previous pixel to determine the local update direction. Over a large number of iterations, it achieves both FPN nonuniformity correction and intensity histogram equalization. We describe a new circuit configuration that exploits local hot-electron injection to enable parallel adaptation of each pixel to a desired common voltage output given a uniform incident light intensity. Since the adaptation of all pixels proceeds 0-7803-8834-8/05/$20.00 ©2005 IEEE. in parallel by simply raising the power supply voltage, it is fast and accurate. In sections II, III and IV we present our design approach for accurate, automatic FPN removal, the design of our adaptive floating gate pixel (AFGP), and experimental results from fabricated chips and their interpretation. II. BACKGROUND A. Floating Gate Structure A floating gate MOSFET uses an electrically isolated material such as polysilicon to store charge indefinitely. In our imager, the individual charge required to cancel each pixel’s FPN offset is locally stored on a non-volatile floating gate, and altered by means of hot-electron injection. The injection mechanism has been extensively described in the literature [7], [10]. Impact-ionized hot-carrier injection occurs in p-type MOSFETs when two conditions are satisfied: a large lateral electric field EL along the channel to increase the probability of impact-ionization and produce high energy electrons, and a large vertical electric field EV across the gate oxide to sweep these hot electrons across the oxide barrier. For an ordinary pFET, it is relatively easy to achieve both conditions under normal operation. We utilize pFET injection in a novel circuit configuration that achieves automatic, accurate FPN reduction inside each pixel. B. Mismatch in the Phototransistor Photocurrent current across an illuminated depletion density −αW region is J = −qΦ0 1 − e1+αL −Js where Φ0 is the flux of photons per unit area, α is the optical absorption coefficient, W is the depth of the depletion region, L is the minority carrier diffusion length and Js is the dark current [11]. W depends on reverse bias voltage and W , α, L and Js depend on doping concentrations. We use a vertical pnp phototransistor as the photosensor in our pixel. The collector is the p-substrate, the base is the n-well, and the emitter is a p-diffusion located in the n-well. The base-emitter junction is biased by the photo current, so the emitter current is Ip = βAJ. The current gain β and the area A are sensitive to the fabrication process. Note that β is a nonlinear function of J particularly for small J [11], and we operate in the region where β is approximately constant. Parameters that depend on doping concentration and geometry are susceptible to mismatch. By grouping thevariables, we −αW get Ip = kΦ0 −Js βA ≈ k·Φ0 where k = −qβA 1 − e1+αL . The phototransistor current Ip is approximately proportional to 5314 Fig. 1. AFGP circuit: (a) pixel circuit; (b) injection circuit. Channel current I2 balances with current source I3 during injection. the photon flux Φ0 with a poorly-controlled gain k that varies from phototransistor to phototransistor. This relationship is valid for photocurrent much larger than the dark current Js A. In the remaining discussion, we explicitly model mismatch as Ip = αp C0 Φ0 , (1) where C0 is the nominal value for gain k and is assumed to be the same for all transistors. αp is the gain mismatch for individual transistors, with a mean value of 1. C. Mismatch in subthreshold MOSFET Channel current for a MOSFET operating in subthreshold is an exponential function of terminal voltages: V VG V W − US − UD nUT ID = I0 e e T −e T (2) L where VG , VD and VS are gate, drain and source voltages, respectively, UT is the thermal voltage UT = kT /q, W L is the width to length ratio, I0 the characteristic current, and n the slope factor. For VS = 0 and VD ≥ VG , (2) can be VG nUT approximated by ID ≈ W . L I0 e The slope factor n is a function of the surface depletion capacitance Cd and the gate oxide capacitance COX , where n = 1 + Cd /COX , so that n can be considered approximately constant [12]. However, the characteristic current I0 is poorly controlled. Characteristic current and geometry variation are the main sources of mismatch in subthreshold MOSFETs. We explicitly model mismatch m in the channel current ID using ID m = αm W L−1 I0 exp(VG /nUt ). Here W I0 /L is the same for all transistors of nominal geometry W/L, and the mismatch factor αm varies from transistor to transistor with mean value of 1. Rewriting ID m we obtain ID m = W L−1 I0 exp [(VG + ∆Vm )/nUt ], where ∆Vm = nUT ln αm . Two main points can be seen from the above development; firstly, mismatch in subthreshold MOSFET drain current is primarily due to mismatch in the current gain and secondly, the current gain error is equivalent to gate voltage offset error. III. A DAPTIVE F LOATING G ATE P IXEL A. Circuit Overview Fig.1(a) shows the implementation of our Adaptive Floating Gate Pixel (AFGP). The AFGP directly transduces photocurrent. Phototransistor Q1 is exposed to incident light and produces an amplified photocurrent Ip at its emitter. This photocurrent is then translated into voltage logarithmically by diode connected M1. Neglecting parasitic capacitances on M2, we see that M1 and M2 form a “floating current mirror” and that I2 = Ip ∗ f1 (VC1 ), where VC1 is the voltage drop across capacitor C1 between VA and the floating gate VB , and f1 is exponential in VC1 . In addition to the capacitor C1 , the floating gate is capacitively coupled to a globally connected node VEL , through a much smaller capacitance C2 . This global node VEL provides an external control to the floating gate and is especially useful for compensating the common mode shifts of the floating gate voltages induced by injection. The mirrored current is then translated into voltage VD by a current conveyor M3-5, where M5 provides a strong bias current that increases the driving strength for fast column line settling. The column line is set to VD by turning on M6 during row activation. Offchip A/D converters convert the analog column voltage VD into digital form that can be read by a PC or microcontroller. B. Floating Gate used for Offset Compensation We analyze the AFGP circuit to find the charge q that should be stored on the floating gate to compensate for overall mismatch. We define a constant I 0 = W L I0 and variables Va = Vdd − VA , Vb = Vdd − VB for short-hand notation. The channel currents for M1, M2 and M3 are Ip I2 I2 = I 0 exp [(Va + ∆V1 )/np UT ] = I 0 exp [(Vb + ∆V2 )/np UT ] = I 0 exp [(VD + ∆V3 )/nn UT ] (3) (4) (5) respectively, neglecting body effect and assuming that M4 and M5 are biased correctly such that M3 is effectively diodeconnected. Note that the differences in individual transistor geometry and characteristic current I0 for both p- and n-type MOSFETs are incorporated into mismatch quantities ∆V1 , ∆V2 and ∆V3 and that I 0 is a mismatch-free quantity that is consistent among all transistors. Next, we express the floating gate voltage according to charge-sharing as Vb = λ1 Va + V0 , where λ1 is the ratio of C1 to the total capacitance CT on the floating node, and V0 is the voltage from the charge q stored on the floating gate, V0 = q/CT . 1 From (3) and (4), we first equate Ip with I2 , substitute into (5) and rearrange, then substitute (3) for Va and (1) for Ip . n By setting V0 = λ1 ∆V1 − ∆V2 + nnp ∆V3 − λ1 np UT ln αp , we obtain C0 Φ0 VD = λ1 nn UT ln . (6) I0 The pixel output VD is logarithmic in the photon flux Φ0 and the offset contributions from Q1, M1, M2 and M3 are entirely eliminated. C. Adaptation Each pixel automatically adapts to cancel its unique offset value by exploiting the negative feedback property of pFET hot-electron injection for constant current bias. During adaptation, we use uniform intensity incident light to illuminate the imager, but Ip , VA , VB , I2 and VD still differ from pixel to pixel. Each pixel adapts by injecting appropriate charge onto 5315 1 We assume that all parasitic capacitances are connected to fixed voltages. its floating gate so that all pixel outputs approach a desired constant voltage VD ∗ . Fig.1(b) shows the mechanism for self-regulated pFET hot electron injection used in the AFGP. The drain of the floating gate transistor M2 is connected to a current source I3 implemented by M3 with a gate bias voltage VD ∗ . I3 is also a source of inter-pixel mismatch. Recall that I2 is produced by the path from Q1, M1, C1 to M2, and that the mismatch of these transistors and the voltage stored on C1 are responsible for inter pixel variations in I2 . We apply a large enough bias VD ∗ to M3 such that for every pixel I2 < I3 . Thus for every pixel the drain voltage V3 is pulled to ground, and the sourceto-drain voltage Vsd on M2 is equal to the power supply Vdd. A normal operating power supply Vdd is chosen such that the EL is insufficient for hot electron injection. During adaptation, we raise Vdd to enable injection. As electrons are injected onto the floating gate, the floating gate voltage decreases. The decreased gate voltage increases I2 . Injection continues until I2 approaches I3 , and V3 begins to increase above ground. This decreases Vsd and stops injection. This intrinsic feedback loop leads to self current calibration. The transition from operation to adaptation is simple. In Fig.1(a), M3 forms part of a current conveyor during normal operation, and in Fig.1(b) M3 is the current source that provides I3 during adaptation. For global adaptation, all row switches M6 are turned on, and all columns are set to VD ∗ , with VD ∗ set to the maximum voltage of all measured pixels to ensure that initially all pixels have I2 < I3 . At the same time we turn off M5 and M4 is also off because V3 is pulled to ground. Thus, with M4 and M5 off, the AFGP enters adaptation mode as in Fig.1(b). Next, Vdd is raised and hot electron injection proceeds until an equilibrium is reached where I2 = I3 for all pixels. Because this current calibration loop encompasses the entire pixel, we compensate the offsets due to Q1, M1, M2 and M3 simultaneously in each pixel. D. Layout The pixel size is 66λ×66λ, with λ = 0.3µm. The fill factor is 13%. The chip was fabricated in a commercially available 0.5µm nWell CMOS technology. The entire chip is covered with metal 3 with windows around each phototransistor and floating gate. The floating node consists of the top plate of a poly-poly2 capacitor, the poly gate of a pFET, and the metal that connects them. This arrangement minimizes stray capacitances to ground. On top of the poly2 is metal 1 which is the global node VEL . IV. E XPERIMENTAL R ESULTS We use an integrating sphere to supply uniform light intensity for calibration and FPN measurement and introduce neutral density filters into the optical path to produce uniform light with different intensities. We denote the unfiltered source intensity as I. The circuit board with the imager chip is shielded electrically and optically. The column line voltage is read by a 16-bit A/D converter in a computer based data acquisition card. The range of the ADC is between 0 and 1 Volt, and the resolution is 15.3µV. The ADC is calibrated so that sampling error is minimized. 16 columns of the imager can be sampled simultaneously giving a maximum of 7 frames/s. Figure 2 shows the histograms of the output voltage VD for all pixels. For a large number of identically distributed pixels (16k pixels available), the histogram approximates the probability density function (pdf) if we consider the output voltage VD as a random variable. Therefore, we quantify the FPN noise power according to the variance σ 2 of VD obtained from the pdf. In Fig.2(a), we measure VD for each pixel of the UV-erased chip under 10−1 I intensity and plot the histogram with dots. The solid trace is a Gaussian fit using least squared error curve-fitting. As expected, the FPN is approximately Gaussian. The standard deviation σ of the Gaussian pdf fit is 16.6mV, and that of the measured VD is 20.5mV. In Fig.2(b), we plot VD measurements with two intensities: I and 10−2 I. The dashed traces are measurements taken prior to UV-erasure, and the solid traces are measurements taken after UV-erasure. The peaks around VD = 0.75V are with intensity I, and those around VD = 0.6V are with intensity 10−2 I. As shown, the raw chip has consistently higher voltage outputs for all intensity levels prior to being UV-erased, but the FPN power σ 2 remains the same. This implies that there is initially negative charge on all floating gates. We first perform adaptation at intensities I and 10−2 I, then take measurements for different intensities from I down to 10−6 I. We set VD ∗ to 0.75V, supply it to all columns, turn on all rows and turn off M5. Next, we perform adaptation for 4 seconds by raising Vdd to 5.15V. We repeat the adaptation process taking measurements each time. The time course of adaptation is plotted in a waterfall fashion depicted in Fig.3. During the first injection at t = 4s, the bell-shaped distribution at 0.5V collapses to the right. During subsequent adaptation cycles, the mean of the VD distribution gradually moves to the right. Finally they accumulate around VD ∗ = 0.75V. We continue to adapt for about 6 minutes, but most pixels have completed adaptation by 3 minutes. Figure 4(a) shows the standard deviation of FPN for measurements at intensities 10−7 I to I, before adaptation (white), after adaptation at I (gray), and after adaptation at 10−2 I Fig. 2. Output voltage histograms before adaptation (direct from fab and after UV-erasure). 5316 Fig. 5. Fig. 3. Fig. 4. A waterfall plot for injection time course. Slide (a) before and (b) after adaptation. tomatically remove fixed pattern noise (FPN) simultaneously from all pixels. We have described theory and method for adapting the voltage on the floating gate of a pFET that leads to a stable equilibrium. The mechanism that is used to adapt out FPN is hot electron injection inside each pixel. Injection stops when two currents inside the pixel balance each other through a negative feedback loop. In addition to canceling offset, each pixel can be used to accurately set up an arbitrary input offset thus creating a “shadow” image that could be used for digital watermarking. This feature is not readily available in other FPN removal schemes. During adaptation, an external voltage is applied globally to all pixels and the imager is uniformly illuminated. We have experimentally demonstrated that FPN can be reduced by a factor of ∼ 100. The pixel output voltage is logarithmically related to the photon flux allowing for a large dynamic range. Each pixel measures ∼ 20µm on a side and has a fill factor of 13%. The chip consumes 43.3mW. VI. ACKNOWLEDGEMENTS We thank the MOSIS service for providing chip fabrication through their Educational Research Program. Y.W. is supported by Johns Hopkins University Applied Physics Laboratory. P.A. is supported by an NSF CAREER Award (NSF-EIA-0238061). R EFERENCES Performance of adaptation at intensity I. (black). FPN is smaller around the adaptation intensity, and grows larger as the intensity deviates from the adaptation intensity. For adapting at I, we achieve a factor of 98.23 FPN variance reduction at the adaptation intensity I, and a factor of 25.00 over the intensity range from 10−2 I to I. For adapting at 10−2 I, we achieve a factor of 22.74 FPN variance reduction at adaptation intensity 10−2 I, and 9.22 over the intensity range from 10−4 I to I. Fig.4(b) shows the mean of VD at different intensities before and after adaptation. It can be seen that VD rises 88.3mV/decade for both. After adaptation, the mean voltage rises 234mV for I and 155mV for 10−2 I. Note that the measurement for 10−7 I is absent for pre-adaptation. This is because VD reaches 0 at 10−6 I. Thus, the imager should be calibrated at the appropriate operating intensity to achieve maximum FPN removal over a range of intensities about the calibration intensity. A standard 35mm camera lens is used to focus images of distant objects. We use slides illuminated from the back as targets. A triangle with sharp angles is used as the target to manually focus the lens. Figure 5 shows the image of a slide before (a) and after (b) 10−2 I calibration. The mean value for voltage output shifts from 345mV to 492mV. V. C ONCLUSION We have described a novel adapting floating gate currentmode pixel for high quality imaging that has the ability to au- [1] O. Yadid-Pecht and R. Etienne-Cummings, CMOS imagers: from phototransduction to image processing. Boston, MA: Kluwer, 2004. [2] R. Etienne-Cummings, J. Van der Spiegel, P. Mueller, and M. Z. Zhang, “A foveated silicon retina for two-dimensional tracking,” IEEE TCAS.II, vol. 47, no. 6, pp. 504–517, June 2000. [3] S. Shah and S. Collins, “A temperature independent trimmable current source,” in IEEE ISCAS, vol. 1, May 2002, pp. I713–I716. [4] S. Jackson, J. Killens, and B. Blalock, “A programmable current mirror for analog trimming using single poly floating-gate devices in standard CMOS technology,” IEEE TCAS.II, vol. 48, no. 1, pp. 100–102, Jan. 01. [5] J. Hyde, T. Humes, C. Diorio, M. Thomas, and M. Figueroa, “A 300MS/s 14-bit digital-to-analog converter in logic CMOS,” IEEE JSSC, vol. 38, no. 5, pp. 734–740, May 2003. [6] P. Hasler, B. Minch, and C. Diorio, “An autozeroing floating-gate amplifier,” IEEE TCAS.II, vol. 48, no. 1, pp. 74–82, January 2001. [7] T. Constandinou, J. Georgiou, and C. Toumazou, “An auto-input-offset removing floating gate pseudo-differential transconductor,” in IEEE ISCAS, vol. 1, May 2003, pp. 169–172. [8] E. Wong, P. Abshire, and M. Cohen, “Floating gate comparator with automatic offset manipulation capability,” in IEEE ISCAS, vol. 1, May 2004, pp. I–529–532. [9] M. Cohen and G. Cauwenberghs, “Floating-gate adaptation for focalplane online nonuniformity correction,” IEEE TCAS.II, vol. 48, no. 1, pp. 83–89, January 2001. [10] P. Hasler and J. Dugger, “Correlation learning rule in floating-gate pFET synapses,” IEEE TCAS.II, vol. 48, no. 1, pp. 65–73, January 2001. [11] M. A. Karim, Electro-optical Devices and Systems. Boston, MA: PWSKent Pub. Co., 1990. [12] E. Vittoz and J. Fellrath, “CMOS analog integrated circuits based on weak inversion operations,” IEEE JSSC, vol. 12, no. 3, pp. 224–231, June 1977. 5317