Document 13299491

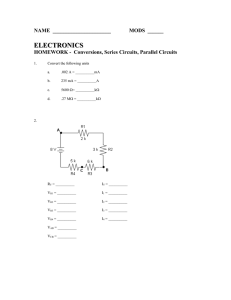

advertisement

A Note on Experiment N ◦ 7, EE2221 by Steve McFadden (s.mcfadden@uky.edu) In the circuit illustrated below the input signal has been increased to the point where the output wave form is clipped. This is referred to as saturation and occurs when the power supply voltage minus some internal saturation voltage is reached. It is a natural limit of the circuit. The output signal can not be driven beyond the power supply values. The question was raised what is happening that produces a voltage at the op-amp inverting input (VB ) while the output is in saturation. This can be evaluated using simple voltage division techniques. It is necessary to do this at instantaneous points in time. I’ve identified t1 , which occurs at the peak. See the series circuit of R1 and Rf . By inspection we see the total voltage developed across the series circuit is the difference between VO and Vi . Vi − VO = VR1 + VRf . Also: Vi = VR1 + VB . Or: VB = Vi − VR1 . For the voltage divider VR1 will be: VR1 = (Vi − VO )( R1 ) R 1 + Rf Therefore: VB = Vi − [(Vi − VO ) R1 ] R 1 + Rf After reorganizing this equation, we obtain: R Vi × Rf1 + VO VB = Rf R1 + 1 Plugging in the values given here, we obtain: VB = 1.98 × 100 10 + (−18.4) = 0.13 V. 100 10 + 1 Figure 1: What is happening in saturation? This is a predicted value using data given. It matches the measured value. Great care was taken in setting up the circuit and defining t1 so that the measured data was very accurate. The observation is VB is determined by the voltage divider and the voltage across it. As long as the opamp is not in saturation that voltage will resolve to zero. 1 This document was created on March 28, 2002. 1