Research Journal of Applied Sciences, Engineering and Technology 5(5): 1674-1680,... ISSN: 2040-7459; e-ISSN: 2040-7467

advertisement

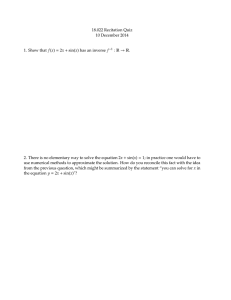

Research Journal of Applied Sciences, Engineering and Technology 5(5): 1674-1680, 2013 ISSN: 2040-7459; e-ISSN: 2040-7467 © Maxwell Scientific Organization, 2013 Submitted: July 24, 2012 Accepted: August 21, 2012 Published: February 11, 2013 Design of a Three-Phase Statcom-Based Inductive Static VAR Compensator Using DC Capacitor Voltage Control Scheme Abdulkareem Mokif Obais and Jagadeesh Pasupuleti Department of Electrical Power Engineering, Universiti Tenaga Nasional, Malaysia Abstract: In this study, a three-phase continuously controlled harmonic-free inductive static VAR compensator is presented. The compensator is built of a three-phase voltage source inverter based statcom. The phase currents of this compensator are linearly and continuously controlled by the statcom DC capacitor voltage. The control strategy is outlined by a process of forcing the capacitor voltage to follow a certain reference voltage which can be varied linearly from its maximum to its minimum values to produce balanced three-phase inductive currents varying in the range of zero to maximum value (IMAX). The proposed compensator was verified on the computer program PSpice. Keywords: Controlled reactors, power quality, reactive power control INTRODUCTION Static VAR compensators have significant impacts on power quality improvement. They are playing very important roles in voltage control, minimization of transmission losses, power factor improvement, stability of power systems and load balancing (Singh et al., 2008; Slepchenkov et al., 2011; Xu et al., 2010; Wolfle and Hurley, 2003; Peng, 1998). Both generation and absorption of reactor power are important in power quality improvement. Compensators employing switched-capacitors are harmonic-free static VAR generators and are characterized by stepping responses (Jintakosonwit et al., 2007). A Thyristor Controlled Reactor (TCR) is a continuously controlled static VAR absorber, but it generates wide spectrum of odd current harmonics, thus it needs harmonic filtration techniques (Yacamini and Resende, 1986; Haque and Malik, 1987). Mixing of fixed or switched-capacitors and TCR techniques, results in a compensator controlled in generation and absorption modes of operation and having the characteristics of both techniques (Haque and Mali, 1985). Power conversion based static VAR compensators are widely used nowadays in power quality improvement. A statcom is one of such compensators. It is either built using Voltage Source Inverter (VSI) shunted by a DC capacitor or Current Source Inverter (CSI) shunted by a DC reactor (Singh et al., 2008; Ye, 2005). Both exchange apparent power with the AC supply through small reactors. They are traditionally governed by angle control scheme which determines the mode of operation and the amounts of phase currents (Tavakoli Bina and Hamill, 2005). Both release harmonics and have real power contribution in the power system network (Filizadeh and Gole, 2005; Chen and Hsu, 2007). Many techniques were approached to minimize these harmonics such as traditional filtering techniques and multilevel technologies in statcom designs (Chen and Hsu, 2007; Hagiwara et al., 2012). In this study, a harmonic-free continuously and linearly controlled three-phase inductive static VAR compensator is presented. It is constructed of VSI-base statcom equipped with DC capacitor voltage control. The statcom draws pure inductive phase currents from the AC supply through to some extent small harmonic suppressing rectors. The currents can be varied linearly from zero to maximum value (IMAX) by varying the DC capacitor voltage from its maximum value to its minimum value. THE PROPOSED COMPENSATOR LAYOUT AND ANALYSIS The proposed three-phase inductive static VAR compensator is shown in Fig. 1. vA, vB and vC are the three-phase AC supply phase voltages. L and R are the self inductance resistance of the statcom reactors. The voltage source inverter is formed of the IBGT switching devices X1, X2, X3, X4, X5 and X6 which are equipped with the free-wheeling diodes D1, D2, D3, D4, D5 and D6. CDC is the statcom DC capacitor which its voltage is controlled directly by the IGBT S7. D7 is a freewheeling diode for S7. LD and RD are self inductance and resistance of the current limiting reactor for S7. DFW and CFW are offering free-wheeling path for the current of LD. The VSI is triggered by the sinusoidal pulse width modulation shown in Fig. 2. vMA, vMB and vMC are Corresponding Author: Abdulkareem Mokif Obais, Department of Electrical Power Engineering, Universiti Tenaga Nasional, Malaysia 1674 2 1 1 1 1 3 X3 X5 R L D7 3 A' X7 + 2 B' VDC - R CDC 2 LD DFW 3 iC 2 C' D4 X4 1 RD 3 N 0 1 R 1 L D6 CFW D2 3 1 1 VC C L D5 1 iB VB B X1 1 D3 3 A 3 iA VA D1 3 1 Res. J. Appl. Sci. Eng. Technol., 5(5): 1674-1680, 2013 X6 X2 Fig. 1: The proposed three-phase inductive static VAR compensator v MA v MC v MB vs 2.0V 0V -2.0V VX1 5.0V 2.5V 0V VX2 5.0V 2.5V 0V VX3 5.0V 2.5V 0V 0s 10ms Time 20ms Fig. 2: The voltage source inverter sinusoidal pulse width modulation triggering signals analogue signals in phase with vA, vB and vC respectively and running with them at the same angular frequency ω. vMA, vMB and vMC are representing the modulating signals and are given by: v MA kv A kV m sin t AM sin t (1) 2 2 (2) v MB kv B kV m sin t AM sin t 3 3 4 (3) 4 v MC kv C kV m sin t AM sin t 3 3 where, Vm : The amplitude of the phase voltage of the AC power system network Each of the three modulating signals will be compared with the carrier signal vS which is a triangular waveform of amplitude of AS and frequency of fS. The results of the three comparisons are VX1, VX3 and VX5 which are representing the triggering signals of the switching devices X1, X3 and X5 respectively. The triggering signals of the switches X4, X6 and X2 are the logic complements of VX1, VX3 and VX5 respectively. According to the triggering process specified in Fig. 2, 1675 Res. J. Appl. Sci. Eng. Technol., 5(5): 1674-1680, 2013 the inverter instantaneous output line voltages vA'B', vB'C' and vC'A' can be given by: v A' B ' VDC V X 1 V X 3 5 vMA vMB vMC +As 0 (4) t' vS -As v B 'C ' vC ' A ' V DC V X 3 V X 5 5 (5) V DC V X 5 V X 1 5 (6) VX1 0 If the carrier signal frequency fS is very much greater than the modulating signals frequency f which is equal to ω/2π, then at any ωt and within one repetition time TS of the carrier signal cycle, the modulating signals will appear as horizontal straight lines as shown in Fig. 3. Note that the sequence of appearance of these lines depends on ωt. The average values of vA'B', vB'C' and vC'A' within TS represent the inverter fundamental line voltages at the power system frequency f. In other words, the inverter fundamental line voltages can be given by: v A'B ' F t' t '5 1 1 3 ' ' v dt V dt V DC dt ' A'B ' DC TS 0 TS t '2 t '4 1 TS TS v B 'C ' dt ' 0 1 TS t '6 t '2 V dt ' V dt ' DC t ' DC t' 5 1 1 TS TS vC ' A'dt ' 0 1 TS t '6 t '3 V dt ' V dt ' DC t ' DC t' 4 1 +5V t' t' t'1 t'4 t'5 t'6 TS t'2 t'3 2 Fig. 3: The voltage source inverter triggering status at certain ωt and within one cycle of vS t '3 TS 4 T v MA 1 S m sin t 1 4 A S (12) t '4 TS 4 v 3 MA AS TS 3 m sin t 4 (13) t '5 TS 4 v 3 MB AS TS 4 2 3 m sin t 3 (14) t '6 TS 4 v 3 MC AS TS 4 4 3 m sin t 3 (15) where, m represents the inverter modulation index and is defined by: m (9) AM AS (16) Substituting for t'1 to t'6 in (7), (8) and (9) results in: where, (vA')F, (vB')F and (vC')F are the inverter fundamental phase voltages and t'1, t'2, t'3, t'4, t'5, t'6 can be determined from Fig. 3 as follows: v A 'B ' F t '2 VX 5 0 TS 2 (8) VDC t '1 t '3 t '4 t '6 vC ' F v A' F TS t '1 +5V (7) V DC t ' 2 t '1 t ' 6 t '5 v B ' F v C ' F TS vC ' A' F VX 3 0 TS t' 0 V DC t '3 t ' 2 t '5 t ' 4 v A' F v B ' F TS v B 'C ' F +5V TS 4 v MC T 4 1 S m sin t 1 A 4 3 S (10) TS 4 v MB T 2 1 S m sin t 1 3 AS 4 (11) 1676 mV DC 2 sin t sin t 3 2 (17) 3 mV DC sin t 2 6 v B 'C ' F mV DC 2 2 4 sin t sin t 3 3 3 mV DC sin t 2 2 (18) Res. J. Appl. Sci. Eng. Technol., 5(5): 1674-1680, 2013 VX1 7 8 VX4 8 VX3 8 96 U5D 8 74ACT04 +5V - 4 0 8 3 + U11A V-5V U12 A4N26 11 Q2N2222A VX5 8 + 10 13 U11B 12 -5V 0 LA 2 2mH 1 LB 2 2mH OUT U15 - U14 2 - 6 R54 22k 4 OUT 6 R49 22 V- 0 4 R45 22k A4N26 R52 10k N 0 0 3.46V X1 G1 CM300DY -24H D1 X3 R53 k7 1 Q2N3906Q21 R57 10k G3 k1 CM300DY -24H D3 X5 k7 + VDC - RC CDC 500uF 2 LD 200uH 0.05 CM300DY -24H OFFSET = 0 PP_AMPLITUDE = 622V G4 FREQ_HZ = 50Hz DELAY = 0 k4 DAMPING = 0 PHASE = -240 D7 G7 RB X4 CM300DY -24H D4 X6 G6 k6 CM300DY -24H 1 2mH CM300DY -24H X7 k5 0.05 2 V+ D5 G5 k3 D6 3 LC V7 15V 0 1 1 Q2N2222A Q2N2222A VREF R55 22k 3 vC OFFSET = 0 PP_AMPLITUDE = 622V FREQ_HZ = 50Hz DELAY = 0 DAMPING = 0 VC PHASE = -120 G7 R50 100 U16 V- iC VB R46 Q19 560 Q20 VDC controlling and driving driving circuit RA 0.05 +max998/mxm -5V V- iB vB +max998/mxm 0 CM300DY -24H 1 OFFSET = 0 PP_AMPLITUDE = 622V FREQ_HZ = 50Hz DELAY = 0 DAMPING = 0 PHASE = 0 R48 22k 2 R56 99.5k iA vA k6 X6 driving circuit +5V 3 R51 500 Voltage source inverter triggering circuit VA R44 22k 0 V9 5V 0 R40 1 Q2N3906Q18 R42 10k +5V 1 0 V6 15V k5 3 R43 99.5k 5V G6 R38 100 Q2N2222A 0 V+ V8 VS R32 Q14 560 Q2N2222A X5 driving circuit VS +5V U13 A4N26 R39 1 R47 500 V1 = -2 V2 = 2 TD = 0 TR = 1ms TF = 0.9999ms PW = 0.0001ms PER = 2ms R35 22k Q16 7 OUT 6 CLC428/CL - 4 V-5V U5F 74ACT04 R34 22 Q2N3906Q17 R41 10k V+ 5 G5 R37 100 V5 15V 0 +5V U5E 74ACT04 R31 Q13 560 Q2N2222A 1 OUT 2 CLC428/CL - 4 V-5V VS R30 22k Q15 3 2 6 V+ OUT U10 VX6 R29 22 VX2 +5V V+ +max998/mxm X4 driving circuit VX5 7 R33 VMC 309.2k 3 k4 Q2N3906Q12 R28 10k X3 driving circuit 7 U7B OUT 6 CLC428/CL - 4 V-5V k3 Q2N3906Q11 V+ + V4 15V R26 1 1 5 5 G4 R24 100 Q2N2222A 0 R25 1 R27 10k R21 Q8 560 Q2N2222A V3 15V 0 +5V U5C 74ACT04 U9 A4N26 Q2N2222A Q2N2222A 2 CLC428/CL - 4 V-5V R20 22k Q10 7 V-5V U8 A4N26 1 OUT R19 22 3 U7A G3 R23 100 1 + R18 Q7 560 3 3 R17 22k Q9 7 4 6 R16 22 VX6 V+ - VS R36 1.8k X2 driving circuit VX3 +5V V+ OUT U6 2 0 vC R14 10k +5V +max998/mxm k2 Q2N3906Q6 X1 driving circuit V+ R22 1.8k 7 7 R15 VMB 309.2k 3 R12 1 k1 X2 G2 k2 Power circuit of VDC-controlled three-phase statcom Fig. 4: The PSpice validation system of the proposed compensator 1677 RD 0.002 D2 V- DFW 3 32 4 74ACT04 vB + U2B OUT 6 CLC428/CL - 4 V-5V U5B V2 15V 0 R11 1 G2 R10 100 Q2N2222A 1 5 R7 Q2 560 Q2N2222A V1 15V Q2N3906Q5 R13 10k R6 22k Q4 U4 A4N26 Q2N2222A 0 VX1 R8 22 V+ U5A G1 R9 100 Q2N2222A +5V 74ACT04 R5 Q1 560 3 1 VS R4 22k Q3 U3 A4N26 1 U2A OUT 2 CLC428/CL - 4 V-5V V-5V R3 22 1 4 + 3 - 3 V+ 2 0 VX4 +5V 6 1 OUT U1 8 +max998/mxm V+ R2 1.8k VX2 +5V V+ vA R1 VMA 309.2k 3 1 CFW 100uF Res. J. Appl. Sci. Eng. Technol., 5(5): 1674-1680, 2013 v C ' A ' F mV DC 2 4 sin t sin t 3 (19) 3 mV DC 7 sin t 6 2 Solving (7), (8), (9), (17), (18) and (19) for (vA')F, (vB')F and (vC')F yields: mV DC sin t 2 v A ' F v B ' F mV DC 2 sin t 2 3 v C ' F (20) RESULTS AND DISCUSSION (21) mV DC 4 sin t 2 3 The system of Fig. 4 was tested on PSpice. The results of those tests are shown in Fig. 5, 6, 7 and 900V VDC 600V (22) vA vB vC 300V Assuming that (ωL)2 is very much greater than R2, VDC is kept constant within its adjusted value and the value of the reactor L is sufficient to suppress all the current harmonics running at the multiples of fS, then the compensator phase currents will pure reactive and can be given by: v v A ' F V 1 iA A Vm sin t DC sin t (23) L L 2 v v B ' F 1 2 V DC 2 sin t V m sin t iB B 3 2 3 L L (24) iC the carrier signal vS, thus an inductance of 2 mH for L was sufficient to suppress all current harmonics running at the multiples of fS. To produce pure reactive phase currents, the reactors self resistance R was chosen such that R2<< (ωL)2. The VSI was operated at a modulation index of 0.9. To produce three-phase balanced inductive current in the range of 0 to 200 A (peak values), according to (23), (24) and (25), the capacitor voltage VDC must be controlled linearly in the range of 690V to 400V. IMAX in this compensator is 200A (peak value). vC vC ' F 1 4 V DC 4 sin t V sin t 3 2 L L m 3 (25) The DC capacitor voltage VDC is controlled by the switching device S7. As VDC starts to rise above its adjusted value, S7 will be turned on causing the capacitor to discharge through the reactor LD. Once VDC becomes equal to its adjusted value, the discharging process will be terminated. 0V -300V 20ms 30ms V(VA) V(VB) 50ms V(V+,V-) 60ms 200A iC 0A iB iA -200A 20ms 30ms I(LA) I(LB) 40ms I(LC) Time 50ms 60ms Fig. 5: The compensator phase voltages and currents when VDC = 690V 900V VDC 600V vA vC vB 300V 0V -300V 20ms 30ms V(VA) V(VB) 40ms V(VC) Time 50ms V(V+,V-) 60ms 200A 100A PSPICE VALIDATION SYSTEM 40ms V(VC) Time iA iB iC 0A -100A A complete system of the proposed three-phase -200A statcom-based inductive static VAR compensator using 20ms 30ms 40ms 50ms 60ms DC capacitor voltage control scheme was designed on I(LA) I(LB) I(LC) PSpice as shown in Fig. 4. In this system a three-phase Time power system of 380 V, 50 Hz was chosen as the power supply of the proposed compensator. A triangular Fig. 6: The compensator phase voltages and currents when waveform of frequency fS of 3.33 KHz was chosen as VDC = 610V 1678 Res. J. Appl. Sci. Eng. Technol., 5(5): 1674-1680, 2013 60ms Fig. 8. These figures indicate that the compensator phase currents are pure inductive and having sinusoidal waveforms. The transient time required for these currents to be settled is directly proportional to VDC. The transient times in Fig. 5, 6, 7 and 8 are due to the times elapsed in charging the capacitor CDC. It is obvious that the compensator phase currents are balanced in phase and magnitudes. The magnitude of these currents was plotted against VDC as shown in Fig. 9. This figure verifies the linearity stated in (23), (24) and (25). 60ms CONCLUSION 900V VDC 600V vA vB 300V vC 0V -300V 20ms 30ms V(VA) V(VB) 40ms V(VC) Time 50ms V(V+,V-) 200A 100A iA iB iC 0A -100A -200A 20ms 30ms I(LB) I(LA) 40ms I(LC) Time 50ms Fig. 7: The compensator phase voltages and currents when VDC = 540V 600V VDC 400V vA vB vC 200V 0V -200V -400V 20ms 30ms V(VA) V(VB) 200A iA iB 40ms V(VC) Time 50ms V(V+,V-) 60ms iC REFERENCES 0A -200A 20ms 30ms I(LA) I(LB) 40ms I(LC) Time 50ms 60ms Fig. 8: The compensator phase voltages and currents when VDC = 400V Current amplitude in amperes 250 200 150 100 50 0 0 200 The linearity, continuous control, harmonics absence and no real power consumption of the proposed compensator were verified on PSpice which is a computer program representing a reliable replacement of real hardware. The compensator can be used in all applications requiring balanced reactive power absorption. Once the charging time for CDC is elapsed, the compensator will respond rapidly to any change in reactive power demand. Keeping VDC constant within its adjusted value, avoids the compensator to generate current harmonics running at the multiples of the AC supply fundamental frequency f. 400 VDC in volts Fig. 9: Phase current amplitude versus VDC 600 800 Chen, B.S. and Y.Y. Hsu, 2007. An analytical approach to harmonic analysis and controller design of a STATCOM. IEEE Trans. Power Delivery, 22(1): 423-432. Filizadeh, S. and A.M. Gole, 2005. Harmonic performance analysis of an OPWM-controlled STATCOM in network applications. IEEE Trans. Power Delivery, 20(2): 1001-1008. Hagiwara, M., R. Maeda and H. Akagi, 2012. Negativesequence reactive-power control by a PWM STATCOM based on A Modular Multilevel Cascade Converter (MMCC-SDBC). IEEE Trans. Ind. Appl., 48(2): 720-729. Haque, S.E. and N.H. Malik, 1987. Analysis and performance of a Fixed Filter-Thyristor Controlled Reactor (FF-TCR) compensator. IEEE Trans. Power Electron., 2(2): 303-309. Haque, S.E., N.H. Mali and W. Shepherd, 1985. Operation of a Fixed Capacitor-Thyristor Controlled Reactor (FC-TCR) power factor compensator. IEEE Trans. Power Ap. Syst., PAS104(6): 1385-1390. 1679 Res. J. Appl. Sci. Eng. Technol., 5(5): 1674-1680, 2013 Jintakosonwit, P., S. Srianthumrong and P. Jintagosonwit, 2007. Implementation and performance of an anti-resonance hybrid deltaconnected capacitor bank for power factor correction. IEEE Trans. Power Electron., 22(6): 2543-2551. Peng, F.Z., J.W. McKeever and D.J. Adams, 1998. A power line conditioner using cascade multilevel inverters for distribution systems. IEEE Trans. Ind. Appl., 34(6): 1293-1298. Singh, B., P. Jayaprakash and D.P. Kothari, 2008. ATconnected transformer and three-leg VSC based DSTATCOM for power quality improvement. IEEE Trans. Ind. Electron., 23(6): 2710-2718. Slepchenkov, M.N., K.M. Smedley and J. Wen, 2011. Hexagram-converter-based STATCOM for voltage support in fixed-speed wind turbine generation systems. IEEE Trans. Ind. Electron., 58(4): 1120-1131. Tavakoli Bina, M. and D.C. Hamill, 2005. Average circuit model for angle-controlled STATCOM. IEE Proc. Electr. Power Appl., 152(3): 653-659. Wolfle, W.H. and W.G Hurley, 2003. Quasi-active power factor correction with a variable inductive filter: Theory, design and practice. IEEE Trans. Power Electron., 18(1): 248-255. Xu, Y., L.M. Tolbert, J.D. Kueck and D.T. Rizy, 2010. Voltage and current unbalance compensation using a static var compensator. IET Power Electron., 3(6): 977-988. Yacamini, R. and J.W. Resende, 1986. Thyristor controlled reactors as harmonic sources in HVDC convertor stations and AC systems. IEE Proc-B, 133(4): 263-269. Ye, Y., M. Kazerani and V.H. Quintana, 2005. Currentsource converter based STATCOM: Modeling and control. IEEE Trans. Power Delivery, 20(2): 795-800. 1680