H E W L E T T - P A... L r x ) E D

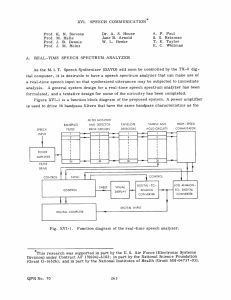

advertisement