Synthesis of a MSP430 Microcontroller Core using Multi-Voltage Techniques

advertisement

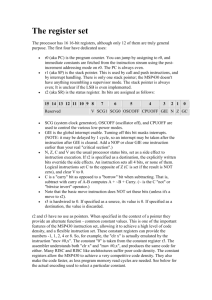

International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue7- July 2013 Synthesis of a MSP430 Microcontroller Core using Multi-Voltage Techniques M.Aravind kumar#1, Ch.V.V.S.Srinivas#2 , C.V.Pradeep Kumar Reddy#3,Abdul Rahaman shaik#4 , K.Ramesh Chandra#5 #1,2,3,5 Assistant Professor, Associate Professor#4 & ECE & JNTUK Vishnu Institute of Technology, Bhimavaram Andhra Pradesh, India Abstract— This paper describes regarding Implementation of Multi-Voltage low power techniques for power improvement. Here Multi-Voltage technique is applied to MSP430 16-bit microcontroller core victimization TSMC 65nm & 45nm NLDM libraries. The optimized power values area unit shown and compared among the libraries. Synopsys Power Compiler tool is employed for synthesis and implementing the Technique. Final outline and Conclusion provided is predicated on the results obtained much once implementation. Reports generated once synthesis state that there is 96.4% reduction in escape power and 26.7% reduction in dynamic power for 65nm NLDM library and 94.4% reduction in escape power and 37.8% reduction in dynamic power for 45nm NLDM library. Keywords— Multi-Voltage technique, TSMC, leakage power, MSP430. Dynamic power is that the energy consumed throughout logic transitions on nets, consisting of 2 elements, shift power and internal power. shift power results from the charging and discharging of the external electrical phenomenon load on the output of a cell. Internal power results from the short-circuit (crowbar) current that flows through the PMOS NMOS stack throughout a transition The cause of switching power is illustrated in Figure 1 I. INTRODUCTION With the growing popularity of portable devices, the consumers need for electronics has been focusing on delivering the right performance with right power with minimal power waste[1]. On the one hand, product specifications dictate their designs must consume minimum amounts of power to meet cost, reliability, and energy efficiency goals. Secondly, functional specifications imply that the ASICs must integrate more circuitry and run faster than ever to implement the desired functionality, which in turn drives up overall power consumption[2]. Fig. 1 Switching Power [2] As a result, a way to minimize power consumption whereas delivering the required performance and conjointly to extend battery period has become a significant concern and a crucial style goal that trendy chip designers should lookout. The total power for a design consists of dynamic power and static power. A. Dynamic Power ISSN: 2231-5381 http://www.ijettjournal.org Page 2779 International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue7- July 2013 II. PROBLEM STATEMENT In earlier generations of IC design technologies, the main parameters of concern were timing and area. Power consumption was a lesser concern. CMOS was considered a low-power technology, with fairly low power consumption at the relatively low clock frequencies used at the time, and with negligible leakage current. Fig. 2 Internal Power flow [2] In recent years, however, device densities and clock frequencies have increased dramatically in A. Static (Leakage) Power CMOS devices, thereby increasing the power consumption dramatically. At the same time, supply The main causes of leakage power are reverse- voltages and transistor threshold voltages have been bias p-n junction diode leakage, subthreshold lowered, causing leakage current to become a leakage, and gate leakage. These leakage paths in a significant problem. As a result, power CMOS inverter are shown in Figure 3 consumption levels have reached their maximum limits, and power has become as important as timing or area. In CMOS circuit in deep submicron (DSM) technology with increasing transistor count, clock frequency and with Transistor size continuously decreasing, leakage power is becoming as critical as dynamic power in many devices. Today low power design considerations as well as power estimation have become an integral part of the VLSI design technique and are impacting the same at all levels. Fig. 3 Leakage Currents [2] So Circuit techniques aimed at lowering leakage Leakage at reverse-biased p-n junctions (diode currents are therefore highly desirable [2]. leakage) has always existed in CMOS circuits. This Low power design is important from three leakage is relatively small. different reasons irrespective of design (i) Device Sub-threshold leakage is the small source-to- temperature (Failure rate, Cooling and packaging drain current that flows even when the transistor is costs) , (ii) Life of the battery (Meantime between held in the “off” state. Sub-threshold leakage charging, System cost) and (iii) Environment current increases exponentially as the gate voltage (Overall energy consumption)[3]. approach the threshold voltage. III. INTRODUCTION TO MULTI-VOLTAGE TECHNIQUE Gate leakage is the result of using an extremely thin insulating layer between the gate conductor and Dynamic power is proportional to VDD2 lowering the MOS transistor channel. VDD on selected blocks helps reduce power significantly. The most basic form of this approach is to partition the internal logic of the chip into ISSN: 2231-5381 http://www.ijettjournal.org Page 2780 International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue7- July 2013 multiple voltage regions or power domains, each with its own supply. This approach is called MultiVoltage design. It is based on the realization that in a modern SoC design, different blocks have IV. INTRODUCTION TO MSP430 CORE different performance objectives and constraints [3]. For example, the CPU and RAM blocks might need The MSP430 is a 16-bit RISC mixed-signal to be faster than a peripheral block. To get maximum speed and lower power at the same time, microcontroller core compatible with TI's MSP430 the CPU and RAM can operate with a higher supply family. voltage while the peripheral block operates with a lower voltage, as shown in Figure 4 Fig. 4 Multi-voltage chip design [3] Fig. 6 MSP430 core block diagram [4] A. Description of the block of MSP430 Where a logic signal leaves one power domain and enters another, if the voltages are significantly • Frontend: The module performs the different, a level-shifter cell is necessary to generate a signal with the proper voltage swing. Level instruction Fetch and Decode tasks.[4]. • Execution unit: Contains ALU and the shifters are the buffers that translate the signal from one voltage swing to another. Example shown in register file, the module executes the current decoded instruction [4]. Figure 5. • Serial Debug Interface: Contains all the required logic for a debugging unit. Communication with the host is done with a standard 8N1 serial interface[4]. • Memory backbone: This block performs a simple arbitration between the frontend and execution-unit [4]. • Basic Clock Module: Generates the ACLK and SMCLK enable signals[4]. Fig. 5 Power Versus Supply Voltage Example [3] • SFRs: The Special Function Registers block contain diverse configuration registers (NMI, Watchdog) [4]. • Watchdog: Although it is a peripheral, the watchdog is permanently included in the core because of its tight links with the NMI interrupts and the PUC reset generation[4]. ISSN: 2231-5381 http://www.ijettjournal.org Page 2781 International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue7- July 2013 V. IMPLEMENTATION OF MULTI-VOLTAGE Fig. 8 MSP430 with different power domains for 65nm library While implementing MSP430 core with 65nm library 3 power domains were created to reduce the power leakage and the power domains are showing in figure 8 with different colours. Fig. 7 Multi-Voltage implementation flow [5] After analysing the design we need to create power domains. The modules in the MSP430 are divided in to domains like memory and execution unit can be placed in high voltage and other modules can be placed in low voltage domain. The supply ports and nets are needed to be created. After creating the required supply ports and nets we need to assign the supply nets to required domain then they are connected to the ports. The main thing is to assign the primary power nets to each power Fig. 9 MSP430 with different power domains for 45nm library domain and to assign the required voltage value While implementing MSP430 core with 45nm (the voltages values can be found from the libraries). library 2 power domains were created to reduce the Finally we need to place the level shifters between power leakage and the power domains are showing the power domains and to find the cell area and in figure 9 with different colours. leakage power we can use the constraints and compile the design. After compiling the design if there are any violations in the area or leakage power we need to change constrains and recompile it and it there are no violations we can observe the power and area reports. This complete flow is implemented using Synopsys power compiler tool and with 65nm and 45nm multi-voltage libraries. ISSN: 2231-5381 http://www.ijettjournal.org Page 2782 International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue7- July 2013 VI. RESULTS The MSP430 core was targeted to 65nm and 45nm libraries. The result obtained before and after using multi-voltage low power technique is shown in form of Graphs and Tables. A. Results in form of Graphs Fig. 13 Graph showing leakage power results for MSP430 core when targeted to 45nm library B. RESULTS IN FORM OF TABLES Fig. 10 Graph showing dynamic power results for MSP430 core when targeted to 65nm library Dynamic Power µw Leakage Power µw Timing (slack met) ns Without MultiVoltage With MultiVoltage 20435.6 5462.1 318.5984 11.476 0.4 0.91 Table 1 Results obtained using 65nm Library for MSP430 Fig. 11 Graph showing leakage power results for MSP430 core when targeted to 65nm library Dynamic Power µw Leakage Power µw Timing (slack met) ns Without MultiVoltage With MultiVoltage 7973.6 3021.4 299.197 16.7048 0.4 0.86 Table 2 Results obtained using 45nm Library for MSP430 VII. CONCLUSION In this paper we have successfully designed MSP430 core according to specifications and implemented the multi-voltage technique for synthesis of MSP430 core using TSMC 65nm and 45nm libraries. Fig. 12 Graph showing dynamic power results for MSP430 core when targeted to 45nm library ISSN: 2231-5381 There is 96.4% reduction in leakage power and 26.7% reduction in dynamic power for TSMC 65nm library and 94.4% reduction in leakage power and 37.8% reduction in dynamic power for TSMC 45nm library. http://www.ijettjournal.org Page 2783 International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue7- July 2013 REFERENCES [5] User Guide. Synopsys Documentation Power Compiler Synopsys Online Design compiler. Synopsys Online [1] Meeta Srivastav, Prof. S.S.S.P. Rao, Himanshu Bhatnagar "Power Reduction Technique using Multi-vt libraries" [6] User Guide Synopsys Documentation [2] Synopsys Low-Power Documentation [7] http://www.tsmc.com/english/b_technology/b01_platform/b010101_45 nm.htm "45nm Technology-Technology for Tomorrow. [3] Michael Keating, David Flynn, Robert Aitken Alan Gibbons, Haitian Shi "Low Power Technique Manual for System-on-Chip Design". [8] http://www.tsmc.com/english/b_technology/b01_platform/b010101_65 nm.htm “65nm Technology” [4] Olivier GIRARD "openMSP430 an MSP430 clone...." Flow User Guide. Synopsys Online Author Details M ARAVIND KUMAR was born in A.P, India, and Completed M.Tech in VLSI System Design from BVRIT Engineering College, Hyderabad in the year of 2010 and B.E from SVH College of Engineering in the year 2005 in Electronics &Communication engineering. Presently working as an Assistant Professor in Vishnu Institute of Technology, Bhimavaram, A.P, India. His research interests in VLSI Design and low power techniques. Presently pursuing Ph.D from Gitam University. CH V V S SRINIVAS was born in A.P, India, Completed M.Tech in Communication Systems Engineering from S R K R Engineering College, Bhimavaram in the year of 2010 and B.E from S R K R Engineering College in the year 2006 in Electronics &Communication engineering. He worked as an Assistant professor in TRRCE and presently working as an Asst.Professor in Vishnu Institute of Technology, Bhimavaram ,A.P, India. His research interests in VLSI Design and communication systems. I born in AP, INDIA.I completed my B.E (ECE) from P B College of engineering (2007 passed out) and I completed my MTECH (EMBEDDED SYSTEMS) from SRM University, Chennai 2012 passed out. I am having 6years of teaching experience. Presently I am working as Assistant Professor in Vishnu Institute of Technology, Bhimavaram. Abdul Rahaman Shaik was born in A.P, India, and Completed M.Tech in VLSI System Design from NIIT Warangal in the year of 2010 and B.E from Sir C R Reddy Engineering College in the year 2000 in Electronics &Communication engineering. He worked as an Assistant professor in Sir C R Reddy Engineering College and presently working as an Assoc. Professor in Vishnu Institute of Technology, Bhimavaram, A.P, India. His research interests are in VLSI Design and Communication systems. Ramesh Chandra Kothapalli, born in A.P, India.Completed M.Tech from IIT Madras. B.Tech from R V R & J C College of Engineering, Guntur. Presently working as Asst.Prof.At Vishnu Institute of Technology,Bhimavaram.He has a Teaching Experience of three years. His Research work interests in Communications ISSN: 2231-5381 http://www.ijettjournal.org Page 2784