A Low-Cost Methodology for Soft Error Free Logic Circuits

advertisement

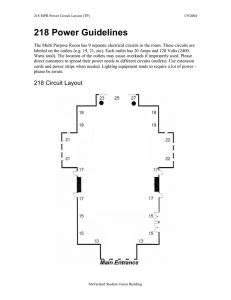

International Journal of Engineering Trends and Technology (IJETT) – Volume 22 Number 10 - April 2015 A Low-Cost Methodology for Soft Error Free Logic Circuits Sridevi Tumuluri 1, P.Sudhakar Rao 2 1 2 PG Student, Electronics & Communication Engineering, NOVA College of Engg & Tech., Vijayawada, A.P, India Associate Professor, Electronics & Communication Engineering, NOVA College of Engg & Tech., Vijayawada, A.P, India Abstract: Continuous scaling of the transistor size and reduction of the operating voltage has led to a significant performance improvement of integrated circuits. However, the vulnerability of the scaled circuits to transient data upsets or soft errors, which are caused by alpha particles and cosmic neutrons, has emerged as a major reliability concern. In this thesis, we have investigated the effects of soft errors in combinational circuits and proposed soft error detection techniques for high speed adders. In particular, we have proposed an area-efficient 64-bit soft error robust logarithmic adder (SRA). The proposed SRA is simulated for different operands with errors inserted at different nodes at the inputs, the carry merge tree, and the sum generation circuit. The simulation vectors are carefully chosen such that the SET is not masked by error masking mechanisms, which are inherently present in combinational circuits. Simulation results show that the proposed SRA is capable of detecting 77% of the errors. The undetected errors primarily result when the SET causes an even number of errors and when errors occur outside the sampling window. . Keywords — soft, error, logic circuits, low cost imperfections may be the result of manufacturing or they may occur during the lifetime of the chip from effects such as electro migration or oxide breakdown. Temporary failures, also called soft errors, are errors caused by cosmic rays or alpha particles. When a high energy particle (e.g., neutron, alpha particle, heavy ion) strikes a silicon substrate, it results in an ionization event. Such an event that can upset a data state is dependent upon several factors such as the energy of the incident particle, the location of the strike, the potential of the node, and the amount of charge collected. Such an event is referred to as a single event transient (SET). An SET leading to a false logic evaluation in a combinational circuit which is latched or an SET resulting in a bit flip in a memory cell, register, or flip-flop is called a soft error. The error is „soft‟ because if new data is written to the bit, it will be stored correctly. The term soft error is also called a single event upset (SEU). The rate at which soft errors occur is called the soft error rate (SER). The unit for measuring the SER and other reliability I. INTRODUCTION mechanisms is the failure in time (FIT). A FIT is The exponential growth in the number of transistors equivalent to one failure in 109 device hours. Ever on a chip has resulted in new obstacles. Technology increasing demand for high density and low power have scaling has resulted in more permanent failures of resulted in decreasing transistor size and smaller node devices and interconnects, and more temporary failures voltages. If uncorrected, failures due to soft errors can such as errors due to transients in the signalling and be higher than all the reliability mechanisms combined. storage of logic values. Permanent failures occur when With scaling, the node capacitance has decreased. In there is a physical imperfection in the chip. These order to keep the electric field constant, operating ISSN: 2231-5381 http://www.ijettjournal.org Page 480 International Journal of Engineering Trends and Technology (IJETT) – Volume 22 Number 10 - April 2015 voltage is scaled as well. Thus, the total charge required in a reverse biased junction. Electrons drift to higher to toggle a node from a particle induced transient potential of n-diffusion and the holes drift to the lower decreases. A recent work predicted that the SER per chip potential of p-diffusion. This sudden burst of charge of logic circuits will increase nine orders of magnitude collection results in a current pulse which can upset the from 1992 to 2011, and the impact of SER on data state. The higher the energy of the alpha particle, combinational logic will be comparable to that of the farther it travels into the substrate and more number unprotected memory elements of electron hole pairs it will generate. Consequently, the higher will be the peak of current pulse. For silicon, the range of a 10MeV particle is <100μm [Baumann05b]. In II. SOURCES OF SOFT ERRORS The main sources of soft errors are: alpha particles, high energy cosmic neutrons, and low energy neutrons. Electromagnetic interference can also cause soft errors by producing alpha-particles. Alpha particles are emitted from packaging materials and the interaction of thermal neutrons with the boron present in p-type semiconductors. An alpha particle, composed of two neutrons and two protons, is a doubly ionized helium atom emitted from the nuclear decay of unstable isotopes. The most common source of alpha particles is from naturally occurring 238U, 235U, and 232Th. These impurities emit alpha particles over a range of energies lead solders, 210Pb is chemically inseparable from 208Pb. 210Pb does not emit an alpha particle when it decays, however, due to short half life of 210Pb, growth of 212Po from 210Pb -7 210Bi -7 210Po -7 212Po is possible which has a very high alpha particle emission rate. The semiconductor manufacturing process and the packaging materials are purified to a point of diminishing returns. Soft error in logic circuits: An upset in the state of a logic circuit will not affect the computation unless it is latched into a memory element. Thus, a soft error in a combinational circuit is defined as a transient error which will be stored in a memory from 4 to 9 Mev. element. However, unlike in memory circuits there are several phenomena in logic circuits which can mask soft errors. An SEU at a node in a combinational circuit will not affect the output of the circuit when its result is determined by another input. The other input is called the controlling input. This can be better explained with the help of a NAND gate. Figure 1: Charge generation and collection by heavy ions The interaction of an alpha particle with the silicon substrate is electronic in nature. A particle travelling through the substrate creates electron hole pairs. Figure 1.1 shows the charge generation and the collection phase ISSN: 2231-5381 http://www.ijettjournal.org Page 481 International Journal of Engineering Trends and Technology (IJETT) – Volume 22 Number 10 - April 2015 The Redundancy Addition and Removal technique is based on the iterative addition and removal of redundancies. This technique has been proved to produce excellent results for combinational circuits, being the major advantages the low memory usage and Figure 2: Logical masking in NAND gate III. the short run times. Sequential logic optimization is also IMPLEMENTATION possible using this technique by considering sequential A new logic optimization method for sequential synchronous circuits is introduced. For this purpose the current main approaches, “Retiming and Resynthesis” and “Redundancy Addition and Removal” are considered. These techniques have some advantages and limitations that have been theoretically proven by several authors. The goal of the new optimization method is to combine these two techniques to get the best of each one. In particular the paper is focused on area optimization. The algorithm proposed in this paper redundancies. An example of Retiming and Resynthesis is shown in Fig. 3. The initial circuit has two registers and three combinational gates. The step of retiming reduces the number of registers to one, and produces the interaction between the combinational gates. The next step, resynthesis, allows the optimization to be done. The final circuit has only one register and only one gate. is efficient and delivers interesting optimization results. Digital circuit logic optimization has been a very important problem in the last decades. Obtaining a good optimized circuit is essential to get smaller and faster circuits. In particular, logic optimization for synchronous sequential circuits is still an open and challenging problem. There are two main approaches to sequential logic optimization, Retiming and Resynthesis (RaR) and Sequential Redundancy Addition and Removal (SRAR). The Retiming technique performs the optimization in two steps. The first step involves moving flip-flops across combinational gates (Retiming), and the second step is performed by optimizing the resulting Figure 3: Retiming and resynthesis example combinational blocks with combinational techniques (Resynthesis). The set of possible transformations that Retiming algorithms can be used for area or can be provided with Retiming and Resynthesis is timing optimization in sequential circuits. They are more limited. This method has become quite attractive despite suitable for timing optimization because they provide its limitations. the necessary steps to equilibrate critical paths between ISSN: 2231-5381 http://www.ijettjournal.org Page 482 International Journal of Engineering Trends and Technology (IJETT) – Volume 22 Number 10 - April 2015 memory elements in the circuit. This can be done by simple flip-flop movements. However, Retiming can also be used for area optimization. In this case the goal of the retiming algorithms is obtaining the circuit with minimum number of flipflops. Retiming and Resynthesis methods have been widely studied, and their optimization capabilities have been formally established by several authors. It has been done by relating transformations in the circuit made by retiming moves with the STG transformations. Given a machine implementation M1, corresponding to a state transition graph G, with a state assignment S1, it is always possible to derive a machine M2 corresponding to the same state transition graph G, and a state assignment S2 by applying only a series of Resynthesis and Retiming operations on M1. Theorem: Let M1 be an implementation corresponding to state assignment S1 and STG G1 and M2 be an implementation corresponding to state assignment S2 and STG G2. Then M2 can be obtained from M1 using only a sequence of Retiming and Resynthesis operations if and only if G1 and G2 are 1-step equivalent. These two theorems determine all the possible transformations Figure 4: Sequential Redundancy Addition and Removal with the Retiming methods. The first theorem shows the encoding capabilities of retiming. Every state IV. CONCLUSION codification in a FSM can be reached with retiming transformations. The second theorem characterizes the In this project Soft error correction may increase the set of possible transformations with retiming in the STG area but when compared to the error correction codes the of the circuit. It is important to observe that the retiming percent of increment is negligible. Constant working of set of possible transformations is only a subset of all the proposed method is not mandatory. References possible transformations in the circuit. This limitation of 1. retiming can be shown by some examples where the circuits cannot be optimized by only retiming and resynthesis operations. ISSN: 2231-5381 2. S. Krishnaswamy, S. M. Plaza, I. L. Markov, and J. P. Hayes, “Signature-based SER analysis and design of logic circuits,” IEEE Trans. Comput.-Aided Design Integr. Circuits Syst. (TCAD), vol. 28, no. 1, pp. 74–86, Jan. 2009. K. Bhattacharya, N. Ranganathan, and S. Kim, “A framework for correction of multi-bit soft errors in L2 cache based on redundancy,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 17, no. 2, pp. 194–206, Feb. 2009. http://www.ijettjournal.org Page 483 International Journal of Engineering Trends and Technology (IJETT) – Volume 22 Number 10 - April 2015 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. M. Nicolaidis, “Time redundancy based soft-error tolerance to rescue nanometer technologies,” in Proc. VLSI Test Symp. (VTS), 1999, pp.86–94. S. Krishnamohan and N. R. Mahapatra, “A highly-efficient technique for reducing soft errors in static CMOS circuits,” in Proc. Int. Conf. Comput. Design (ICCD), 2004, pp. 126–131. S.-C. Chang,M.Marek-Sadowska, and K.-T. Cheng, “Perturb and simplify: Multilevel boolean network optimizer,” IEEE Trans. Comput.- Aided Design Integr. Circuits Syst., vol. 15, no. 12, pp. 1494–1504, Dec. 1996. L. A. Entrena and K.-T. Cheng, “Combinational and sequential logic optimization by redundancy addition and removal,” IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 14, no. 7, pp.909–916, Jul. 1995. N. Miskov-Zivanov and D. Marculescu, “MARS-C: Modeling and reduction of soft errors in combinational circuits,” in Proc. Design Autom. Conf. (DAC), 2006, pp. 767–772. N. Miskov-Zivanov and D. Marculescu, “Circuit reliability analysis using symbolic techniques,” IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 25, no. 12, pp. 2638–2649, Dec. 2006. B. Zhang, W.-S. Wang, and M. Orshansky, “FASER: Fast analysis of soft error susceptibility for cell-based designs,” in Proc. Int. Symp. Quality Electron. Design (ISQED), 2006, pp. 755–760. M. Zhang and N. R. Shanbhag, “Soft-error-rate-analysis (SERA) methodology,” IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 25, no. 10, pp. 2140–2255, Oct. 2006. R. Ramanarayanan, V. Degalahal, R. Krishnan, J. S. Kim, V. Narayanan, Y. Xie, M. J. Irwin, and K. Unlu, “Modeling soft errors at the device and logic levels for combinational circuits,” IEEE Trans. Depend. Secure Comput., vol. 6, no. 3, pp. 202–216, Jul.–Sep. 2009. M. Omana, G. Papasso, D. Rossi, and C.Metra, “A model for transient fault propagation in combinational logic,” in Proc. Int. On-Line Test. Symp. (IOLTS), 2003, pp. 111–115. K. Bhattacharya and N. Ranganathan, “Reliability-centric gate sizing with simultaneous optimization of soft error rate, delay and power,” in Proc. Int. Symp. Low Power Electron. Design (ISLPED), 2008, pp. 99–104. K.-C. Wu and D. Marculescu, “Soft error rate reduction using redundancy addition and removal,” in Proc. Asia South Pacific Design Autom. Conf. (ASP-DAC), 2008, pp. 559–564. Q. Ding, Y.Wang, H.Wang, R. Luo, and H. Yang, “Output remapping technique for soft-error rate reduction in critical paths,” in Proc. Int. Symp. Quality Electron. Design (ISQED), 2008, pp. 74–77. ISSN: 2231-5381 Author’s Profile SRIDEVI TUMULURI 8019787996 P.SUDHAKAR RAO 9505235051 http://www.ijettjournal.org SRIDEVI TUMULURI is a PG student persuing her M.Tech in VLSI & ES specialization in NOVA College of Engg & Tech., Vijayawada. P.SUDHAKAR RAO is working as Associate Professor & Head of the Dept. Of ECE in NOVA College of Engg & Tech., Vijayawada. He has 10 years of teaching experience and 01 year of industrial experience. He has published 4 papers on his research work and guided so many PG students. Page 484