NatureVue™ Video Signal Processor with

Bitmap OSD, Dual HDMI Tx, and Encoder

ADV8003

Data Sheet

FEATURES

HDMI transmitters

Dual HDMI transmitters enabling splitter capability

Content type bits

CEC 1.4 controller

Audio return channel (ARC) support

Support of standard S/PDIF for stereo LPCM compressed

audio up to 192 kHz

6-channel uncompressed LPCM I2S audio up to 192 kHz

6-channel direct stream digital (DSD) audio inputs

Noise shaped video (NSV) six-DAC video encoder

Six 12-bit NSV video DACs

Multiformat video output support

Composite (CVBS), S-Video (Y/C), and Component YPrPb

(SD, ED, and HD)

Rovi Rev. 7.1.L1 (SD) and Rev. 1.4 (ED) compliant

Simultaneous SD and ED/HD operation

Professional video mode

Capability to output up to 36-bit TTL data

Video signal processor

Full 12-bit, 4:4:4 YUV internal processing

Motion adaptive de-interlacing with ultralow angle

interpolation

Multiple video processing paths

Upscaling to 4k × 2k (ADV8003KBCZ-8x models only)

Aspect ratio conversion/panorama scaling

Cadence detection for the recovery of original frames from

film-based content

Dual video scalers enable simultaneous output of multiple

different resolutions

Sharpness and detail enhancement

Noise reduction to reduce random, mosquito, and block

noise

Frame rate converter

Support for up to 3 simultaneous video streams, including

picture-in-picture (PiP) support

On-screen display (OSD)

Internally generated bitmap-based OSD allowing overlay

on one or more video outputs

Overlay on 3D video formats

Dedicated OSD scaler

Alpha blending of OSD data on video data

Disturbance free blending of OSD on either of 2 zones

Option of external OSD

Easy to use software tool for developing OSDs

APPLICATIONS

High-end A/V receivers

Upconverting DVD players/recorders

Blu-ray players/recorders

Set-top boxes

Video conferencing

Standalone video processors

HDMI splitters

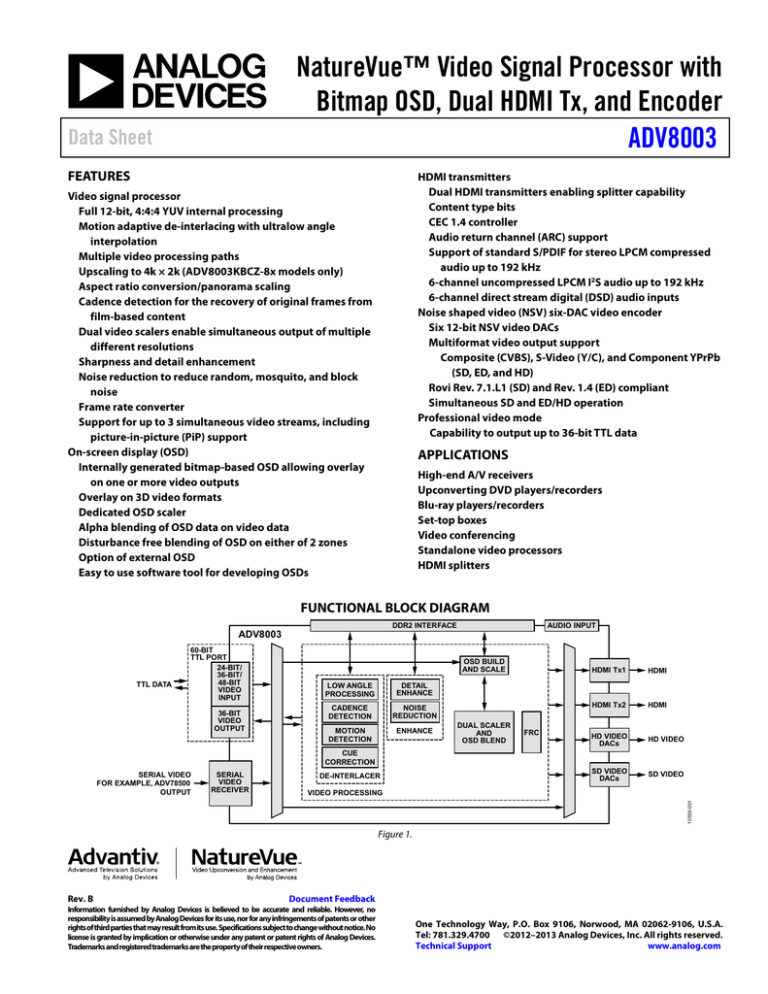

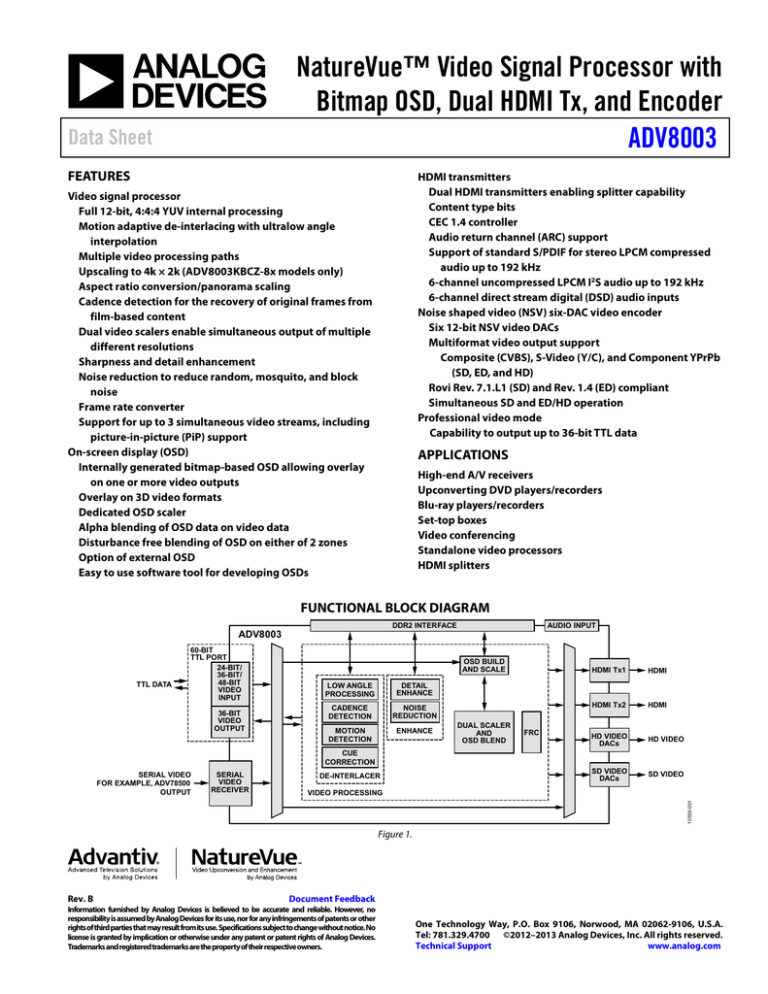

FUNCTIONAL BLOCK DIAGRAM

AUDIO INPUT

DDR2 INTERFACE

ADV8003

TTL DATA

60-BIT

TTL PORT

24-BIT/

36-BIT/

48-BIT

VIDEO

INPUT

36-BIT

VIDEO

OUTPUT

OSD BUILD

AND SCALE

LOW ANGLE

PROCESSING

DETAIL

ENHANCE

CADENCE

DETECTION

NOISE

REDUCTION

MOTION

DETECTION

ENHANCE

DUAL SCALER

AND

OSD BLEND

FRC

HDMI Tx1

HDMI

HDMI Tx2

HDMI

HD VIDEO

DACs

HD VIDEO

SD VIDEO

DACs

SD VIDEO

CUE

CORRECTION

SERIAL

VIDEO

RECEIVER

DE-INTERLACER

VIDEO PROCESSING

10556-001

SERIAL VIDEO

FOR EXAMPLE, ADV78500

OUTPUT

Figure 1.

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2012–2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

ADV8003

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Thermal Considerations............................................................ 59

Applications ....................................................................................... 1

Functional Overview...................................................................... 60

Functional Block Diagram .............................................................. 1

Video Input ................................................................................. 60

Revision History ............................................................................... 2

Flexible Digital Core .................................................................. 60

General Description ......................................................................... 3

Video Signal Processor (VSP) ................................................... 60

The ADV8003 Family .................................................................. 3

On-Screen Display (OSD) ......................................................... 61

Detailed Functional Block Diagram .............................................. 5

External DDR2 Memory ........................................................... 61

Specifications..................................................................................... 6

HDMI Transmitters ................................................................... 61

Electrical Characteristics ............................................................. 6

Video Encoder ............................................................................ 61

Analog Specifications ................................................................... 7

Professional Configuration ....................................................... 61

Data and I C Timing Characteristics ......................................... 8

Register Map Architecture ............................................................ 62

Absolute Maximum Ratings .......................................................... 18

Typical Applications Diagram ...................................................... 63

ESD Caution ................................................................................ 18

Outline Dimensions ....................................................................... 64

Pin Configuration and Function Descriptions ........................... 19

Ordering Guide .......................................................................... 64

2

Design Considerations ................................................................... 59

Power-Up Sequence ................................................................... 59

REVISION HISTORY

8/13—Revision B: Initial Version

Rev. B | Page 2 of 64

Data Sheet

ADV8003

GENERAL DESCRIPTION

The ADV8003 is a multiple input video signal processor that can

de-interlace and scale SD, ED, or HD video data to HD formats;

generate a bitmap on-screen display (OSD); and output the video

with OSD overlaid on two High Definition Multimedia Interface

(HDMI®) transmitters and a video encoder.

Video can be input into the ADV8003 in a number of ways:

using the 48-bit TTL pixel port, using the 24-bit external OSD

TTL pixel port, or from a device with an HDMI transmitter such

as the ADV7850. The ADV8003 supports many of the formats

outlined in the CEA-861 and VESA specifications, as well as

several other widely used timing formats.

Using two external DDR2 memories, the ADV8003 can perform

high performance, motion adaptive interlaced to progressive

conversion on SD and HD content. Using a single DDR2 memory,

the HD de-interlacing is limited to intrafield.

The ADV8003 features primary and secondary video scalers

that enable simultaneous output of multiple different resolutions.

The primary video scaler of the ADV8003KBCZ-8/8B/8C models

is capable of upscaling to 4k × 2k format and downscaling from

1080p. The primary video scaler of the ADV8003KBCZ-7/

ADV8003KBCZ-7B/ADV8003KBCZ-7C/ADV8003KBCZ-7T

models is capable of upscaling and downscaling to and from a

1080p format. The secondary video scaler facilitates up-scaling to

1080p and downscaling to 480p. Detail enhancement and image

enhancing techniques such as random, mosquito, and block noise

reduction allow for improved final image quality. The frame rate

converter of the ADV8003 allows the conversion between

common frame rates with support to output two different frame

rates simultaneously under certain conditions.

DDR2

INTERFACE

60-BIT

INPUT

VIDEO

48-BIT

INPUT

1080p (OSD)

HDMI Tx2

1080i (OSD)

HD VIDEO

DACs

720p (OSD)

SD VIDEO

DACs

480i

The ADV8003 can accept OSD information from an external OSD

source on the 24-bit external OSD TTL pixel data input or can

internally generate a high quality, bitmap-based OSD. The internal

OSD is highly flexible and allows the system designer to easily

incorporate features like scrolling text and animation in various

color depths up to 24-bit true color.

Analog Devices, Inc., provides an OSD development tool (Blimp)

to assist in the design, debug, and emulation of the OSD prior

to integration with the system application. When the design is

complete, the OSD development tool automatically generates

code to which system APIs can be added before integration with

the system application and an OSD design resource, which must

be downloaded to an external SPI flash memory.

Video can be output from the ADV8003 using one or both of the

HDMI transmitters and/or the 6-DAC SD/HD video encoder. The

flexible multiplexing allows simultaneous output on the HDMI

transmitters and HD formats on the HD DACs (for example,

1080p) with SD formats on the SD DACs (for example, 480i).

Both of the HDMI transmitters on the ADV8003 support all

mandatory and many optional 3D video resolutions and audio

return channels (ARC). Each transmitter also features a full

CEC master. The ADV8003 can receive up to six channels of I2S,

S/PDIF, direct stream digital (DSD), and high bit rate (HBR).

The six 12-bit NSV® video DACs allow for composite (CVBS),

S-Video (Y/C), and component (YPrPb) analog outputs in

standard, enhanced, and high definition video formats. Oversampling of 216 MHz (SD and ED) and 297 MHz (HD) removes

the requirement for external output filtering.

The ADV8003 can also support 30-bit TTL in mode and 30-bit

TTL out mode for professional applications, which do not require

the use of HDMI.

The ADV8003 supports the I2C protocol for communication

with the system microcontroller.

DIGITAL

CORE

THE ADV8003 FAMILY

10556-002

480i VIDEO

FROM

DECODER

HDMI Tx1

channels, or displaying OSD on multiple outputs of different

resolutions.

Figure 2. Sample Multiple Output Configuration

The ADV8003 has a flexible digital core that allows the user to

configure the part in several different modes; for example, using

a single video processing channel, using dual video processing

There are a number of derivatives within the ADV8003 family,

each featuring different capabilities; all are provided in the same

19 mm × 19 mm, 425-ball CSP_BGA package (see Table 1).

Note that the functionality of the ADV8003KBCZ-8 is

described throughout this data sheet. Some sections are not

relevant to other models because not all of the blocks found in

the ADV8003KBCZ-8 are included in those models. Table 1

lists the functionality for each model.

Rev. B | Page 3 of 64

ADV8003

Data Sheet

Table 1. Features Sets of the ADV8003 Family ICs

Part Number

ADV8003KBCZ-8 1

ADV8003KBCZ-8B

ADV8003KBCZ-8C

ADV8003KBCZ-71

ADV8003KBCZ-7B

ADV8003KBCZ-7C

ADV8003KBCZ-7T

1

Maximum

Data Rate

3 Gbps

3 Gbps

3 Gbps

2.25 Gbps

2.25 Gbps

2.25 Gbps

2.25 Gbps

Maximum Video Format

4k × 2k at 30 Hz (8-bit)

4k × 2k at 30 Hz (8-bit)

4k × 2k at 30 Hz (8-bit)

UXGA (162 MHz)

UXGA (162 MHz)

UXGA (162 MHz)

UXGA (162 MHz)

HDMI TX

Outputs

2

1

2

2

1

2

0

Analog Outputs

Six 12-bit DACs

No

No

Six 12-bit DACs

No

No

No

Rovi

Output

Yes

No

No

Yes

No

No

No

VSP

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Rovi enabled ICs require the buyer to be an approved licensee (authorized buyer) of ICs that are capable of outputting Rovi compliant video.

Rev. B | Page 4 of 64

OSD

Yes

Yes

Yes

Yes

Yes

Yes

Yes

TTL

Out

Yes

No

No

Yes

No

No

Yes

VS

Figure 3. ADV8003KBCZ-8

Rev. B | Page 5 of 64

DDR_DQ[31:0]

RESET

GENERATION

AND POWER

MANAGEMENT

TOP LEVEL

CONTROL

CLOCK

GENERATION

RECEIVER

POWER

SUPPLY

DETAIL

ENHANCEMENT

CUE

CORRECTION

FRAME

RATE

CONVERTER

SCALER 2

SCALER 1

SCALING AND

FRAME RATE

CONVERSION

HEAC

ARC PORT

VIDEO PROCESSING AND OSD BLENDING

BLOCK

NOISE

REDUCTION

LOW ANGLE

PROCESSING

CADENCE

DETECTION

MOSQUITO

NOISE

REDUCTION

MOTION

DETECTION

VIDEO

ENHANCEMENT

RANDOM

NOISE

REDUCTION

DE-INTERLACER

AND CADENCE

DETECTION

SPI

SLAVE

I2C SLAVE

I/O, OSD, ENCODER

VSP, HDMI Tx

REGISTER MAPS

SPI

MASTER

OSD

SCALER

BITMAP OSD

CONTROLLER

OSD

GENERATION

CONTROL

OSD VIDEO

BLEND

DDR_VREF

INT0

INT1

INT2

XTALP

XTALN

RX_0 P

RX_0N

RX_1 P

RX_1N

RX_2 P

RX_2N

RX_C P

RX_CN

RX_HPD

RX_5V

PCLK

DE

DIGITAL

VIDEO

CAPTURE

AND

FORMATTING

DDR_RAS

HS

OSD VIDEO

CAPTURE

AND

FORMATTING

DDR_CS

P[35:0]

OSD_DE

OSD_CLK

OSD_IN[12]

OSD_VS

COLOR SPACE

CONVERSION

UPDITHER

TO VBI INSERTION IN

ENCODER BLOCK

DDR_WE

OSD_HS

OSD_IN[23:16]/

OSD_IN[11:0]/

EXT_DIN[7:0]

DDR_DQS[3:0]

SPI SLAVE

DDR_DQS[3:0]

OSD_IN[15:13]/

VBI_x

DDR_DM[3:0]

COLOR SPACE

CONVERSION

UPDITHER

DDR_BA[2:0]

COLOR SPACE

CONVERSION

UPDITHER

DDR_A[12:0]

VIDEO MUXING

DDR_CAS

DDR2 INTERFACE

DDR_CK

VBI DATA SERVICE

INSERTION

PROGRAMMABLE

CHROMINANCE

FILTERS

PROGRAMMABLE

LUMINANCE

FILTERS

SHARPNESS AND

ADAPTIVE FILTER

CONTROL

HDCP

ENCRYPTION

SUBCARRIER

FREQ LOCK

SIN/COS

MODULATION/COS

SYNC

INSERTION

ENCODER

4:2:2

4:4:4

AND

COLOR SPACE

CONVERTER

HDMI Tx

VIDEO DATA

CAPTURE

PROGRAMMABLE

HDTV FILTERS

4:2:2

4:4:4

AND

COLOR SPACE

CONVERTER

REFERENCE

AND CABLE

DETECTION

12-BIT

DAC6

12-BIT

DAC5

12-BIT

DAC4

12-BIT

DAC3

12-BIT

DAC2

12-BIT

DAC1

TMDS

OUTPUTS

HDCP

KEYS

TMDS

OUTPUTS

HDCP

KEYS

MASTER

I2C

CEC

CONTROL

HDCP

ENCRYPTION

HDCP AND EDID

UNCONTROLLER

AUDIO DATA CAPTURE

HDMI Tx

VIDEO DATA

CAPTURE

ED/HD

PROCESSOR

DDR_CK

MULTIPLEXER

MCLK

16×/4× OVERSAMPLING FILTERS

SCLK

SD

PROCESSOR

DSD_CLK

2 × PLLs

AUD_IN[5:0]

DDR2 CONTROLLER INTER FACE

DAC6

DAC5

DAC4

DAC3

DAC2

DAC1

TX2_0+

TX2_0–

TX2_1+

TX2_1–

TX2_2+

TX2_2–

TX2_C+

TX2_C–

TX1_0+

TX1_0–

TX1_1+

TX1_1–

TX1_2+

TX1_2–

TX1_C+

TX1_C–

HPD_TX1

HPD_TX2

DDC1_SC L

DDC1_SD A

DDC2_SC L

DDC2_SD A

CEC2

CEC1

Data Sheet

ADV8003

DETAILED FUNCTIONAL BLOCK DIAGRAM

COMPx

RSETx

VREF

ELPFx

SFL

ALSB

SCL

SDA

CS2

SCK2

MISO2

MOSI2

CS1

SCK1

MISO1

MOSI1

HEAC_1+

HEAC_1–

HEAC_2+

HEAC_2–

ARC1_OUT

ARC2_OUT

DVDD_IO

PVDD_DDR

DVDD_DDR

AVDDx

CVDD1

PVDDx

DVDD

PDN

RESET

10556-003

ADV8003

Data Sheet

SPECIFICATIONS

Measured at DVDD = 1.746 V to 1.854 V, DVDD_DDR = 1.746 V to 1.854 V, PVDD1 = 1.746 V to 1.854 V, PVDD2 = 1.746 V to 1.854 V,

PVDD3 = 1.746 V to 1.854 V, PVDD5 = 1.746 V to 1.854 V, PVDD6 = 1.746 V to 1.854 V, PVDD_DDR = 1.746 V to 1.854 V, AVDD3 =

1.746 V to 1.854 V, CVDD1 = 1.746 V to 1.854 V, AVDD1 = 3.20 V to 3.40 V, AVDD2 = 3.20 V to 3.40 V, DVDD_IO = 3.20 V to 3.40 V,

TMIN to TMAX = 0°C to 70°C, unless otherwise noted.

ELECTRICAL CHARACTERISTICS

Table 2.

Parameter

STATIC PERFORMANCE

Resolution (Each DAC)

Integral Nonlinearity, +ve 1

Integral Nonlinearity, −ve1

Differential Nonlinearity, +ve 2

Differential Nonlinearity, −ve2

DIGITAL INPUTS

Input High Voltage

Symbol

Test Conditions/Comments

N

INL

INL

DNL

DNL

DAC outputs sampled at 500 kHz

DAC outputs sampled at 500 kHz

DAC outputs sampled at 500 kHz

DAC outputs sampled at 500 kHz

VIH

Input Low Voltage

VIL

Input Leakage Current

IIN

Input Capacitance

DIGITAL INPUTS (5 V TOLERANT)

Input High Voltage

Input Low Voltage

Input Leakage Current

DIGITAL OUTPUTS

Output High Voltage

Output Low Voltage

High Impedance Leakage Current

Output Capacitance

POWER REQUIREMENTS 3, 4, 5

Digital Power Supply

PLL Analog Supply

PLL Digital Supply

Encoder PLL Supply

HDMI Tx1 PLL Power Supply

HDMI Tx2 PLL Power Supply

HDMI Analog Power Supply

Comparator Power Supply

HDMI Rx Inputs Analog Supply

Encoder Analog Power Supply

Digital Interface Supply

Digital Power Supply Current, Including

DVDD_DDR and PVDD_DDR

Min

HEAC inputs

DDR_DQS inputs

Other digital inputs

13

VOH

VOL

ILEAK

COUT

2.4

DVDD

PVDD1

PVDD2

PVDD3

PVDD5

PVDD6

AVDD3

CVDD1

AVDD1

AVDD2

DVDD_IO

IDVDD

1.746

1.746

1.746

1.746

1.746

1.746

1.746

1.746

3.20

3.20

3.20

PLL Digital Supply Current

IPVDD2

V

0.3 ×

DVDD_IO

±60

±60

±10

3.4

0.8

±60

0.4

±10

13

Mode 1

1.8

1.8

1.8

1.8

1.8

1.8

1.8

1.8

3.3

3.3

3.3

1989.0

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

1423.0

60.6

23.0

21.0

1.3

21.8

19.9

0.2

Rev. B | Page 6 of 64

Unit

Bits

LSB

LSB

LSB

LSB

0.7 ×

DVDD_IO

VIH

VIL

IIN

IPVDD1

Max

12

0.389

−0.322

0.183

−0.208

CIN

PLL Analog Supply Current

Typ

1.854

1.854

1.854

1.854

1.854

1.854

1.854

1.854

3.40

3.40

3.40

V

µA

µA

µA

pF

V

V

µA

V

V

µA

pF

V

V

V

V

V

V

V

V

V

V

V

mA

mA

mA

mA

mA

mA

mA

mA

mA

Data Sheet

Parameter

Encoder PLL Supply Current

ADV8003

Symbol

IPVDD3

HDMI Tx1 PLL Supply Current

IPVDD5

HDMI Tx2 PLL Supply Current

IPVDD6

HDMI Analog Power Supply Current

IAVDD3

Comparator Power Supply Current

ICVDD1

HDMI Rx Inputs Analog Supply Current

IAVDD1

Encoder Analog Power Supply

IAVDD2

Digital Interface Supply Current

IDVDD_IO

Test Conditions/Comments

Mode 1

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

Mode 1

Mode 2

Power-down mode

Min

Typ

8.9

3.8

0.0

62.2

49.3

1.8

62.5

2.1

1.6

52.9

19.7

3.6

76.1

69.6

1.1

62.3

56.8

6.3

36.2

9.2

1.9

1.14

1.93

0.1

Max

Unit

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

Integral nonlinearity (INL) measures the deviation of the actual DAC transfer function from the ideal. For +ve INL, the actual line lies above the ideal line value. For −ve INL,

the actual line lies below the ideal line value.

2

Differential nonlinearity (DNL) measures the deviation of the actual DAC output voltage step from the ideal. For +ve DNL, the actual step value lies above the ideal

step value. For −ve DNL, the actual step value lies below the ideal step value.

3

Mode 1 involves a 1080i60 input to the ADV8003 receiver and a 720p60 input to the ADV8003 TTL external OSD input. Both inputs are run through the front-end color

space converters. The 1080i60 video stream is de-interlaced and upscaled to 4k × 2k at 24 Hz. The 720p video stream is input to the OSD block and is blended onto the

4k × 2k at 24 Hz video stream using the OSD block scaler. Both HDMI transmitters are then driven using the 4k × 2k at 24 Hz output.

4

Mode 2 involves a 1080i60 input to the ADV8003 receiver. This input is run through the front-end color space converter. The 1080i60 video stream is de-interlaced and

is output to HDMI Transmitter 1. The secondary VSP is used to convert the 1080p video stream to 480i and is output using the SD encoder.

5

In the power-down mode, the ARC and the internal clock tree are kept active.

1

ANALOG SPECIFICATIONS

Table 3.

Parameter

Low Drive Output Current (Full Scale)

DAC-to-DAC Matching

Output Compliance, VOC

Output Capacitance, COUT

DAC Analog Output Skew

Test Conditions/Comments

RSET = 4.12 kΩ, RL = 300 Ω

DAC1 to DAC6

Min

3.95

Typ

4.3

0.9

0

DAC1, DAC2, DAC3

DAC4, DAC5, DAC6

DAC1 to DAC6

Rev. B | Page 7 of 64

Max

4.5

1.4

9

9

0.2

Unit

mA

%

V

pF

pF

ns

ADV8003

Data Sheet

DATA AND I2C TIMING CHARACTERISTICS

For input timing measurements, VIH = DVDD_IO and VIL = GND.

Table 4.

Parameter

TMDS CLOCK

TMDS Input Clock Frequency

Symbol

TMDS Output Clock Frequency

CLOCK AND CRYSTAL

Crystal Frequency, XTAL

Crystal Frequency Stability

Primary Video Input Clock Frequency Range

Secondary Video Input Clock Frequency Range

Video Output Clock Frequency Range

Serial Port 1 SCK Frequency (SCK1)

Serial Port 2 SCK Frequency (SCK2)

Serial Port 3 SCK Frequency (VBI_SCK)

Audio SCLK Frequency

Audio MCLK Frequency

Audio DSD Clock Frequency

FAST I2C PORTS 1

SCL Frequency

SCL Minimum Pulse Width High

SCL Minimum Pulse Width Low

Start Condition Hold Time

Start Condition Setup Time

SDA Setup Time

SCL and SDA Rise Time

SCL and SDA Fall Time

Stop Condition Setup Time

SERIAL PORT 2, 3

Master Serial Port (Serial Port 2)

CS2 Falling Edge to SCK2 Rising/Falling Edge

Test Conditions/Comments

Min

ADV8003KBCZ-8,

ADV8003KBCZ-8B,

ADV8003KBCZ-8C

ADV8003KBCZ-7,

ADV8003KBCZ-7B,

ADV8003KBCZ-7C,

ADV8003KBCZ-7T

ADV8003KBCZ-8,

ADV8003KBCZ-8B,

ADV8003KBCZ-8C

ADV8003KBCZ-7,

ADV8003KBCZ-7B,

ADV8003KBCZ-7C,

ADV8003KBCZ-7T

Typ

Max

Unit

25

297

MHz

25

225

MHz

25

297

MHz

25

225

MHz

±50

162

162

162

50

81

27

49.152

98.304

5.6448

MHz

ppm

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

27

13.5

13.5

13.5

11.5

400

t1

t2

t3

t4

t5

t6

t7

t8

t9, t10

SCK2 Rising/Falling Edge to CS2 Rising Edge

t11, t12

CS2 Pulse Width

SCK2 High Time

t13

t14

600

1.3

600

600

100

300

300

0.6

t9, t10, depending on the

values of CPHA and CPOL

t11, t12, depending on the

values of CPHA and CPOL

SCK2 Low Time

1 × SCK2

periods

1 × SCK2

periods

1880

0.45 × SCLK2

periods

0.45 × SCLK2

periods

Rev. B | Page 8 of 64

1.5 × SCLK2

periods

1.5 × SCLK2

periods

1900

0.55 ×

SCLK2

periods

0.55 ×

SCLK2

periods

kHz

ns

µs

ns

ns

ns

ns

ns

µs

ns

ns

ns

%

duty

cycle

%

duty

cycle

Data Sheet

Parameter

MOSI2 Start of Data Invalid to SCK2 Falling Edge

CS2 Start of Data Invalid to SCK2 Falling

Edge

SCK2 Falling Edge to MOSI2 End of Data Invalid

SCK2 Falling Edge to CS2 End of Data Invalid

MISO2 Setup Time

ADV8003

Symbol

t15

t15

Test Conditions/Comments

SPI Mode 0, SPI Mode 3

SPI Mode 0, SPI Mode 3

t16

t16

t17

SPI Mode 0, SPI Mode 3

SPI Mode 0, SPI Mode 3

Valid regardless of the

SCK2 active edge used

Valid regardless of the

SCK2 active edge used

SPI Mode 1, SPI Mode 2

SPI Mode 1, SPI Mode 2

SPI Mode 1, SPI Mode 2

SPI Mode 1, SPI Mode 2

Valid regardless of the

SCK2 active edge used

Valid regardless of the

SCK2 active edge used

MISO2 Hold Time

t18

MOSI2 Start of Data Invalid to SCK2 Rising Edge

CS2 Start of Data Invalid to SCK2 Rising Edge

SCK2 Rising Edge to MOSI2 End of Data Invalid

SCK2 Rising Edge to CS2 End of Data Invalid

MISO2 Setup Time

t19

t19

t20

t20

t21

MISO2 Hold Time

t22

Slave Mode (Serial Port 1)

CS1 Falling Edge to SCK1 Rising/Falling Edge

t23, t24

SCK1 Rising/Falling Edge to CS1 Rising Edge

t25, t26

CS1 Pulse Width

t27

SCK1 High Time

t30

Max

1.15

0.81

Unit

ns

ns

1.85

2.14

14.57

ns

ns

ns

0.0

ns

1.59

1.24

1.39

1.68

14.57

ns

ns

ns

ns

ns

0.0

ns

t31

t32

t33

SPI Mode 0, SPI Mode 3

SPI Mode 0, SPI Mode 3

SPI Mode 0, SPI Mode 3

t34

t35

t36

t37

t38

SPI Mode 0, SPI Mode 3

SPI Mode 1, SPI Mode 2

SPI Mode 1, SPI Mode 2

SPI Mode 1, SPI Mode 2

SPI Mode 1, SPI Mode 2

t39

ns

50.0

ns

0.55 × SCK1

periods

0.45 × SCK1

periods

0.55 × SCK1

periods

0.15

1.4

5.89

12.08

0

1.96

5.79

11.97

0.45 ×

VBI_SCK

periods

0.45 ×

VBI_SCK

periods

0.55 ×

VBI_SCK

periods

0.55 ×

VBI_SCK

periods

5×

VBI_SCK

periods

SPI Mode 0 only

SPI Mode 0 only

Rev. B | Page 9 of 64

ns

0.45 × SCK1

periods

VBI_CS Pulse Width

t40

t41

50.0

5 × SCK1

periods

VBI_SCK Low Time

VBI_CS, VBI_MOSI Setup Time

VBI_CS, VBI_MOSI Hold Time

Typ

t23, t24, depending on the

values of CPHA and CPOL

t25, t26, depending on the

values of CPHA and CPOL

SCK1 Low Time

MOSI1 Setup Time

MOSI1 Hold Time

SCK1 Falling Edge to MISO1 Start of Data

Invalid

SCK1 Falling Edge to MISO1 End of Data Invalid

MOSI1 Setup Time

MOSI1 Hold Time

SCK1 Rising Edge to MISO1 Start of Data Invalid

SCK1 Rising Edge to MISO1 End of Data Invalid

Slave Mode (Serial Port 3)

VBI_SCK High Time

Min

0.93

0.75

%

duty

cycle

%

duty

cycle

ns

ns

ns

ns

ns

ns

ns

ns

%

duty

cycle

%

duty

cycle

ns

ns

ns

ADV8003

Parameter

SPI Pass-Through Mode

Data Transition on SCK1 to Start of Data

Invalid on SCK2

Data Transition on SCK1 to End of Data Invalid

on SCK2

Data Transition on MOSI1 to Start of Data

Invalid on MOSI2

Data Transition on MOSI1 to End of Data Invalid

on MOSI2

Data Transition on MISO2 to Start of Data

Invalid on MISO1

Data Transition on MISO2 to End of Data Invalid

on MISO1

Data Transition on CS1 to Start of Data

Invalid on CS2

Data Transition on CS1 to End of Data Invalid

on CS2

RESET FUNCTION

Reset Pulse Width

VIDEO DATA AND CONTROL INPUTS3

PCLK High Time

Data Sheet

Symbol

Test Conditions/Comments

Max

Unit

t42

5.17

ns

t43

10.20

ns

t42

4.90

ns

t43

10.85

ns

t42

5.29

ns

t43

11.97

ns

t42

4.61

ns

t43

8.78

ns

t44

ms

0.45 × PCLK

period

0.55 × PCLK

period

0.45 × PCLK

period

0.55 × PCLK

period

0.55 ×

OSD_CLK

period

0.55 ×

OSD_CLK

period

t45

0.45 ×

OSD_CLK

period

0.45 ×

OSD_CLK

period

1.42

t46

0.95

ns

t47

0.72

ns

t48

1.49

ns

t51

OSD_CLK Low Time

Main Video Input, SDR and DDR Mode Setup

Time (Data Latched on Rising Edge)

Main Video Input, SDR and DDR Modes Hold

Time (Data Latched on Rising Edge)

Main Video Input, DDR Mode Setup Time

(Data Latched on Falling Edge)

Main Video Input, DDR Mode Hold Time

(Data Latched on Falling Edge)

Interleaved Video Input, SDR Setup Time

(Data Latched on Rising Edge)

Interleaved Video Input, SDR Hold Time

(Data Latched on Rising Edge)

External OSD Input, SDR and DDR Mode Setup

Time (Data Latched on Rising Edge)

External OSD Input, SDR and DDR Mode Hold

Time (Data Latched on Rising Edge)

External OSD Input, DDR Mode Setup Time

(Data Latched on Rising Edge)

External OSD Input, DDR Mode Hold Time

(Data Latched on Rising Edge)

Typ

5

PCLK Low Time

OSD_CLK High Time

Min

%

duty

cycle

%

duty

cycle

%

duty

cycle

%

duty

cycle

ns

t49

Used for 300 MHz TTL data

1.42

ns

t50

Used for 300 MHz TTL data

0.95

ns

t52

1.33

ns

t53

0.94

ns

t54

0.57

ns

t55

1.51

ns

Rev. B | Page 10 of 64

Data Sheet

ADV8003

Parameter

VIDEO DATA AND CONTROL OUTPUTS3

OSD_CLK High Time

Symbol

Test Conditions/Comments

Max

Unit

t57

0.60 ×

OSD_CLK

period

0.60 ×

OSD_CLK

period

0.07

%

duty

cycle

%

duty

cycle

ns

t58

1.56

ns

t59

0.41

ns

t60

0.93

ns

0.55 ×

MCLK

periods

0.55 ×

MCLK

periods

%

duty

cycle

%

duty

cycle

ns

ns

0.55 ×

SCLK

periods

0.55 ×

SCLK

periods

%

duty

cycle

%

duty

cycle

ns

ns

0.55 ×

DSDCLK

periods

0.55 × SCLK

periods

%

duty

cycle

%

duty

cycle

ns

ns

t56

Typ

0.40 ×

OSD_CLK

period

0.40 ×

OSD_CLK

period

OSD_CLK Low Time

OSD_CLK Active Edge to Data and Control

Start of Data Invalid (Data Latched on Falling

Edge)

OSD_CLK Active Edge to Data and Control End

of Data Invalid (Data Latched on Falling Edge)

OSD_CLK Active Edge to Data and Control

Start of Data Invalid (Data Latched on Rising

Edge)

OSD_CLK Active Edge to Data and Control End

of Data Invalid (Data Latched on Rising Edge)

S/PDIF INPUT3

MCLK High Time

Min

t61

0.45 × MCLK

periods

MCLK Low Time

0.45 × MCLK

periods

S/PDIF Data Setup Time

S/PDIF Data Hold Time

I2S PORT, SLAVE MODE3

SCLK High Time

t62

t63

0.12

1.89

t64

0.45 × SCLK

periods

SCLK Low Time

0.45 × SCLK

periods

I2S Data Setup Time

I2S Data Hold Time

DSD PORT3

DSD Clock High Time

t65

t66

0.42

1.38

t67

0.45 × DSD

CLK periods

DSD Clock Low Time

0.45 × SCLK

periods

DSD Data Setup Time

DSD Data Hold Time

t68

t69

0.48

1.79

It is possible to run I2C at faster speeds; however, it has been characterized to run only in fast mode.

All serial port measurements are for the default polarity and phase settings (clock low in idle state and negative edge used).

3

All measurements are guaranteed by design only.

1

2

Timing Diagrams

t3

t5

t3

SDA

t1

SCL

t2

t7

t4

2

Figure 4. I C Timing

Rev. B | Page 11 of 64

t8

10556-004

t6

ADV8003

Data Sheet

t13

t9

t11

t12

t10

CS2

0

0

0

SCK2

1

0

1

SCK2

2

1

0

SCK2

3

1

1

SCK2

INSTRUCTION(0x0B)

MOSI2

24-BIT ADDRESS

23 22 21 ... 3

2

1

DUMMY BYTE

0

7

6

5

4

3

2

1

0

DATA OUT 1

MISO2

7

6

5

4

3

2

DATA OUT 2

1

0

7

6

5

4

3

2

1

10556-005

SPI

MODE CPOL CPHA

0

Figure 5. Detailed SPI Master Timing Diagram (Serial Port 2)

t14

t17

t17

t18

t15

t18

t16

SCK2

MOSI2

CS2

MISO2

(FALLING EDGE CAPTURE)

10556-006

MISO2

(RISING EDGE CAPTURE)

Figure 6. Serial Port 2 Master Mode Timing (SPI Mode 0 and SPI Mode 3)

t14

t21

t19

t20

t21

t22

t22

SCK2

MOSI2

CS2

MISO2

(RISING EDGE CAPTURE)

10556-007

MISO2

(FALLING EDGE CAPTURE)

Figure 7. Serial Port 2 Master Mode Timing (SPI Mode 1 and SPI Mode 2)

Rev. B | Page 12 of 64

Data Sheet

ADV8003

t27

t23

SPI

MODE CPOL CPHA

t24

CS1

0

0

0

SCK1

1

0

1

SCK1

2

1

0

SCK1

3

1

1

SCK1

t25

t26

W/R

7

6

5

4

1

2

3

0

7

6

5

4

3

2

1

0

7

5

6

4

3

2

DATA IN 1

1

0

7

6

7

6

6

5

4

3

2

3

2

1

0

5

4

3

2

1

0

1

0

DATA OUT 1

DATA OUT 0

7

4

DATA OUT 0

DUMMY BYTE

DELAY MODE 1

MISO1

DELAY MODE 0

MISO1

5

1

0

7

6

5

4

3

2

10556-008

MOSI1

DATA IN 0

SUB ADDRESS

DEVICE ADDRESS

Figure 8. Detailed SPI Slave Timing Diagram (Serial Port 1)

t30

t31

t34

t32

t33

SCK1

10556-009

MOSI1

MISO1

Figure 9. Serial Port 1 Slave Mode Timing (SPI Mode 0 and SPI Mode 3)

t30

t35

t38

t37

t36

SCK1

10556-010

MOSI1

MI SO1

Figure 10. Serial Port 1 Slave Mode Timing (SPI Mode 1 and SPI Mode 2)

t39

t40

t41

VBI_SCK

10556-011

VBI_CS

VBI_MOSI

Figure 11. Serial Port 3 Slave Mode Timing (SPI Mode 0 Only)

Rev. B | Page 13 of 64

ADV8003

Data Sheet

t43

t42

SCK1

MISO2

MOSI1

CS1

10556-012

SCK2

MISO1

MOSI2

CS2

Figure 12. SPI Pass-Through Mode (Serial Port 1 and Serial Port 2)

t45

t44

t46

PCLK

10556-013

P[35:0]

HS

VS

DE

Figure 13. Main Video Input, Noninterleaved SDR Video Data and Control Timing

t44

PCLK

t47

t46

t48

t45

10556-014

P[35:0]

HS

VS

DE

Figure 14. Main Video Input, Noninterleaved DDR Video Data and Control Timing

t44

PCLK

t49

t50

OSD_IN[11:0]

P[35:24]

10556-015

P[23:0]

HS

VS

DE

Figure 15. Interleaved SDR Video Data and Control Input Timing

Rev. B | Page 14 of 64

Data Sheet

ADV8003

t51

OSD_CLK

t53

t52

10556-016

OSD_IN[23:0]

OSD_HS

OSD_VS

OSD_DE

Figure 16. External OSD Input, Noninterleaved SDR Video Data and Control Timing

t51

OSD_CLK

t54

t53

t55

t52

10556-017

OSD_IN[23:0]

OSD_HS

OSD_VS

OSD_DE

Figure 17. External OSD Input, Noninterleaved DDR Video Data and Control Timing

t56

OSD_CLK

t57

t58

10556-018

OSD_IN[23:0]

P[35:24]

OSD_HS

OSD_VS

OSD_DE

Figure 18. SDR Video Data and Control Output Timing (Data Launched on Falling Edge)

t56

OSD_CLK

t59

t60

10556-119

OSD_IN[23:0]

P[35:24]

OSD_HS

OSD_VS

OSD_DE

Figure 19. SDR Video Data and Control Output Timing (Data Launched on Rising Edge)

Rev. B | Page 15 of 64

ADV8003

Data Sheet

t61

MCLK

t62

t63

10556-120

S/PDIF

AUDIO

DATA

Figure 20. S/PDIF Input Timing, Data Latched on Rising Edge

DATA

SYNC IMPULSE

S/PDIF

1.5 × tMCLK

10556-020

tMCLK

0.5 × tMCLK

Figure 21. S/PDIF Data Timing

t64

SCLK

t65

t66

10556-021

I2S[3:0]

LRCLK

Figure 22. I2S Timing

AUD_IN[5]

RIGHT

LEFT

SCLK

MSBLEFT

LSB

LSB

MSBRIGHT

32 CLOCK SLOTS

32 CLOCK SLOTS

I2S STANDARD

I2S FORMAT = 00

10556-022

AUD_IN[4:1]

Figure 23. I2S Standard Audio—Data Width of 16 Bits to 24 Bits per Channel

AUD_IN[5]

LEFT

RIGHT

SCLK

LSBRIGHT

LSBLEFT

MSBLEFT

LSB

MSBRIGHT

16 CLOCK SLOTS

16 CLOCK SLOTS

I2S STANDARD 16-BIT PER CHANNEL

I2S FORMAT = 00

Figure 24. I2S Standard Audio—16-Bit Samples Only

Rev. B | Page 16 of 64

10556-023

AUD_IN[4:1]

Data Sheet

AUD_IN[5]

ADV8003

LEFT

RIGHT

SCLK

AUD_IN[4:1]

MSB

MSB

MSB

MSB – 1

MSB

LSB

MSB

MSB

MSB

MSB – 1

MSB

LSB

MSB

EXTENDED

MSB

EXTENDED

32 CLOCK SLOTS

10556-024

32 CLOCK SLOTS

SERIAL AUDIO

RIGHT JUSTIFIED

2

I S FORMAT = 01

Figure 25. Serial Audio—Right-Justified

AUD_IN[5]

LEFT

RIGHT

SCLK

AUD_IN[4:1]

LSB

MSB

LSB

MSB

32 CLOCK SLOTS

32 CLOCK SLOTS

10556-125

SERIAL AUDIO

LEFT JUSTIFIED

I2S FORMAT = 10

Figure 26. Serial Audio—Left-Justified

AUD_IN[5]

CHANNEL A

CHANNEL B

SCLK

MSB

V

U

C

LSB

P

MSB

V

U

32 CLOCK SLOTS

C

P

32 CLOCK SLOTS

FRAME n

FRAME n + 1

AES3 DIRECT AUDIO

I2S FORMAT = 11

Figure 27. AES3 Direct Audio

t67

DSD_CLK

t68

t69

DSD[5:0]

Figure 28. DSD Timing

Rev. B | Page 17 of 64

10556-126

LSB

10556-127

AUD_IN[4:1]

ADV8003

Data Sheet

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter

AVDD1, ADDD2, DVDD_IO to GND

DVDD, PVDDx, CVDD1, AVDD3,

DVDD_DDR, PVDD_DDR to GND

DVDD to Other 1.8 V Power Supplies 1

PVDD1 to Other 1.8 V Power Supplies1

PVDD2 to Other 1.8 V Power Supplies1

PVDD3 to Other 1.8 V Power Supplies1

PVDD5 to Other 1.8 V Power Supplies1

PVDD6 to Other 1.8 V Power Supplies1

CVDD1 to Other 1.8 V Power Supplies1

AVDD3 to Other 1.8 V Power Supplies1

DVDD_DDR to Other 1.8 V Power

Supplies1

PVDD_DDR to Other 1.8 V Power

Supplies1

Digital Inputs to GND

Serial Video Inputs to GND

DDR_IO and DDR_VREF to GND

5 V Tolerant Digital Inputs to GND 2

1.8 V Analog Inputs to GND

3.3 V Analog Inputs to GND

HDMI Digital Outputs to GND

Digital Outputs Voltage to GND

Analog Outputs Voltage to GND 3

Maximum Junction Temperature (TJ MAX)

Storage Temperature Range

Infrared Reflow Soldering (20 sec)

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rating

3.9 V

2.2 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

−0.3 V to +0.3 V

ESD CAUTION

−0.3 V to +0.3 V

−0.3 V to DVDD_IO + 0.3 V

−0.3 V to CVDD1 + 0.3 V

−0.3 V to DVDD_DDR + 0.3 V

−0.3 V to +5.5 V

−0.3 V to AVDD3 + 0.3 V

−0.3 V to AVDD2 + 0.3 V

−0.3 V to AVDD3 + 0.3 V

−0.3 V to DVDD_IO + 0.3 V

−0.3 V to AVDD2 + 0.3 V

125°C

−65°C to+150°C

260°C

1.8 V power supplies include DVDD, PVDD1, PVDD2, PVDD3, PVDD5, PVDD6,

CVDD1, AVDD3, DVDD_DDR, and PVDD_DR.

The following inputs are 5 V tolerant: CEC1, CEC2, DDC1_SCL, DDC2_SCL,

DDC1_SDA, DDC2_SDA, HEAC_1−, HEAC_1+, HEAC_2−, HEAC_2+, RX_5V,

and RX_HPD.

3

Except the ELPF1 and ELPF2 outputs, which are kept to −0.3 V to PVDD3 +

0.3 V; the RTERM output, which is kept to −0.3 V to CVDD1 + 0.3 V; and the

R_TX1 and R_TX2 outputs, which are kept to −0.3 V to PVDD5 + 0.3 V.

1

2

Rev. B | Page 18 of 64

Data Sheet

ADV8003

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

2

3

4

5

6

9

10

A

OSD_

DE

OSD_

CLK/

EXT_

CLK

AUD_

IN[1]

AUD_

IN[2]

AUD_

IN[5]

ARC2_

OUT MOSI1

SCK2

CS2

B

OSD_

IN[21]/

EXT_

DIN[5]

OSD_

IN[22]/

EXT_

DIN[6]

OSD_

VS

AUD_

IN[0]

AUD_

IN[3]

SFL

ARC1_

MISO1

OUT

MOSI2 MISO2

C

OSD_

IN[19]/

EXT_

DIN[3]

OSD_

IN[20]/

EXT_

DIN[4]

GND

AUD_

IN[4]

DSD_

CLK

SCLK

SCL

SCK1

GND

INT0

PDN

GND

D

OSD_

IN[16]/

EXT_

DIN[0]

OSD_

IN[17]/

EXT_

DIN[1]

OSD_

IN[18]/

EXT_

DIN[2]

GND

DVDD_

IO

MCLK

SDA

CS1

GND

INT1

INT2

DVDD_

IO

OSD_

IN[15]/

VBI_CS

DVDD_

IO

E

OSD_

OSD_

IN[13]/

IN[14]/

VBI_SCK VBI_MOSI

7

8

11

12

14

15

RESET XTALN PVDD2

NC

NC

XTALP PVDD1

NC

NC

GND

RX_CP RX_0P RX_1P

GND

NC

NC

RX_

HPD

AVDD1

GND

TEST1

NC

NC

RX_5V

NC

NC

ALSB

13

16

17

18

19

20

21

22

23

RX_2N CVDD1 RSET1

VREF

A

COMP1

DAC4

B

AVDD1 AVDD1

DAC5

DAC6

C

RTERM AVDD2 AVDD2

DAC1

DAC2

D

COMP2

DAC3

E

RSET2 PVDD3

GND

CEC1

F

GND

AVDD3

G

CVDD1 RX_CN RX_0N RX_1N

GND

RX_2P

TEST2

GND

GND

F

OSD_

IN[9]

OSD_

IN[10]

OSD_

IN[11]

OSD_

IN[12]

G

OSD_

IN[5]

OSD_

IN[6]

OSD_

IN[7]

OSD_

IN[8]

GND

GND

GND

DVDD

GND

GND

DVDD

GND

GND

GND

GND

ELPF1

ELPF2

H

OSD_

IN[1]

OSD_

IN[2]

OSD_

IN[3]

OSD_

IN[4]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

TX1_2+ TX1_2–

H

OSD_

HS

OSD_

IN[0]

DVDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

DVDD

DDC1_

SDA

GND

TX1_1+ TX1_1–

J

DVDD_ DVDD_

IO

IO

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DDC1_

SCL

J

DE

HS

K

VS

PCLK

GND

TX1_0+ TX1_0–

K

L

P[32]

P[33]

P[34]

P[35]

DVDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HPD_

TX1

GND

TX1_C+ TX1_C–

L

M

P[28]

P[29]

P[30]

P[31]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

R_TX1

PVDD5

HEAC_ HEAC_

1–

1+

M

N

P[24]

P[25]

P[26]

P[27]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

CEC2

PVDD5 AVDD3

DVDD

DDC2_

SCL

GND

TX2_2+ TX2_2–

P

GND

TX2_1+ TX2_1–

R

P

P[20]

P[21]

P[22]

DVDD

P[23]

GND

GND

GND

GND

GND

GND

GND

GND

GND

NC

N

R

P[16]

P[17]

P[18]

P[19]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DDC2_

SDA

T

P[14]

P[15]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HPD_

TX2

GND

TX2_0+ TX2_0–

T

U

P[10]

P[11]

P[12]

P[13]

GND

GND

DVDD

GND

GND

DVDD

GND

GND

DVDD

GND

GND

R_TX2

GND

TX2_C+ TX2_C–

U

V

P[6]

P[7]

P[8]

P[9]

GND

PVDD6

HEAC_ HEAC_

2+

2–

V

W

P[2]

P[3]

P[4]

P[5]

TEST3

Y

P[0]

P[1]

DDR_

DQS[2]

GND

AA

DDR_

DQ[18]

AB

DDR_

DDR_

DDR_

DQ[21] DQ[19] DQ[17]

AC

DDR_ DDR_

DDR_

DDR_

DDR_

DDR_ DDR_

DDR_

DQ[16] DQ[20] DQ[22] DQ[25] DQ[28] DQ[27] DQ[24] A[9]

1

GND

2

GND

3

DDR_

CAS

DVDD_

DDR

DDR_

A[2]

GND

DDR_

CS

DVDD_

DDR

DDR_

CK

DDR_

A[12]

DDR_

A[6]

DDR_

A[3]

DDR_

A[0]

DDR_

BA[0]

DDR_

RAS

DDR_

CKE

DDR_

A[5]

DDR_

A[7]

DDR_

A[1]

DDR_

A[10]

DDR_

BA[1]

DDR_

BA[2]

DDR_

WE

DDR_

VREF

9

10

12

13

14

15

16

GND

DDR_

A[11]

DDR_ DDR_ DVDD_ DDR_

DQS[2] DQ[26] DDR DQS[3]

NC/

GND

DDR_

DM[2]

4

DDR_

DQ[30]

5

DDR_

DM[3]

6

DDR_ DDR_

DQ[31] DQ[29]

7

8

DDR_

CK

GND

DDR_ DVDD_ DDR_

DQS[3]

DQ[23] DDR

DVDD_

DDR

DDR_

A[4]

DDR_

A[8]

11

DVDD_

DDR

GND

DDR_

DQ[9]

GND

DDR_ DVDD_

DQ[11]

DDR

GND

W

DDR_

DQ[6]

PVDD_

DDR

GND

Y

AA

DDR_

DM[1]

DDR_

DM[0]

GND

GND

DDR_

DQ[3]

DDR_

DQ[13]

DDR_

DQ[0]

DDR_

DQ[5]

DDR_

DQS[0]

DDR_

DQ[4]

AB

DDR_

DDR_

DDR_

DQ[10] DQS[1] DQ[15]

DDR_

DQ[7]

DDR_

DQ[2]

DDR_

DQS[0]

DDR_

DQ[1]

AC

20

21

22

23

DDR_

DDR_

DQ[12] DQS[1]

17

Figure 29. ADV8003KBCZ-8 and ADV8003KBCZ-7 Pin Configuration

Rev. B | Page 19 of 64

DVDD_ DDR_

DQ[14]

DDR

NC

PVDD6 AVDD3

DDR_

DQ[8]

18

19

10556-025

1

OSD_

IN[23]/

EXT_

DIN[7]

ADV8003

Data Sheet

Table 6. ADV8003KBCZ-8 and ADV8003KBCZ-7 Pin Function Descriptions

Pin No.

A1

Mnemonic

OSD_IN[23]/EXT_DIN[7]

A2

A3

OSD_DE

OSD_CLK/EXT_CLK

Type

OSD video input/

miscellaneous digital

OSD video sync

OSD video sync

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

AUD_IN[1]

AUD_IN[2]

AUD_IN[5]

ARC2_OUT

MOSI1

SCK2

CS2

RESET

XTALN

PVDD2

Audio input

Audio input

Audio input

Audio output

Serial port control

Serial port control

Serial port control

Miscellaneous digital

Miscellaneous digital 1

Power

A14

A15

A16

A17

A18

A19

A20

A21

A22

NC

NC

CVDD1

RX_CN

RX_0N

RX_1N

RX_2N

CVDD1

RSET1

N/A

N/A

Power

Rx input

Rx input

Rx input

Rx input

Power

A23

VREF

Miscellaneous analog1

B1

OSD_IN[21]/EXT_DIN[5]

B2

OSD_IN[22]/EXT_DIN[6]

B3

B4

B5

B6

B7

B8

B9

B10

B11

OSD_VS

AUD_IN[0]

AUD_IN[3]

SFL

ARC1_OUT

MISO1

MOSI2

MISO2

ALSB

OSD video input/

miscellaneous digital

OSD video input/

miscellaneous digital

OSD video sync

Audio input

Audio input

SFL

Audio output

Serial port control

Serial port control

Serial port control

I2C control

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

XTALP

PVDD1

NC

NC

GND

RX_CP

RX_0P

RX_1P

RX_2P

GND

COMP1

DAC4

Miscellaneous analog1

Miscellaneous digital1

Power

N/A

N/A

GND

Rx input

Rx input

Rx input

Rx input

GND

Miscellaneous analog1

Analog video output

Description

External OSD Video Pixel Input Port (OSD_IN[23])/Additional TTL Input for External

CCIR 656 Video Data (EXT_DIN[7]).

Data Enable for the OSD Input Port.

Pixel Clock for the OSD Input Port (OSD_CLK)/Pixel Clock for External Video Data

(EXT_CLK).

I2S0/DSD1 Audio Input.

I2S1/DSD2 Audio Input.

LRCLK/DSD5 Audio Input.

Audio Return Channel for HDMI Tx2.

Master Out Slave In (Serial Port 1). Serial Port 1 is used for OSD control.

Serial Clock (Serial Port 2). Serial Port 2 is used for the external flash ROM.

Chip Select (Serial Port 2). Serial Port 2 is used for the external flash ROM.

Reset Pin.

Crystal Input.

PLL Digital Supply Voltage (1.8 V).

No Connect. Do not connect to this pin.

No Connect. Do not connect to this pin.

Comparator Supply Voltage (1.8 V).

Rx Clock Complement Input.

Rx Channel 0 Complement Input.

Rx Channel 1 Complement Input.

Rx Channel 2 Complement Input.

Comparator Supply Voltage (1.8 V).

Resistor Current Setting for Encoder DACs: DAC1, DAC2, and DAC3. Place the RSET1

resistor as close as possible to the ADV8003.

Optional External Voltage Reference Input for DACs or Voltage Reference Output. Place

VREF voltage components as close as possible to the ADV8003.

External OSD Video Pixel Input Port (OSD_IN[21])/Additional TTL Input for External

CCIR 656 Video Data (EXT_DIN[5]).

External OSD Video Pixel Input Port (OSD_IN[22])/Additional TTL Input for External

CCIR 656 Video Data (EXT_DIN[6]).

Vertical Sync for the OSD Input Port.

S/PDIF/DSD0 Audio Input.

I2S2/DSD3 Audio Input.

Subcarrier Frequency Lock Signal (SFL).

Audio Return Channel for HDMI Tx1.

Master In Slave Out (Serial Port 1). Serial Port 1 is used for OSD control.

Master Out Slave In (Serial Port 2). Serial Port 2 is used for the external flash ROM.

Master In Slave Out (Serial Port 2). Serial Port 2 is used for the external flash ROM.

Sets LSB of I2C address. When the ALSB pin is set low, the I2C address is 0x18; when the

ALSB pin is set high, the I2C address is 0x1A.

Crystal Input.

PLL Analog Supply Voltage (1.8 V).

No Connect. Do not connect to this pin.

No Connect. Do not connect to this pin.

Ground.

Rx Clock True Input.

Rx Channel 0 True Input.

Rx Channel 1 True Input.

Rx Channel 2 True Input.

Ground.

Compensation Pin. Connect a 2.2 nF capacitor from COMP1 to AVDD2.

Encoder DAC4 Output.

Rev. B | Page 20 of 64

Data Sheet

ADV8003

Pin No.

C1

Mnemonic

OSD_IN[19]/EXT_DIN[3]

C2

OSD_IN[20]/EXT_DIN[4]

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

C21

C22

C23

D1

GND

AUD_IN[4]

DSD_CLK

SCLK

SCL

SCK1

GND

INT0

PDN

GND

GND

NC

NC

RX_HPD

AVDD1

GND

GND

AVDD1

AVDD1

DAC5

DAC6

OSD_IN[16]/EXT_DIN[0]

D2

OSD_IN[17]/EXT_DIN[1]

D3

OSD_IN[18]/EXT_DIN[2]

D4

D5

D6

D7

D8

D9

D10

GND

DVDD_IO

MCLK

SDA

CS1

GND

INT1

Type

OSD video input/

miscellaneous digital

OSD video input/

miscellaneous digital

GND

Audio input

Audio input

Audio input

I2C control

Serial port control

GND

Miscellaneous digital

Miscellaneous digital

GND

GND

N/A

N/A

Rx input

Power

GND

GND

Power

Power

Analog video output

Analog video output

OSD video input/

miscellaneous digital

OSD video input/

miscellaneous digital

OSD video input/

miscellaneous digital

GND

Power

Audio input

I2C control

Serial port control

GND

Miscellaneous digital

D11

INT2

Miscellaneous digital

D12

D13

D14

D15

D16

D17

D18

D19

DVDD_IO

TEST1

NC

NC

RX_5V

NC

NC

RTERM

Power

Miscellaneous digital

N/A

N/A

Rx input

N/A

N/A

HDMI Rx input

D20

D21

D22

D23

AVDD2

AVDD2

DAC1

DAC2

Power

Power

Analog video output

Analog video output

Description

External OSD Video Pixel Input Port (OSD_IN[19])/Additional TTL Input for External

CCIR 656 Video Data (EXT_DIN[3]).

External OSD Video Pixel Input Port (OSD_IN[20])/Additional TTL Input for External

CCIR 656 Video Data (EXT_DIN[4]).

Ground.

I2S3/DSD4 Audio Input.

DSD Audio Clock Input.

I2S Bit Clock Input.

I2C Clock Input. SCL is open drain; use a 4.7 kΩ resistor to connect this pin to a 3.3 V supply.

Serial Clock (Serial Port 1). Serial Port 1 is used for OSD control.

Ground.

Interrupt Pin 0. When status bits change, this pin is triggered.

Power-Down. This pin controls the power state of the ADV8003.

Ground.

Ground.

No Connect. Do not connect to this pin.

No Connect. Do not connect to this pin.

Hot Plug Assert Signal Output for the Rx Input.

HDMI Rx Inputs Analog Supply (3.3 V).

Ground.

Ground.

HDMI Rx Inputs Analog Supply (3.3 V).

HDMI Rx Inputs Analog Supply (3.3 V).

Encoder DAC5 Output.

Encoder DAC6 Output.

External OSD Video Pixel Input Port (OSD_IN[16])/Additional TTL Input for External

CCIR 656 Video Data (EXT_DIN[0]).

External OSD Video Pixel Input Port (OSD_IN[17])/Additional TTL Input for External

CCIR 656 Video Data (EXT_DIN[1]).

External OSD Video Pixel Input Port (OSD_IN[18])/Additional TTL Input for External

CCIR 656 Video Data (EXT_DIN[2]).

Ground.

Digital Interface Supply (3.3 V).

MCLK for S/PDIF Input Audio.

I2C Data Input. SDA is open drain; use a 4.7 kΩ resistor to connect this pin to a 3.3 V supply.

Chip Select (Serial Port 1). Serial Port 1 is used for OSD control.

Ground.

Interrupt Pin for HDMI Transmitter Outputs. When status bits change, an interrupt is

generated on this pin.

Interrupt Pin for HDMI Receiver Input Lines. When status bits change, an interrupt is

generated on this pin.

Digital Interface Supply (3.3 V).

Test Pin. Float this pin.

No Connect. Do not connect to this pin.

No Connect. Do not connect to this pin.

5 V Detect Pin for the Rx Input.

No Connect. Do not connect to this pin.

No Connect. Do not connect to this pin.

This pin sets internal termination resistance. Use a 500 Ω resistor between this pin and

GND. Place the RTERM resistor as close as possible to the ADV8003.

Analog Power Supply (3.3 V).

Analog Power Supply (3.3 V).

Encoder DAC1 Output.

Encoder DAC2 Output.

Rev. B | Page 21 of 64

ADV8003

Data Sheet

Pin No.

E1

Mnemonic

OSD_IN[13]/VBI_SCK

E2

OSD_IN[14]/VBI_MOSI

E3

OSD_IN[15]/VBI_CS

E4

E20

E21

E22

E23

F1

F2

F3

F4

DVDD_IO

TEST2

GND

COMP2

DAC3

OSD_IN[9]

OSD_IN[10]

OSD_IN[11]

OSD_IN[12]

F20

RSET2

Type

OSD video input/

miscellaneous digital

OSD video input/

miscellaneous digital

OSD video input/

miscellaneous digital

Power

Miscellaneous analog

GND

Miscellaneous analog1

Analog video output

OSD video input

OSD video input

OSD video input

OSD video input/

miscellaneous digital

Miscellaneous analog1

F21

F22

F23

G1

G2

G3

G4

G7

G8

G9

G10

G11

G12

G13

G14

G15

G16

G17

G20

G21

G22

G23

H1

H2

H3

H4

H7

H8

H9

H10

H11

H12

H13

H14

H15

H16

H17

H20

PVDD3

GND

CEC1

OSD_IN[5]

OSD_IN[6]

OSD_IN[7]

OSD_IN[8]

GND

GND

GND

DVDD

GND

GND

DVDD

GND

GND

GND

GND

ELPF1

ELPF2

GND

AVDD3

OSD_IN[1]

OSD_IN[2]

OSD_IN[3]

OSD_IN[4]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

Power

GND

HDMI Tx1

OSD video input

OSD video input

OSD video input

OSD video input

GND

GND

GND

Power

GND

GND

Power

GND

GND

GND

GND

Miscellaneous analog1

Miscellaneous analog1

GND

Power

OSD video input

OSD video input

OSD video input

OSD video input

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

Description

External OSD Video Pixel Input Port (OSD_IN[13])/Serial Clock for VBI Data Serial Port

(VBI_SCK).

External OSD Video Pixel Input Port (OSD_IN[14])/Master Out Slave In for VBI Data

Serial Port (VBI_MOSI).

External OSD Video Pixel Input Port (OSD_IN[15])/Chip Select for VBI Data Serial Port

(VBI_CS).

Digital Interface Supply (3.3 V).

Test Pin. Float this pin.

Ground.

Compensation Pin. Connect a 2.2 nF capacitor to AVDD2.

Encoder DAC3 Output.

External OSD Video Pixel Input Port (OSD_IN[9]).

External OSD Video Pixel Input Port (OSD_IN[10]).

External OSD Video Pixel Input Port (OSD_IN[11]).

External OSD Video Pixel Input Port (OSD_IN[12]).

Resistor Current Setting for Encoder DACs: DAC4, DAC5, and DAC6. Place the RSET2

resistor as close as possible to the ADV8003.

PLL Supply (1.8 V).

Ground.

HDMI Tx1 Consumer Electronics Control (CEC).

External OSD Video Pixel Input Port (OSD_IN[5]).

External OSD Video Pixel Input Port (OSD_IN[6]).

External OSD Video Pixel Input Port (OSD_IN[7]).

External OSD Video Pixel Input Port (OSD_IN[8]).

Ground.

Ground.

Ground.

Digital Power Supply (1.8 V).

Ground.

Ground.

Digital Power Supply (1.8 V).

Ground.

Ground.

Ground.

Ground.

External Loop Filter for PLL 1. Connect to PVDD3.

External Loop Filter for PLL 2. Connect to PVDD3.

Ground.

HDMI Analog Power Supply (1.8 V).

External OSD Video Pixel Input Port (OSD_IN[1]).

External OSD Video Pixel Input Port (OSD_IN[2]).

External OSD Video Pixel Input Port (OSD_IN[3]).

External OSD Video Pixel Input Port (OSD_IN[4]).

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Rev. B | Page 22 of 64

Data Sheet

ADV8003

Pin No.

H21

H22

H23

J1

J2

J3

J4

J7

J8

J9

J10

J11

J12

J13

J14

J15

J16

J17

J20

Mnemonic

GND

TX1_2+

TX1_2−

DE

HS

OSD_HS

OSD_IN[0]

DVDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

DVDD

DDC1_SDA

Type

GND

HDMI Tx1

HDMI Tx1

Digital video sync

Digital video sync

Digital video sync

OSD video input

Power

GND

GND

GND

GND

GND

GND

GND

GND

GND

Power

HDMI Tx1

J21

J22

J23

K1

K2

K3

K4

K7

K8

K9

K10

K11

K12

K13

K14

K15

K16

K17

K20

GND

TX1_1+

TX1_1−

VS

PCLK

DVDD_IO

DVDD_IO

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DDC1_SCL

GND

HDMI Tx1

HDMI Tx1

Digital video sync

Digital video sync

Power

Power

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HDMI Tx1

K21

K22

K23

L1

L2

L3

L4

L7

L8

L9

L10

L11

L12

L13

L14

L15

GND

TX1_0+

TX1_0−

P[32]

P[33]

P[34]

P[35]

DVDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

HDMI Tx1

HDMI Tx1

Digital video input

Digital video input

Digital video input

Digital video input

Power

GND

GND

GND

GND

GND

GND

GND

GND

Description

Ground.

HDMI1 Channel 2 True Output.

HDMI1 Channel 2 Complementary Output.

Data Enable for Digital Input Video.

Horizontal Sync for Digital Input Video.

Horizontal Sync for the OSD Input Port (OSD_HS).

External OSD Video Pixel Input Port (OSD_IN[0]).

Digital Power Supply (1.8 V).

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Digital Power Supply (1.8 V).

HDCP Slave Serial Data for HDMI Tx1. This pin is open drain; use a 2 kΩ resistor to

connect this pin to the HDMI Tx 5 V supply.

Ground.

HDMI1 Channel 1 True Output.

HDMI1 Channel 1 Complementary Output.

Vertical Sync for Digital Input Video.

Pixel Clock for Digital Input Video.

Digital Interface Supply (3.3 V).

Digital Interface Supply (3.3 V).

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

HDCP Slave Serial Clock for HDMI Tx1. This pin is open drain; use a 2 kΩ resistor to

connect this pin to the HDMI Tx 5 V supply.

Ground.

HDMI1 Channel 0 True Output.

HDMI1 Channel 0 Complementary Output.

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Power Supply (1.8 V).

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Rev. B | Page 23 of 64

ADV8003

Data Sheet

Pin No.

L16

L17

L20

L21

L22

L23

M1

M2

M3

M4

M7

M8

M9

M10

M11

M12

M13

M14

M15

M16

M17

M20

Mnemonic

GND

GND

HPD_TX1

GND

TX1_C+

TX1_C−

P[28]

P[29]

P[30]

P[31]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

R_TX1

Type

GND

GND

HDMI Tx1

GND

HDMI Tx1

HDMI Tx1

Digital video input

Digital video input

Digital video input

Digital video input

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HDMI Tx11

M21

M22

M23

N1

N2

N3

N4

N7

N8

N9

N10

N11

N12

N13

N14

N15

N16

N17

N20

N21

N22

N23

P1

P2

P3

P4

P7

P8

P9

P10

P11

P12

P13

PVDD5

HEAC_1+

HEAC_1−

P[24]

P[25]

P[26]

P[27]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

CEC2

PVDD5

AVDD3

NC

P[20]

P[21]

P[22]

P[23]

DVDD

GND

GND

GND

GND

GND

GND

Power1

HDMI Tx1

HDMI Tx1

Digital video input

Digital video input

Digital video input

Digital video input

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HDMI Tx2

Power1

Power

N/A

Digital video input

Digital video input

Digital video input

Digital video input

Power

GND

GND

GND

GND

GND

GND

Description

Ground.

Ground.

Hot Plug Assert Signal Input for HDMI Tx1.

Ground.

HDMI1 Clock True Output.

HDMI1 Clock Complementary Output.

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Sets Internal Reference Currents. Place a 470 Ω resistor (1% tolerance) between this pin and

ground, as close as possible to the ADV8003.

HDMI Tx PLL Power Supply (1.8 V).

HDMI Tx1 HEAC+ from the HDMI Connector.

HDMI Tx1 HEAC− from the HDMI Connector.

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

HDMI Tx2 Consumer Electronics Control (CEC).

HDMI Tx PLL Power Supply (1.8 V).

HDMI Analog Power Supply (1.8 V).

No Connect. Do not connect to this pin.

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Power Supply (1.8 V).

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Rev. B | Page 24 of 64

Data Sheet

ADV8003

Pin No.

P14

P15

P16

P17

P20

Mnemonic

GND

GND

GND

DVDD

DDC2_SCL

Type

GND

GND

GND

Power

HDMI Tx2

P21

P22

P23

R1

R2

R3

R4

R7

R8

R9

R10

R11

R12

R13

R14

R15

R16

R17

R20

GND

TX2_2+

TX2_2−

P[16]

P[17]

P[18]

P[19]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DDC2_SDA

GND

HDMI Tx2

HDMI Tx2

Digital video input

Digital video input

Digital video input

Digital video input

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HDMI Tx2

R21

R22

R23

T1

T2

T3

T4

T7

T8

T9

T10

T11

T12

T13

T14

T15

T16

T17

T20

T21

T22

T23

U1

U2

U3

U4

U7

U8

U9

U10

GND

TX2_1+

TX2_1−

P[14]

P[15]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HPD_TX2

GND

TX2_0+

TX2_0−

P[10]

P[11]

P[12]

P[13]

GND

GND

DVDD

GND

GND

HDMI Tx2

HDMI Tx2

Digital video input

Digital video input

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HDMI Tx2

GND

HDMI Tx2

HDMI Tx2

Digital video input

Digital video input

Digital video input

Digital video input

GND

GND

Power

GND

Description

Ground.

Ground.

Ground.

Digital Power Supply (1.8 V).

HDCP Slave Serial Clock for HDMI Tx2. This pin is open drain; use a 2 kΩ resistor to

connect this pin to the HDMI Tx 5 V supply.

Ground.

HDMI2 Channel 2 True Output.

HDMI2 Channel 2 Complementary Output.

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

HDCP Slave Serial Data for HDMI Tx2. This pin is open drain; use a 2 kΩ resistor to

connect this pin to the HDMI Tx 5 V supply.

Ground.

HDMI2 Channel 1 True Output.

HDMI2 Channel 1 Complementary Output.

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Ground.

Hot Plug Assert Signal Input for HDMI Tx2.

Ground.

HDMI2 Channel 0 True Output.

HDMI2 Channel 0 Complementary Output.

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Digital Video Input Bus[35:0].

Ground.

Ground.

Digital Power Supply (1.8 V).

Ground.

Rev. B | Page 25 of 64

ADV8003

Data Sheet

Pin No.

U11

U12

U13

U14

U15

U16

U17

U20

Mnemonic

GND

DVDD

GND

GND

DVDD

GND

GND

R_TX2

Type

GND

Power

GND

GND

Power