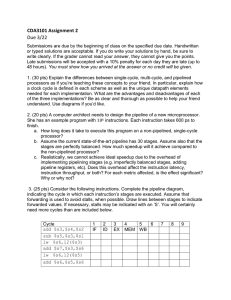

CDA3101 Assignment 3

advertisement

CDA3101 Assignment 3 Due 6/24 Submissions are due by the beginning of class on the specified due date. Handwritten or typed solutions are acceptable. If you do write your solutions by hand, be sure to write clearly. If the grader cannot read your answer, they cannot give you the points. Late submissions will be accepted with a 10% penalty for each day they are late (up to 48 hours). You must show how you arrived at the answer or no credit will be given. 1. (40 pts) Pretend you’re hanging out in the Majors’ lab and a fellow student is struggling with some Comp Org II concepts. Explain the differences between singlecycle, multi-cycle, and pipelined processors as if you’re teaching these concepts to your friend. In particular, explain how a clock cycle is defined in each scheme as well as the unique datapath elements needed for each implementation. What are the advantages and disadvantages of each of the three implementations? Be as clear and thorough as possible to help your friend understand. Use diagrams if you’d like. 2. (30 pts) A computer architect needs to design the pipeline of a new microprocessor. She has an example program with 106 instructions. Each instruction takes 600 ps to finish. a. How long does it take to execute this program on a non-pipelined, single-cycle processor? b. Assume the current state-of-the-art pipeline has 30 stages. Assume also that the stages are perfectly balanced. How much speedup will it achieve compared to the non-pipelined processor? c. Realistically, we cannot achieve ideal speedup due to the overhead of implementing pipelining stages (e.g. imperfectly balanced stages, adding pipeline registers, etc). Does this overhead affect the instruction latency, instruction throughput, or both? For each metric affected, is the effect significant? Why or why not? 3. (30 pts) Identify all of the data dependencies in the following MIPS code (even if they are not hazards). Which dependencies are data hazards that can be resolved via forwarding? Which data dependencies are data hazards that will cause a stall? add sub lw add lw add $s3, $s5, $s6, $s7, $s6, $s6, $s4, $s2 $s3, $s1 12($s3) $s3, $s6 12($s5) $s5, $s6