TEST 2 REVIEW Lectures 5-10

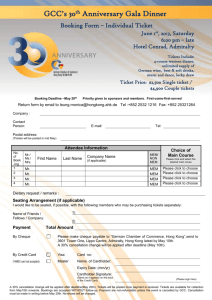

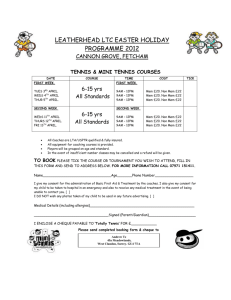

advertisement

TEST 2 REVIEW Lectures 5-10 REVIEW Test 2 will cover lectures 5-10. There are approx. 8-10 questions in total with the last being a bonus question. The questions take the form of short answers (where you are expected to write briefly on a topic), homework-like problems, and exercises similar to those done in lectures. PIPELINE EXERCISE Perhaps the most important skill for you to have developed in this unit is the ability to understand and specify the state of a pipeline executing a given set of instructions. This skill indicates that you understand not only how basic pipelining works, but also how hazards are handled in a processor. We will do one of these exercises together. PIPELINE EXERCISE Imagine we have the following instructions being executed. 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? PIPELINE EXERCISE 24 28 32 36 40 lw sub and or add IF/ID Field PC+4 Instruction $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 Value What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? PIPELINE EXERCISE 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? 20($1) $2, $3 $4, $5 $6, $7 $8, $9 IF/ID Field Value PC+4 44 Instruction add $14, $8, $9 We’ll use a ‘?’ to indicate that a value cannot be known with the information we have. An ‘X’ indicates a “don’t care” for data that we can calculate, but don’t need. PIPELINE EXERCISE ID/EX Field Value ID/EX Field PC+4 RegWrite Instruction MemtoReg branchTarget MemRead Read Data 1 MemWrite Read Data 2 ALUSrc Immediate ALUOp RegisterRs RegDst RegisterRt RegisterRd Value What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 PIPELINE EXERCISE ID/EX Field Value ID/EX Field Value PC+4 40 RegWrite 1 Instruction or $13,$6,$7 MemtoReg 0 branchTarget X MemRead 0 Read Data 1 ? MemWrite 0 Read Data 2 ? ALUSrc 0 Immediate X ALUOp 10 RegisterRs 6 RegDst 1 RegisterRt 7 RegisterRd 13 What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 PIPELINE EXERCISE EX/MEM Field PC+4 Instruction RegWrite MemtoReg MemRead MemWrite ALUResult writeData writeRegister Value What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 PIPELINE EXERCISE EX/MEM Field Value PC+4 36 Instruction and $12,$4,$5 RegWrite 1 MemtoReg 0 MemRead 0 MemWrite 0 ALUResult ? writeData ? writeRegister 12 What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 PIPELINE EXERCISE MEM/WB Field PC+4 Instruction RegWrite MemtoReg writeDataMem writeDataALU writeRegister Value What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 PIPELINE EXERCISE MEM/WB Field Value PC+4 32 Instruction sub $11,$2,$3 RegWrite 1 MemtoReg 0 writeDataMem ? writeDataALU ? writeRegister 11 What are the contents of IF/ID, ID/EX, EX/MEM, and MEM/WB at the end of cycle 5? 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 PIPELINE EXERCISE MEM/WB Field Value PC+4 Instruction RegWrite MemtoReg writeDataMem writeDataALU writeRegister What is the contents of the MEM/WB register at the end of cycle 4? 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 PIPELINE EXERCISE MEM/WB Field Value PC+4 ? Instruction lw $10,20($1) RegWrite 1 MemtoReg 1 writeDataMem ? writeDataALU ? writeRegister 10 What is the contents of the MEM/WB register at the end of cycle 4? 24 28 32 36 40 lw sub and or add $10, $11, $12, $13, $14, 20($1) $2, $3 $4, $5 $6, $7 $8, $9 FORWARDING EXERCISE Consider the following sequence of instructions. add $1,$5,$3 sw $1,0($2) lw $1,4($2) add $5,$5,$1 sw $1,0($2) Assume we have no forwarding or other hazard detection. Insert NOOPs into the instruction sequence to ensure correct execution. FORWARDING EXERCISE Consider the following sequence of instructions. add $1,$5,$3 noop noop sw $1,0($2) lw $1,4($2) noop noop add $5,$5,$1 sw $1,0($2) Now assume we have forwarding and can stall as necessary. Construct the pipeline diagram for the original instruction sequence, indicating where forwards are made if necessary. FORWARDING EXERCISE Consider the following sequence of instructions. add $1,$5,$3 sw $1,0($2) lw $1,4($2) add $5,$5,$1 sw $1,0($2) Now assume we have forwarding and can stall as necessary. Construct the pipeline diagram for the instruction sequence, indicating where forwards are made if necessary. cycle 1 2 3 4 5 add IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID STALL IF STALL sw lw add sw 6 7 8 9 EX MEM WB ID EX MEM 10 WB BRANCH PREDICTION EXERCISE Consider the following sequence of instructions (with their 8-bit addresses indicated on the left). Before this snippet executes, the value of $s0 is always 5, $s1 is always 0, and $s2 is always 1. 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 Imagine that this code snippet is executed twice in a processor which uses a 1-bit branch prediction buffer initialized to not taken. Let’s find out how many mispredictions will we make over the two executions. BRANCH PREDICTION EXERCISE First of all, let’s construct our initial 1-bit BPB. How many indexing bits does this particular code segment need to uniquely identify the instructions? 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 BRANCH PREDICTION EXERCISE First of all, let’s construct our initial 1-bit BPB. How many indexing bits does this particular code segment need to uniquely identify the instructions? 2 bits! We’ll begin by predicting not taken for every instruction. 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 Lower Portion of Address Prediction 0000 0 0100 0 1000 0 1100 0 BRANCH PREDICTION EXERCISE Over the course of two executions of the code snippet, the branch instruction is taken 8 times and not taken twice. The action and predictions, according to the 1-bit branch prediction buffer, are shown to the right. Action Prediction Taken 0 Taken 1 Taken 1 Our mis-prediction rate is 4/10. Taken 1 Not Taken 1 Taken 0 Taken 1 Taken 1 Taken 1 Not Taken 1 What is the mis-prediction rate for a 2-bit branch prediction buffer that is initialized to weakly not taken? BRANCH PREDICTION EXERCISE What is the misprediction rate for a 2-bit branch prediction buffer that is initialized to weakly not taken? Our prediction is not as sensitive now – we require multiple wrong decisions to change the prediction. The mis-prediction rate is now 3/10. Action Prediction Taken 01 Taken 10 Taken 11 Taken 11 Not Taken 11 Taken 10 Taken 11 Taken 11 Taken 11 Not Taken 11 BRANCH PREDICTION EXERCISE Let’s say we have a two-bit branch prediction buffer where every entry is initially weakly not taken. 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 What would the contents of the initially empty branch target buffer look like after a single execution of the code snippet above? Lower Portion of Address Prediction 0000 01 0100 01 1000 01 1100 01 BRANCH PREDICTION EXERCISE Let’s say we have a two-bit branch prediction buffer where every entry is initially weakly not taken. 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 What would the contents of the initially empty branch target buffer look like after a single execution of the code snippet above? Lower Portion of Address Prediction 0000 01 0100 10 1000 01 1100 01 Lower Portion of Address Tag Target 1101 L1 0000 0100 1000 1100 BRANCH PREDICTION EXERCISE 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 Lower Portion of Address Prediction Lower Portion of Address 0000 01 0000 0100 01 0100 1000 01 1000 1100 01 1100 Given the instructions above, and the initially empty BTB and weakly not-taken BPB, draw the pipeline diagram for a single execution of the code snippet, assuming branch prediction happens in the IF stage. Tag Target BRANCH PREDICTION EXERCISE 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 cycle 1 2 3 4 5 sub IF ID EX MEM WB IF ID EX MEM WB IF ID IF bne add … sub bne sub 6 7 8 9 10 ID EX MEM WB IF ID EX MEM WB IF ID EX MEM 11 IF WB 12 13 BRANCH PREDICTION EXERCISE 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 cycle 7 8 9 10 11 sub IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB IF ID EX MEM bne sub bne sub bne sub 12 13 14 15 16 17 WB 18 19 BRANCH PREDICTION EXERCISE 1101 0000 1101 0100 1101 1000 L1: sub $s0, $s0, $s2 bne $s0, $s1, L1 add $s2, $s2, $s2 cycle 12 13 14 15 16 bne IF ID EX MEM WB IF ID IF ID sub bne add 17 18 19 EX MEM WB IF 20 21 22 23 24