1

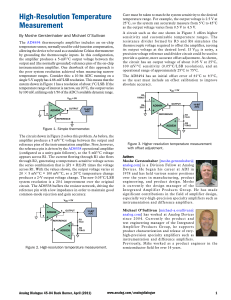

advertisement