Design for MOSIS Educational Program (Research) Low Power Differential Oscillator Design

advertisement

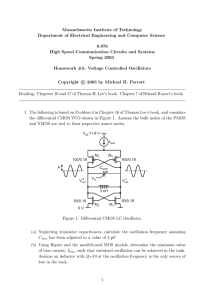

Design for MOSIS Educational Program (Research) Low Power Differential Oscillator Design Design No.: 84305, Fab_ID: UTK_ARTHAS Prepared by: Kai Zhu, Ashraf Islam, M. Shahriar Jahan, Melika Roknsharifi, Dr. Jeremy Holleman and Dr. Syed Islam Institution: Department of Electrical Engineering and Computer Science, The University of Tennessee, Knoxville, TN-37996-2100 Date of Chip Submission: Sept. 30th, 2010 Estimated Project Size: 16 mm2 in IBM9RF 90nm CMOS process Project Description With the increasing demands on the biomedical electronics, the development of high-performance integrated circuits with low power consumption has attracted great attention in recent years. Being a crucial building block in a communication system, the phase-locked loop (PLL) is recognized as one of the most power-consuming components. It is desirable to implement the PLL circuit for minimum power consumption while maintaining the desirable performance such as the phase noise and output power to satisfy the system specifications. In a typical PLL for wireless radio-frequency (RF) application, there are several blocks: voltage controlled oscillator (VCO), frequency divider (FD), phase frequency detector (PFD), charge pump and loop filter. Among them the VCO and FD consumes the most current in the system [1]. Therefore, to reduce the power consumption of the PLL, these two blocks must be optimally designed for extremely low power. In this design, we’re targeted for designing an low-power oscillator with the total current of 20 µA for the PLL system, while obtaining the phase noise of -60 dBc/Hz @10KHz and -100 dBc/Hz@1MHz for biomedical system. Differential ring oscillator is used for low power consideration. Maneatis load-based ring oscillator [2] is chosen for good noise performance and better control of the oscillating frequency. 2. 5 µA current is fed for the Itail in each stage. Fig. 1 shows the buffer low-power topology used in this design. VDD VOUT - VCNTL VOUT + VIN + VIN - Itail Fig. 1 Maneatis Load Low Power Buffer. Three stages are selected to build the ring oscillator for trade-off between low power and good noise performance. + + - - + + - - + + - - VOUT + VOUT - VCNTL Fig. 2 Fully-Differential Ring Oscillator with three stages. AgilentTM N9010A Signal Spectrum Analyzer is employed to test the circuits. Fig. 3 shows the output spectrum with VCNTL = 0.5V and 5 μA to each stage. Fig. 3 Output spectrum with VCNTL = 0.5 V, Ibias = 5 μA, output power = -1.99 dBm . The phase noise performance under this condition is -60 dBc/sqrtHz at 10 KHz offset, and -94 dBc/sqrtHz at 1MHz offset. VCNTL can changes from 0V to 1V. But different voltages can not only achieve different frequencies, but also get different noise performance. Fig. 4 shows the output spectrum with VCNTL = 0.35 V, where the frequency is about 132.9 MHz. However, the phase noise at 10 KHz offset also changes to -56 dBc/sqrtHz and -88 dBc/sqrtHz. Fig. 4 Output spectrum with VCNTL = 0.35 V, Ibias = 5 μA, output power = -1.39 dBm. Table I shows the summary of the ring oscillator. TABLE I SUMMARY OF THE RING OSCILLATOR Process Power supply Area Power consumption Output power Phase noise (@113.7 MHz) Tuning range 90 nm RF CMOS 1V core: 50 μm x 70 μm buffer: 230 μm x 440 μm core: 15 μW buffer: 350 μW -1.99 dBm ~ -1.39 dBm @10 KHz: -60 dBc/sqrtHz @1 MHz: -94 dBc/sqrtHz 107 MHz ~ 145 MHz Fabrication Process The IBM 90nm 9RF CMOS process offered through MOSIS is ideal for developing the proposed circuits. Project Size The chip area is 4 mm x 4 mm or 16 mm2. Packaging Requirements We use OCP_LQFP44A for packaging through MOSIS. References [1] Hamid R. Rategh, Hirad Samavati, and Thomas H. Lee, “A CMOS Frequency Synthesizer with an Injection-Locked Frequency Divider for a 5-GHz Wireless LAN Receiver”, IEEE Journal of Solid-State Circuits, vol. 35, no. 5, May 2000. [2] J. G. Maneatis, “ Low-jitter process-independent DLL and PLL based on self-biased techniques”, IEEE Journal of Solid-State Circuits, Vol.31, pp.1723-1732, No.11, Nov 1996.