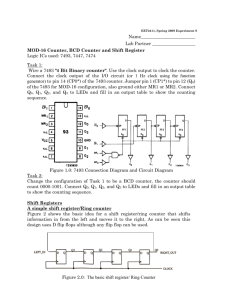

MOSIS REPORT Spring 2010 MOSIS Report 1

advertisement

MOSIS REPORT Spring 2010 MOSIS Report 1 MOSIS Report 2 MOSIS Report 3 MOSIS Report 1 Design of 4-bit counter using J-K flip flop I. Objective The purpose of this project is to design one 4-bit counter using flip flops and implement it on an AMI 0.5um chip. Related Cadence tools are employed to simulate and layout the design. II. Counter structure A digital counter, or simply counter, is a semiconductor device that is used for counting the number of times that a digital event has occurred. The counter's output is indexed by one LSB every time the counter is clocked. A simple implementation of a 4-bit counter is shown in Figure 1, which consists of 4 stages of cascaded negative edge triggered J-K flip-flops. This is a binary counter, since the output is in binary system format, i.e., only two digits are used to represent the count, i.e., '1' and '0'. With only 4 bits, it can only count up to '1111'. Figure.1 A Simple Ripple Counter Consisting of J-K Flip-flops As one can see from Figure 1, the J and K inputs of all the flip-flops are tied to '1', so that they will toggle between states every time they are clocked. Also, the output of each flip-flop in the counter is used to clock the next flip-flop. As a result, the succeeding flip-flop toggles between '1' and '0' at only half the frequency as the flip-flop before it. This type of binary counter is known as a 'serial', 'ripple', or 'asynchronous' counter. The name 'asynchronous' comes from the fact that this counter's flip-flops are not being clocked at the same time. An asynchronous counter has a serious drawback - its speed is limited by the cumulative propagation times of the cascaded flip-flops. A counter that has N flip-flops, each of which has a propagation time T, must therefore wait for duration equal to N * T before it can undergo another transition clocking. A better counter, therefore, is one whose flip-flops are clocked at the same time. Such a counter is known as a synchronous counter. A simple 4-bit synchronous counter is depicted in Figure 2. Figure.2 A Simple Synchronous Counter Consisting of J-K Flip-flops and AND gates The 4-bit counter I designed for this project is based on Figure.2, while it also has serial carry look ahead and synchronous reset which allows all the output set to “0” by the user. III. Flip flop design Flip flops are fundamental building block in this 4-bit counter. A flip flop (FF) is a storage circuit that changes states on the rising or falling edge of a clock signal. There are many flip flop designs such as SR (Set-Reset) flip flop, D (delay) flip flop; T (toggle) flip flop and JK (Jump Key) flip flop. One negative edge triggered J-K flip flop is chosen in this design because it is a universal flip-flop that can be configured to work as an SR flip-flop, a D flip-flop, or a T flip-flop. IV. Design steps Cadence tools are employed in this design to implement the circuit. Basic design steps are illustrated below in Figure 3. Figure. 3 Flowchart of design steps V. JK flip flop The basic characteristic table of JK flip flop is shown in Table 1. Table 1 characteristic table of JK flip flop R 0 0 0 0 1 J 0 0 1 1 d K 0 1 0 1 d Qn+1 Qn 0 1 Qn' 0 The most common approach for constructing an edge-triggered flip flop is to use a master-slave configuration. The schematic of this circuit is shown in Figure. 4 Figure. 4 Schematic of JK flip flop The circuit works as follows: On the high phase of the clock, the master stage is transparent, and the J-K inputs are passed to the master stage output, QM and QMB. During this period, the slave stage is in the hold mode, keeping its previous value by using feedback. On the falling edge of the clock, the master stage stops sampling the input, and the slave stage starts sampling. During the low phase of the clock, the slave stage samples the output of the master stage (QM), while the master stage remains in a hold mode. The value of Q is finalized right before falling edge of the clock, achieving the negative edge-triggered effect. The circuit layout is also depicted in Figure 5. Figure 5 Layout of JK flip flop VI. 4-bit counter The truth table for 4 bit counter is, Table 2 Truth table for 4-bit counter RESET 0 0 0 0 0 0 0 States CLA (carry-out) 0 0 0 0 0 0 0 F3 0 0 0 0 0 0 0 F2 0 0 0 0 1 1 1 F1 0 0 1 1 0 0 1 F0 0 1 0 1 0 1 0 Count 0 1 2 3 4 5 6 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 1 1 1 1 1 1 1 0 1 0 0 0 0 1 1 1 1 0 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 The counter has been designed with J-K flip flops with their inputs shorted. In addition, look ahead function is implemented using NAND gates. The schematic of this counter is in Figure. 6. Figure.6 schematic of 4-bit counter In transistor level, the design was done using the minimum gate length of 0.6μm. This minimum length has been adopted everywhere in the design and the width of each n-MOS and p-MOS transistor was chosen as 3.0μm to maximize the speed. For simplicity the widths were kept same everywhere, as it does not hinder the correct functionality of the circuit and helps keeping the total chip area to a minimum. The layout of this counter is in Figure. 7. All of three metal layers are used to minimize the area. Parallel power supply metal lines are also designed to avoid electro-migration. The total area is 422um*42um=0.018mm2. Figure 7 Layout of 4-bit counter VII. Simulation results 1). Schematic simulation 7 8 9 10 11 12 13 14 15 0 The 4-bit counter has been simulated under different clock frequencies from 1MHz to 100MHz. Figure 9 shows the simulation results under clock frequency of 50MHz. One can notice once the reset is set to 0, the counter begins to work. Figure 8 Schematic simulation of 4-bit counter (CLA is the look ahead) Figure 9 Post layout simulation of 4-bit counter 2). Post layout simulation The post layout simulation has been conducted using the same clock frequency (50MHz). 3). Performance of 4-bit counter The rise and fall time (10%-90%) and delay of each output have been measured under different load capacitance. The following graphs show both the rise and fall time and delay are increased linearly with the load capacitance. The clock frequency is set to 1MHz this time. 120.0 110.0 100.0 90.0 80.0 70.0 60.0 50.0 40.0 30.0 20.0 10.0 0.0 120.0 110.0 100.0 90.0 80.0 70.0 60.0 50.0 40.0 30.0 20.0 10.0 0.0 F0 rise time(ns) F0 fall time(ns) 0 1 0 2 3 4 5 Load capacitance (pF) 1 120.0 110.0 100.0 90.0 80.0 70.0 60.0 50.0 40.0 30.0 20.0 10.0 0.0 2 3 4 Load capacitance (pF) Figure 11 Rise and fall time of F1 2 3 4 5 Figure 12 Rise and fall time of F2 F1… F1… 0 1 Load capacitance (pF) Figure 10 Rise and fall time of F0 120.0 110.0 100.0 90.0 80.0 70.0 60.0 50.0 40.0 30.0 20.0 10.0 0.0 F2… 5 F3… F3 fall… 0 1 2 3 Load capacitance (pF) 4 Figure 13 Rise and fall time of F3 5 54.0 52.0 50.0 48.0 46.0 44.0 42.0 40.0 38.0 36.0 34.0 32.0 30.0 28.0 26.0 24.0 22.0 20.0 18.0 16.0 14.0 12.0 10.0 8.0 6.0 4.0 2.0 0.0 F0 delay (ns) F1 delay (ns) F2 delay (ns) F3 delay (ns) 0 1 2 3 Load capacitance (pF) 4 5 Figure 14 Propagation delay of all outputs VIII. Test result The taped out chip has been tested under different clock signals using breadboard setup, including 10 KHz, 500 KHz, and 2 MHz. Since the breadboard has quite a bit parasitic capacitance and inductance, no extra load capacitors are added to the output. Figure 16, 17 and 18 show the transient response of circuit outputs F0, F1, F2, and F3 (Bottom to Top traces) under 10 KHz, 500 KHz, and 2 MHz clock frequency, respectively. Figure 15 Transient response under 10KHz clock frequency Figure 16 Transient response under 500 KHz clock frequency Figure 17 Transient responses under 2 MHz clock frequency The rise time for each output is around 60ns, while the fall time is around 160ns. IX. Conclusion In this project we implemented a 4-bit counter on a 0.6um chip. The counter is found in many digital Circuits, such as digit clock, PLL, and timing circuits. This counter is based on master slave J-K flip flop which also has features of look ahead output and synchronous reset. Post layout verification has been done and is ready for tape out. MOSIS Report 2: Design 4 bit counter For a 4bit counter we need 4 flip flops. Each flip flop generate one bit of the output. The blew truth table shows the relation between each flip flop input and output of previous state: Present Next D3 D2 D1 D0 State State 0000 0001 0 0 0 1 0001 0010 0 0 1 0 0010 0011 0 0 1 1 0011 0100 0 1 0 0 0100 0101 0 1 0 1 0101 0110 0 1 1 0 0110 0111 0 1 1 1 0111 1000 1 0 0 0 1000 1001 1 0 0 1 1001 1010 1 0 1 0 1010 1011 1 0 1 1 1011 1100 1 1 0 0 1100 1101 1 1 0 1 1101 1110 1 1 1 0 1110 1111 1 1 1 1 1111 0000 1 0 0 0 From above table we can find the relation of D 0 and its output Q0: 00 01 11 10 Q1Q0 Q3Q2 00 1 0 0 1 01 1 0 0 1 11 1 0 0 1 10 1 0 0 1 And the input is connected to the “Clock”, therefore if we use a rising edge D-flip flop, in each rising of input the output will toggle; there we can understand that the frequency of output is a half of input frequency. This is shown in figure blew: For Q1 , Q2 and Q3 we need this frequency division as well. It can be seen in first table that in rising edge of Q0, Q1 should toggle, in the rising edge of Q1 , Q2 should toggle and in the rising edge of Q 2 , Q3 should toggle. Therefore we can connect every output of each D-flip flop to its input (D) and then connect the Clock to the output of previous stage. Complete circuit of 4 bit counter will look like blew: We can see the 7 buffers are added in the 3 input and 4 output of circuit. For D-flip flops, the rising edge flip flop is used, which is shown blew: But to add Set, Reset and Hold to this counter, the input of NOT No. 7 and N0. 8 should be under control. Therefore we used a set and reset system for NOT No. 5 and 6 to control the input of NOT No. 7 and 8. The same NOT is used to control the input of NOT 3 and NOT 4, to reset the memory of DFF, and do the counting from beginning and do not hold the data. Picture of these NOTs with reset and set is shown blew: Set Reset 0 0 0 1 Output 1 Not- allowed 1 0 1 1 Normal NOT of A and B 0 The reset and set of NOT No. 3,4,5 and 6 are being controlled by an output SET and RESET pin. Set Reset Mode Out of Out of Out of NOT3 NOT4 NOT5 Out of NOT6 0 0 Counting Defined by input Defined by input Defined by input Defined by input 0 1 Reset 0 1 1 0 1 0 Set 1 0 0 1 1 1 Hold 1 1 1 1 Set Reset Mode NOT3 NOT4 NO Set3 Reset3 Set4 Reset4 Set5 0 0 Counting 1 0 1 0 1 0 1 Reset 1 1 0 0 0 1 0 Set 0 0 1 1 1 1 1 Hold 0 0 0 0 0 Therefore we can find the required control signals: Set3=Set6= Reset3=Reset6= Set4=Set5= Reset4=Reset5= Final circuit of D-flip flop looks like blew: The layout of the entire 4 bit counter is shown blew: For testing the post layout simulation a circuit like blew is used: The result of post layout simulations without set and reset are shown blew: The result of post layout simulations with Set and Reset and Hold activated are shown blew: 1. 2. 3. 4. 5. Summary of what has been achieved in this project: 4 bit counter with Set, Reset and Hold (W/L)p=7.5u/0.6u , (W/L)n=1.5u/0.6u 4 stage Buffers in inputs and outputs Max Delay=7ns, Max rise time=2ns Area= 282um*294um Chip Test Results: Output result for input frequency of 10KHz Output results for input frequency of 800KHz Rise time and fall time in the edges in the above figure is shown below: Report 3 I. Objective: The objective of this project is to design a 4-bit counter and implement it into a chip with the help of Cadence (custom IC design tool) AMI 0.6 micron process following necessary steps and rules dependent on selected process technology. II. Selection of Counter design: The chosen design for the 4-bit counter is a simple 4-bit synchronous. The reasons behind choosing this design are i. ii. iii. III. Synchronous counter is the most used and reliable counter design Synchronous design ensures that all the output bits change simultaneously at the edge of a clock signal and holds that output until the next clock signal Low propagation delay than asynchronous counter Selection of Flip-flop: The basic building block of a counter is flip-flop. The choice of flip-flop depends on the logic function of the circuit. The logic function of the counter suggests a D flipflop as most appropriate for the design. So a positive edge triggered D flipflop was chosen for counter design. The flipflop was built using transmission gates and inverters, so the number of transistors required was reduced to 20, which is quite low compared to conventional NAND/NOR gate design. IV. Design Steps: Cadence is one of the most popular, efficient and commercial custom IC design tool widely used for transforming a design idea to fabrication. For fruitful production of an IC from a design concept a sequence of steps has to be followed. The flow chart below describes these steps- Design Specification Schematic Capture Create Symbol Simulation Layout DRC- Design rule Check Extraction LVS - Layout vs Schematic Check Post layout Simulation V. Truth tables and K-maps: Present State Next State Q3 0 0 0 Q2 0 0 0 Q1 0 0 1 Q0 0 1 0 Q3* 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 0 0 1 0 1 0 0 0 1 1 1 0 0 1 1 1 0 1 1 0 0 1 0 0 1 1 1 1 1 0 0 0 0 1 1 1 0 1 1 1 1 1 1 1 0 0 1 1 1 1 Flip Flop Input Q2* Q1* Q0* 1 0 1 D3 0 0 0 D2 0 0 0 D1 0 1 1 D0 1 0 1 0 0 1 0 1 0 0 0 0 1 1 1 0 0 1 0 1 0 1 0 0 1 0 0 1 0 1 0 1 1 1 0 0 1 0 0 1 0 1 1 1 1 0 0 1 1 1 0 0 1 0 1 1 1 0 0 1 1 1 0 0 1 0 0 1 0 1 1 1 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 0 1 1 1 0 1 1 0 0 0 0 0 0 0 0 K-maps: Q1Q0 Q3Q2 00 01 11 10 00 01 11 10 0 0 1 1 0 0 1 1 0 1 0 1 0 0 1 1 Q1Q0 Q3Q2 00 01 11 10 00 01 11 10 0 1 1 0 0 1 1 0 1 0 0 1 0 1 1 0 D3 Q1Q0 Q3Q2 00 01 11 10 D2 00 01 11 10 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 D1 Q1Q0 Q3Q2 00 01 11 10 00 01 11 10 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 D0 Logic function: Logic circuit: Schematic of 4-bit counter: Figure 1: Schematic diagram of 4-bit counter VI. Required Basic building blocks: D Flip-flop: D flip flop used in for this circuit for reliable operation and compression. The flip flop triggers at positive edge of the clock cycle. Truth table for the JK flip flop is given below: Schematic of D flip flop: Figure 2: Schematic diagram of D flip flop Layout: Layout was drawn in AMI 0.6 micron process. All the building blocks used in the layout have the same height to maintain symmetry. Minimum spacing rule was utilized to reduce the size of layout. Figure 3: Layout of D flip flop Inverter: Figure 4: Layout of inverter A standard inverter was built in AMI 0.6 micron process. To meet the design requirements while building AND gate from 2 input NAND gate, Inverter 2x was also built. Transmission gate: Figure 5: Layout of transmission gate AND gate: Figure 6: Layout of AND gate XOR gate: Figure 7: Layout of XOR gate VII. Complete Layout of counter design: Maximum effort was made to minimize the delay while maintaining standard chip size The complete layout occupies an area = 471.3µm x 66.15µm = 0.0311mm2 Figure 4: Layout of 4-bit up counter Extracted layout with pad frame: Figure 9: Extracted layout including padframe VIII. Pre-layout simulation output: Figure 5: Prelayout simulation output, clock frequency= 10MHz Post layout simulation output: Figure 6: Post layout simulation output, clock frequency= 10MHz Post layout simulation with load: Figure 7: Post layout simulation output, clock frequency= 10MHz, C_load= 5 pF IX. Measurement of rise time and fall time and propagation delay: Capacitive loading was varied from 1pF to 15pF and rise time, fall time and propagation delay was measured. During rise time and fall time measurement time required to change from 10% to 90% of maximum voltage was measured. The propagation delay was measured at 50% point. Time measurement was taken for all four output bits. Plot of response time Vs Capacitive load: Figure 8: Plot of Rise time, fall time Vs Capacitive load Figure 9: Plot of propagation delay Vs Capacitive load Discussion: Above plots show that the rise time, fall time and delay linearly varies with the capacitive loading. This indicates the liner behavior of the designed circuit. It may be noticed that the fall time higher than the rise time. This is because during fall time the capacitive loads discharges through the NMOS to reach ground potential. In this design a large number of NAND gates are used which has number of NMOS in series. The series connected NMOS has a larger resistance and has greater RC delay which leads to the higher value of fall time. Since in NAND gates PMOS are connected in parallel they quickly charge the load capacitor and give lower rise time. The delay for all four bits are almost equal. All rise time and fall time was measured for 10MHz clock frequency. At this frequency capacitive loading beyond 15pF produces signal that cannot be recognized as ‘1’ or ‘0’. At lower clock frequency higher capacitive loading is possible. X. Application: Counter is used widely in number of digital and analog circuit. There are vast applications of counter in the field of electronics. Some of them are listed belowI. A counter can be used as frequency divider. This 4-bit counter can be efficiently used to get four different frequencies up to one sixteenth times of the original clock frequency. II. III. IV. Counter can be used on building entrances to keep track of number of people entering or leaving. Counter can be used in digital logic deigns to perform certain operation at certain steps. Counters are also applicable in timer circuit to turn on/ off a device after certain time with use of a proper logic function.