Electrical & Computer Engineering ECE 491 Introduction to VLSI

advertisement

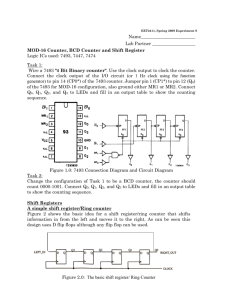

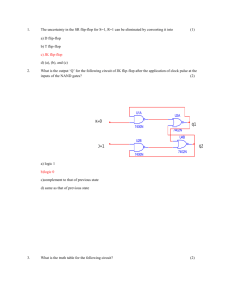

Electrical & Computer Engineering ECE 491 Introduction to VLSI Report 1 Marva` Morrow INTRODUCTION Flip-flops are synchronous bistable devices (multivibrator) that operate as memory elements. A bistable multivibrator is one that exhibits two stable states. It is commonly used as basic building block for counters, registers, and memories. A flip-flop circuit contains two outputs, one is for the normal value and the other is for the complement value of the stored bit. There are different flip-flops that could have been chosen for this particular project; J-K, T or D Flip-Flop. The specific composition picked for this project was the D Flip-Flop. The D Flip-Flop is just a modification of the clocked SR Flip-Flop (See Figure 1), as are the rest of the flip-flops. Figure 1: SR Flip-Flop Diagram The D input goes directly into the input of the R connection and the complement of the D input goes into an inverter that acts as the input of the S connection. The D input is then sampled during the occurrence of an input that is the Clock (See Figure 2). Figure 2: D Flip-Flop Diagram When sampling the D input, if the output is 1, the flip-flop is switched to the set state. If the output is 0, the flip-flop switches to the clear state (See Figure 3). 2 Figure 3: Transition Table of D Flip-Flop One main point about the D Flip-Flop, which is not in the RS or the J-K Flip-Flop, is that when the clock input falls to logic 0 and the output can change the state, the Q output always takes the state of the D input at the moment of the clock edge. PROJECT APPLICATION Figure 4: Designed D Flip-Flop using 9 NAND gates This application shown is a modified version of one flip-flop design in which the bottom application is an inverter. After performing some research on this particular design, it was noticed that a NAND gate with the inputs tied together (Figure 5) could be used to imitate an inverter. 3 Figure 5: NAND gate with inputs tied together acting as inverter The next step is to run the Spectre Simulation on the Schematic and change the schematic source code file (Figure 6) to generate a set of output waveforms (Figure 7), as performed in previous labs. Figure 6: Schematic Source code .inp file This change will be done by the same method of including the Model Files that were created in the Lab project 2. The other change that needs to be made is adding the Spectre Source Statements for the sources and inputs (D and Clk). 4 Figure 7: Generated Waveform Output of the Schematic After inspecting this process, it was noticed that a slight delay existed on the output. This delay could be caused from a number of elements after, checking the schematic again and doing more research the results were the same therefore it was necessary in completing this project that the next step be accessed. From the schematic design and from the information gained from the Internet, a symbol for the D Flip-Flop (Figure 8) was not a difficult task to achieve. 5 Figure 8: Generated symbol of the designed D Flip-Flop This next particular section of the process is considered to be most difficult section because of its complexity. This section is implementing the layout of the laboratory from a series of NAND gate layouts (Figure 9) that were completed in the previous lab. 6 Figure 9: NAND gate layout that will be used to create D Flip-Flop Figure 10: Layout of the designed D Flip-Flop 7 This layout (Figure 10) was thought to be the simplest because it places all the elements (NAND gates) side by side and makes it easier when connecting the specific gates together. The system of tying the gates together were taken from the schematic in which the process is to tie the input or output to its specified component whether it be input, output or the clock. Once the layout is constructed to its desired presentation, it is necessary to run a DRC (Design Rule Check) on the layout to make sure it has no errors associated with it. Once the DRC is complete the next step is to create an extracted view (Figure 11) of the layout. This specific process accesses the layout in order to correctly identify the supplies, gates and connections that are tied together. Figure 11: Extracted View of the designed D Flip-Flop Once you have completed this portion of the laboratory it is necessary to run the Spectre Simulation again, but this time with the layout. The same process is followed, by editing the Source File (Figure 12) for the layout. 8 Figure 12: Extracted Source code .inp file Once this step is complete and you save this file, it is necessary to run the simulation and get the output waveforms (Figure 13) for the layout. 9 Figure 13: Generated Waveform Output of the Extracted As you can see from the Extracted Waveform Output, there is also a delay but this time the curve is smoother at the beginning of the process than that of the Schematic Waveform Output. Once this is realized and the Waveform Outputs are viewed a similar then the next step to take is to run the LVS (Layout Versus Schematic) process in order to determine if the two processes are, in fact, identical. This process is a simple one to perform but could be a big problem to correct. Once this is complete the output should be viewed for net list matching (Figure 14). 10 Figure 14: Output of LVS to show that the netlists match This is the most important part of the entire project and for this reason it is imperative the netlist match, if they do not then the error should be sought, if possible, and corrected. In this case, they are identical. The next few processes were to estimate the rise and fall times of each individual section of the project. 11 Figure 15: Schematic Waveform Output with rise time (30% - 70%) The estimated rise time is ≅ 218.805 psec 12 Figure 16: Schematic Waveform Output with fall time (70% - 30%) The estimated fall time is ≅ 147.013 psec 13 Figure 17: Extracted Waveform Output with rise time (30% - 70%) The estimated rise time is ≅ 176.952 psec 14 Figure 18: Schematic Waveform Output with fall time (70% - 30%) The estimated fall time is ≅ 254.441 psec CONCLUSION The end results for each section are designated in their specific section and the end Area of this layout was shown to be ≅ (69.15 µm * 127.8 µm) = 8837.37 µm2. This project seemed very straightforward and was not very difficult except for when encountering the layout portion of this lab. The laboratory process was a simple on to design once the information of each different design was reviewed (T Flip-Flop, J-K Flip-Flop, and the selected D Flip-Flop). This project was really in depth and was considered to be a culmination of all the labs that were performed for this class. I really enjoyed the process of this project process except trying to debug the layout portion of the lab. 15 Report 2 Contents: 1) Abstract 2) Introduction 3) 1-bit cell development a. schematic b. layout 4) 4-bit cell development a. schematic b. layout 5) Results a. 1-bit b. 4-bit, c. LVS matching 6) Measurements and plots a. Rise time, Fall time and propagation delay b. Effect of loading 7) Summary /Conclusion 16 Abstract: This project involves the design and simulation of a 4-bit counter. This was accomplished in two steps. In the first step a Toggle master-slave flip-flop was designed and verified on the schematic as well as the layout level using the netlist generated by Spectre Simulations. In the second step, simulation and layout of the 4-bit counter was performed. The design was simulated under no load and 4-load conditions to validate the functionality and to estimate the delay involved in each cell. Introduction: Counters are designed using flip-flops in order to have knowledge of the previous state to decide on the next state depending on the inputs applied. Counters can be classified as synchronous and asynchronous counters based on the application of clock to the flip-flops. A synchronous counter is clocked by a single clock for all the stages and the output for each stage changes at the same time. In an asynchronous the output from the previous stage is given as the clock for the next stage so that the output ripples across each stage to reach the final count. I chose to implement an asynchronous counter in this project to test the propagation delay involved in rippling the output across the different stages of the 4-bit counter. The counter was designed for use of few gates and to provide an output that is free of glitches. A binary counter can be realized using T-FFs by counting the number of toggles in the previous stage. The T input of each flip-flop is set to 1 to produce a toggle at each cycle of the clock input. For each two toggles of the first cell, a toggle is produced in the second cell, and so on down to the fourth cell. This produces a binary number equal to the number of cycles of the input clock signal. This device is sometimes called a "ripple through" counter. Using a Master-slave configuration isolates the output from any glitches resulting from any changes happening in the input signal. The master-slave flip-flop is essentially two back-to-back JK flip-flops, but the feedback is to both to the master FF and the slave FF. In this configuration, the master FF sees the input when the clock is high and the output of the first stage holds the input for the next stage. During the clock ‘low’, the slave circuit is enabled to track the change in the input by using the output of the master FF. Thus the master-slave configuration eliminates any sharp change of state within a clock cycle and the FF is free of oscillations. Implementation: The Counter was implemented using the Toggle Flip-flops using 3 levels of hierarchy as: • Implementation of 2 and 3 input NAND gates • Implementation of T-FF using the basic cells developed • Implementation of 4-bit Counter using the T-FFs 17 The following steps were performed for each cell that was developed to realize the counter. • Creation of schematic • Symbol creation • Netlist generation and simulation of the schematic using Spectre • Manual Layout creation • Extraction of the layout • LVS check and post-layout simulation using Spectre • 1-bit Cell: The schematic of the Toggle FF realized using gates is shown below. The FF has 2 stages i.e. the master and the slave stage. The FF requires a clock and an input which when always equal to ‘1’ results in the constant toggling of the output Q and its inverse Q_inv. This schematic was realized and the functionality was tested using the netlist simulation in spectre. Then the symbol for the single slice of the counter was generated and the manual layout was drawn. Layout: The layouts of the individual NAND gates were drawn and the functionality was verified. The size used for the n-mos and the p-mos used for the initial cells were retained in order to maintain consistency across all the cells. NMOS: L = 0.6 µm and W = 4.5 µm PMOS : L = 0.6 µm and W = 1.5 µm The size of a standard 2 input NAND gate was 28.65 µm x 13.2 µm (378.18 µm2) The layout shows that the individual NAND gates are placed side by side to reduce the layout area and for ease of interconnections. 18 The layout structure is 3-IP NAND – 3-IP NAND – 2-IP NAND - 2-IP NAND – INVERTER -2-IP NAND -2-IP NAND -2-IP NAND -2-IP NAND. The layout occupies an area of 2471.0625 µm2 (86.25µm by 28.65µm). The input leads are seen entering in the left side and the outputs of Q and Q_inv are seen leaving at the right side. Thus it is a simple configuration to fabricate. 4-bit Counter: The schematic of the 4-bit Counter realized using 1-bit Counter cells is shown below. There are 4 FFs required for the counter and the enable input of 1 is given to all the FFs. The input clock is required for the first stage only and the output from the Q_inv of the previous stage is used as the clock for the subsequent stages. This schematic was realized and the functionality was tested using the netlist simulation in spectre. 19 Then the symbol for the single slice of the counter was generated and the manual layout was drawn. Layout: The layout shows that the individual TFFs were placed on below the other to use the layout area in an effective manner and for ease of interconnections. 20 The layout structure from the top to the bottom is TFF(Q_3 MSB) – TFF(Q_2) – TFF(Q_1) – TFF(Q_0 LSB) The layout occupies an area of 10000.6875 µm2 (86.25µm by 115.95µm). The input leads are seen entering in the left side and the outputs of Q and Q_inv are seen leaving at the right side. 21 Simulation Results: The results of simulation for a single bit and a 4-bit counter are linked below: 1-bit Counter output waveform: Q_inv Q Enable Clock The waveforms show that the output changes at the negative edge of the clock transition. This is so because the master FF is enabled for the positive transitions and the slave responds to the negative transitions. The frequency of the output is also seen to be half that of the clock and the output toggles for every clock cycle due to the constant ‘1’ input to the toggle FF. 4-bit Counter Waveform: Q_3 (MSB) Q_2 Q_1 Q_0 (LSB) Enable Clock 22 The waveforms show the operation of the 4-bit counter. The Q_0 output which is the LSB toggles for every negative transition of the clock cycle. The output of the next stage follows with toggling depending on the transition of the previous stage and the output for the 4 stages are obtained. It is seen that the counters starts counting from ‘1111’ to ‘0000’ as a count-down counter and then starts again from ‘1111’, thus counting correctly. LVS Results: The result of the LVS run shows that the netlist generated from the schematic and of the layout match perfectly. Measurements: The circuit’s delay plots and measurements have been included below to show the delays involved in the different stages of the counter. The rise time, fall time and the propagation delay involved for no load and load conditions have been simulated and tabulated. The rise time was calculated as the time taken by the output signal to rise from the 0% value of 0V to 70% (3.5V) of the final value. The fall time was found as the time taken by the signal to fall from 100% (5V) to 30% (1.5V) i.e. the t-70% was calculated. The propagation delay was calculated as the time taken by the output signal to ripple out for a given change in the input signal. This was measured as the time taken between the 50% change of the input signal (in this case it is the clock) and the 50% change in the output signal of the different stages in the 4-bit counter. Table showing the delay measurements: Rise Time Load Capacitance No load 1pF 2pF 5pF Q0 296p 4.02n 7.8n 15.6n Q1 309p 4.9n 8.6n 18.6n Q2 311p 4.9n 8.3n 17.9n Fall Time Q3 1.08n 4.869n 7.6n 18n Q0 618p 14.2n 27.3n 64.8n Q1 618p 14.7n 26.5n 66n Q2 618p 14.2n 26.6n 64.5n Propagation Delay Q3 1.7n 14.8n 26.4n 66n Q0 556p 3.1n 5.5n 10.4n Q1 2.1n 7.87n 13.5n 27.5n The plots of propagation delay for various load conditions: 23 Q2 3.6n 12.7n 21.5n 44.6n Q3 5.2n 17.5n 29.5n 62n Delay vs Load Capacitance (Q1) 12 30 10 25 Propagation Delay in ns Propagation Delay in ns Delay vs Load Capacitance (Q0) 8 6 4 2 20 15 10 5 0 0 1 2 0 5 0 Load Capacitance in pF 2 5 Delay vs Load Capacitance (Q3) Delay vs Load Capacitance (Q2) 70 50 60 40 Propagation Delay in ns Propagation Delay in ns 1 Load Capacitance in pF 30 20 10 50 40 30 20 10 0 0 1 2 5 0 Load Capacitance in pF 0 1 2 5 Load Capacitance in pF These measurements show that the delay increases with the increase in the load capacitance value and also illustrates the ripple effect wherein for the output for the last stage to be reflected, it requires the output from the previous stages to ripple out and reach the last stage. This leads to more delay for the output to reach the last stage when compared to the previous stages. Conclusion: Any error that was generated during the DRC or LVS check was corrected and the 4-bit Counter’s functionality has been validated and it works correctly. The layout generated occupies less space and the delays involved were measured. The gds file required for fabrication of this design would be extracted. Thus this project has given a good introduction to the phases involved in designing a circuit for a chip. This counter finds it application in almost all electronic appliances which involves a timer namely in microwave ovens, washing machine etc. Report 2 Introduction 24 This project was assigned to gain a better understanding VLSI layout. The requirements are to design and test a four bit counter. We are allowed total design freedom meaning there are no restrictions on how the counter is to be constructed. We are to choice a design and construct the circuit schematic in Cadence. Then run simulations on the schematic to test for proper execution. Next we are to layout the design making sure we meet all design rules. Finally we do post layout simulation and compare the results to the pre layout simulations. The design will use the logic devices that we created from previous labs. Once the counter works properly we are to do more in-depth testing of the propagation delay and the rise time and fall time of the counter. Theory & Design I choose to use a D flip flop for the project. D flip flops are latches that hold on to a value from the previous state until they are signaled to change. When the clock goes high, what ever value D is gets transferred to Q. When the clock goes low Q will not change. Basically Q stores the value of D until the clock goes high again. While doing research on counters on the internet, every counter I found was based on a J K flip flop. I wanted to do something different so I kept searching and soon found a simple example of a D flip flop and how to connect the flip flop into a counter. The schematic I found only used 4 flip flops which are a lot less then the other flip flop designs that I encountered. I thought if I could make the counter from such a simple D flip flop that I would end up using less area then other students’ designs. I liked how the design only used NAND gates whereas other designs also used NOR gates. The simple schematic can be seen in Figure 1. Figure 1 First Failed Attempt After drawing the schematics for this simple design, I tested the circuit by simulating it in Cadence. The simulation showed that the counter did not work correctly. I finally realized that maybe this was not the best design for a D flip flop. Searching the internet again, I soon found a better design that still only used NAND gates except this time there were 8 NAND gates and one inverter. Figure 2 Final Design Schematic Figure 2 shows the schematic for the more complex but effective D flip flop. This flip flop is a negative edge trigger, which means that Q will change only on the falling edge of the clock cycle. Several D flip flops can be connected together to form a counter. 25 When D flip flops are connected as shown in Figure 3 they form what is called an asynchronous ripple counter. This is the type of counter I will be using for the project. I constructed the flip flop with 8 two input NAND gates and 1 inverter. I used the symbols I created from the previous labs to construct the schematic. I did not change any of the values for NMOS or PMOS; they are the same as they were in the lab, which is 3u/0.6u for NMOS and 7.5u/0.6u for PMOS. The schematic can be seen in Figure 4. The color has been modified to help the devices standout. Figure 4 Schematic of D flip flop Next I simulated this circuit to make sure that it works correctly. The simulation in Figure 5 shows the correct operation of a negative edge triggered D flip flop. I made the simulation pulse the D input when the clock was low to demonstrate that Q does not 26 change until the next clock pulse, this explains the jump of the red graph in Figure 5. Figure 5 Simulation of D flip flop Next I created a symbol for the D flip flop and began constructing the 4-bit counter. The symbol can be seen in Figure 6 and the schematic for the counter can be seen in Figure 7. Figure 6 Symbol of D flip flop 27 Figure 7 Schematic of 4 bit counter using D flip flops When I finished the schematic of the counter I simulated it to make sure that it did indeed count correctly. The simulation can be seen in Figure 8. A close up of the counter simulation can be seen in Figure 9. I turned the counter into a symbol as well that is shown in Figure 10. Figure 8 Simulation of Counter Schematic 28 Figure 9 Close up of Counter Simulation Figure 10 Counter Symbol 29 Layout After simulating the counter to make sure it works properly, I began creating the layout for the D flip flop. I placed the 8 NAND gates as strategically as I could to minimize the area. The gates and wires are squeezed as tightly as allowed by the design rules. I periodically had to go back and fix areas that were to close after running the Design Rule Check in Cadence. I enjoyed how Cadence allowed you to change a single gate and it would propagate through the design. This made the layout a little easier because I did not have to change all 8 NAND gates. Although, I did end up making the design harder on my self because I did not realize that I could use metal 3. This should make my layouts more impressive since I only used two types of metal. The layout for the D flip flop can be seen in Figure 11. The inputs and outputs are visible in the image. Once I had the layout for the D flip flop I just copied it 4 times into the layout for the counter. I arranged the D flip flops in a way that minimizes the amount of metal needed to connect them. The layout of the 4-bit counter can be seen in Figure 12. Figure 11 Layout of the D flip flop Figure 12 Layout of the 4 bit counter 30 There is only one input to the 4-bit counter, which is the left most metal contact in Figure 12 and this is for the clock signal. There are 4 outputs, one for each bit in the counter; they can be seen as the 4 highest metal contacts in Figure 12. The outputs are from left to right as follows; bit zero, bit one, bit two, and bit three. Where bit zero is the least significant bit and bit three is the most significant bit. The layout design for the counter only uses an area of 15,371 µm2. Post Layout Simulations After completing the layout, I extracted the parasitic capacitances and preformed the same simulations as before, only this time the capacitances are taken into consideration. I also calculated the rise, fall, and delay times for the counter. Figure 13 shows the extracted layout. The correct performance of the counter can be seen from the post simulation graph in Figure 14. Figure 13 Extracted layout of counter Figure 14 Post simulation of 4 bit counter, notice the delay 31 A close up of the post simulation can be seen in Figure 15 it shows the delay slope in more detail. Figure 15 Close up to show delay in counter layout The following table details the rise and fall times for all of the outputs of the counter. These measurements are based on the 90 – 10 method. Bit value Rise time Fall time Bit 3 239.92ps 401.223ps Bit 2 987.68ps 981.046ps Bit 1 980.716ps 978.695ps Bit 0 984.448ps 981.968ps Table 1 Detailing rise and fall times for the outputs I also measured the delay of different capacitive loads. I took several measurements then found where the delay values seemed to change rapidly and I took more concentrated values at that point, a graph of the delay values I found can be seen in Figure 16. The 32 graph shows that as the capacitive load decrease the delay will decrease. The delay seems to level out around 4 nanoseconds. Delay vs capacitance 80 70 60 Pico Farad 50 40 Delay vs capacitance 30 20 10 0 0.001 0.01 0.1 1 10 Delay nano seconds Figure 16 Delay of various capacitive loads Conclusions This project met its goals in that I am now a more proficient user of Cadence layout tools. I now understand more about digital logic layout and digital devices. I designed a working 4-bit counter from the ground up and proved that it worked with simulations. I encountered several problems such as a design that does not work, and having to relocate different parts of the layout because they did not meet the design rules. I have since learned to check the DRC more often. Report 3 33 CONTENTS ABSTRACT 1. Introduction 1.1 Project overview 1.2 JK Master Slave Flip Flop 1.3 Designing of a 4- bit Counter 1.4 Standard Height cell Format 2. Design and Implementation 2.1 Schematic of 1 – bit slice 2.2 Design of 4 – bit slice 3. Results SUMMARY 34 ABSTRACT This project involves the design and the simulation of a 4 bit counter. In the first part of the project, a one bit slice of a flip flop is drawn manually and then a schematic of JK Master-slave flip flop was designed. A layout was designed using Virtuoso and in all the cases the layout was verified using Spectre Simulation. In the second part, a 4 bit counter was designed using the 1 bit slice of the counter. It is simulated under no load, and by including some capacitances to validate its functionality and to calculate the rise time, fall time and delays. 1. INTRODUCTION 1.1 Project Overview: In this project, a standard cell design approach was used to generate the layout of Application Specific Integrated Circuit (ASIC). All the guidelines and design rules are followed in designing the layout. Firstly, a 1 bit slice of JK Flip Flop schematic was obtained and then the layout of JK Master-Slave Flip Flop was generated using Prolific and simulated using Spectre. The widths of the NFETS and PFETS were kept unchanged. 35 Secondly, a cell layout of 4 – bit Binary Counter was generated and simulated. The schematic of the 4 bit counter was designed and it is replicated for 4 bits and the final layout was designed and simulated using Pre-Spectre and Post-Spectre simulation. A binary counter can be constructed from J-K flip flops by connecting the clock to the next counter inverted output. The J and K inputs of each flip flop are connected together to form a T flip flop to produce a toggle at each cycle of the clock input. For each two toggles of the first cell, a toggle is produced in the second cell and so on till the fourth cell. Thus a 1-bit slice of a JK flip flop is implemented and then it is extended to design a 4 bit binary counter. 1.2 JK Master Slave Flip Flop: The J-K flip-flop is perhaps the most widely used type of flip-flop. Its function is identical to that of the S-R flip flop in the SET, RESET and HOLD conditions of operation. The difference is that the J-K flip-flop does not have any invalid states. In other words, the JK flip-flop is an SRFF with some additional gating logic on the inputs which serve to overcome the SR=11 prohibited state in the SRFF. A simple JKFF is illustrated below 36 One way of overcoming the problem with oscillation that occurs with a JK Flip-when J=K=1 is to use a so-called master-slave flip-flop which is illustrated below. The master-slave flip-flop is essentially two back-to-back JKFFs and the feedback from this device is fed back both to the master FF and the slave FF. Also the NAND gates may have any number of inputs. The behavior of JK flip flop is completely predictable. Any input to the master-slave flip-flop at J and K is first seen by the master FF part of the circuit while CLK is High (=1). This behavior effectively locks the input into the master FF. An important feature here is that the complement of the CLK pulse is fed to the slave FF. Therefore the outputs from the master FF are only seen by the slave FF when CLK is Low (=0). Therefore on the High-to-Low CLK transition the outputs of the master are fed through the slave FF. This means that the at most one change of state can occur when J=K=1 and so oscillation between the states Q=0 and Q=1 at successive CLK pulses does not occur. 1.3 T Flip Flop: Firstly, a JK flip flop was implemented in this project and the by shorting J and K a T flip flop was designed. The T input is the CLK input for other types of flip flops. The T or "toggle" flip-flop changes its output on each clock edge, giving an output which is half the frequency of the signal to the T input. 37 It is useful for constructing binary counters, frequency dividers, and general binary addition devices. Counters can be designed in many ways. They can be broadly classified into Synchronous and Asynchronous counters. Asynchronous counters do not have a common clock that controls all the flip-flop stages. The control clock is input to the first stage, or the LSB stage of the counter. The clock for each stage subsequent is obtained from the flip-flop from the prior stage. This type of counter is also known as “Ripple Counter”. 1.4 Standard Height Cell Format: The standard-height in this design is 96-lambda. The W/L of pfet is 15/2, and nfet is 15/6. The following rules for standard-height cells were followed. • All the standard cells share the same height. • The wells must be as indicated on the sides of the cell. However, the center of the design can have the NMOS and PMOS transistor in any configuration so long as no DRC errors occur in the spacing. • The vdd and gnd supply must be labeled as vdd! and gnd!. • The final cell must have the left-bottom corner positioned at the left-bottom corner of the grid. 38 2. DESIGN AND IMPLEMENTATION 2.1 Schematic of 1 – bit Slice: A 1-bit slice which is a T flip flop was implemented. First, the 1-bit slice schematic was built using Cadence Composer and pre-layout simulations using Spectre were performed. A manual layout from the Composer schematic that conforms to the standard-height format was produced using Virtuoso. Lastly, a manual layout from the Composer schematic that conforms to a bit-slice format was produced by Virtuoso. After the layouts were generated in these cases, DRC checks and post-layout simulations were performed. 2.2 Design of a 4 – bit Slice: In this design, 4- bit slice schematic was implemented from 1 – bit slice of the counter using Cadence composer, then a layout is drawn using Virtuoso and post layout simulations are performed. Thus the delay for each bit is calculated. The LVS was 39 checked for correctness of all the connections at the input and output. The waveforms are obtained for the counter. Steps involved in designing a 4 bit counter: • A schematic is designed. All the gates and inverter are imported from other libraries. • A pre-layout spectre simulation is performed. • A layout is generated using Virtuoso based on the schematic. • The extracted view and LVS results are obtained. • The Post-layout spectre simulation gives the results. 3. RESULTS The input value T is kept all time high. As the value is high at the negative edge clock, the output Q will toggle. The layout and simulation should be performed thoroughly for better results. Also a graph, delay Vs Capacitance is plotted. Length X Width : 328um X 112.950um Area : 37047.6 (um) Rise Time (ns) : 0.6ns Fall Time (ns) : 1.2ns 40 SUMMARY This project is to design a 4 – bit binary counter in chip level. The layout obtained from the prolific tools is accurate. The DRC errors have to be eliminated during the process of plotting and the layout should be compact in order to decrease the area of the layout while implementing it on a chip. 41 References: 1. Digital Integrated Circuits – Ken Martin 2. Digital Design – M. Morris Mano. 42 Report 4 Contents Introduction……………………………………………………………..3 Project Overview………………………………………………………..4 T- Flip Flop Schematic………………………………………………....5 T-Flip Flop layout…………………………………………………….…6 Post Spectra simulation of Flip Flop………………………………….…7 Schematic 4 Bit Counter…………………………………………………8 Layout 4 Bit Counter…………………………………………………….9 Rise Time & Fall Time…………………………………………………..12 Delay Vs Load Capacitance……………………………………………...14 Summary…………………………………………………………….…...15 References……………………………………………………………….15 43 Introduction A Sequential network is a digital system where the output is determined by both the present input and the result of a previous event. A counter is a device which implements the sequential logic. The Counter is a very critical and integral part of all digital systems, especially as system complexity increases. The counter can be designed in many ways, in general a modulo N counter has N states, labeled 0 thro N-1. It Resets to 0 after the Nth pulse. For a binary counter with K flip-flops N=2k Counters have many applications such as 1. Decade Counters that count from 0..9.0 2. UP/DOWN COUNTERS that have either a steering control or two pulse input lines 3. Divide by N counters 4. Used in various devices such as ATM’s, Watches etc. 44 Project Overview: The counter was built with the help of a T-Flip Flop, The gates used were only a 3 Input Nand Gates a 2 Input Nand gates and an inverter for realizing the design. The outputs of the Flip Flop are q and qinv. The clock is the input given to the first two Nand gates and the inverter. The T-Flip Flop was chosen for its simplicity and to avoid glitches in the output. The flip-flop was asynchronous design where the q inv output of each stage was an input to the next stage. The Layout was drawn with the help of Cadence. The LVS and post spectra simulation was performed also a load capacitance in the rage of 0.5 pf to 12 pf was added and the delay was calculated. The various Delay Vs load Capacitance delay was the plotted on an excel sheet. The graph shows each delay of Individual Bits as well as the “Rise Time” and “Fall Time”. 45 The T Flip Flop Composer Schematic This was the schematic used in the design of the T Flip Flop the clk input is given to the first 2 Nand gates and also the inverter. 46 The T Flip Flop layout The design of the flip flop in cadence, the extracted view is below 47 Post spectra simulation The post spectra simulation was done and the output of the flip-flop is below 48 Schematic of the 4 Bit Counter The Inputs CLK and T are on the left side given to the first flip-flop and output of each flip q inverted is given as an input to the next stage. The output q0 q1 q2 q3 are on the right of each flip-flop. The clock is on the first flip flop and the two J and K pins are shorted to form the T-Flip Flop. 49 Layout of the 4 bit counter The 4 bit counter extracted view, the VDD rail is on the left and GND rail is on the right. The output q0 q1 q2 q3 are on the right of each flip-flop. The clock is on the first flip flop and the two J and K pins are shorted to form the T-Flip Flop. 50 Post Spectra Simulation The LVS was performed to see if the layout is in accordance with the schematic. The net- lists matched which shows that all the nets and transistors are in order. 51 Post Spectra simulation- Waveform 52 Post Spectra simulation-Rise Time Post Spectra simulation-Rise Time 53 Post Spectra simulation- Delay 54 Delay Vs Load capacitance As the load capacitance is increased the delay increases and the output is shown in the graphs below. Also the rise time and fall times are shown. The curves are shown for the individual Bits q1 q2 q3 q4. Delay Vs Load Capacitance 90 80 70 Delay 60 q3 q2 q1 q0 50 40 30 20 10 0 .2pf .5pf .7pf 2pf 4pf 6pf 8pf 10pf Capacitance Q3-Lsb Q0-Msb 55 Summary and Results The 4 bit counter was designed and its working was observed. The design was kept as small as possible. The design specifications are given below. Area of Layout = 170 X 210 um2 Delay Vs Load Capacitance .2pf .5pf .7pf 2pf 4pf 6pf 8pf 10pf q3 1.03 1.49 1.8 3.75 6.76 9.78 12.86 15.88 q2 3.21 4.34 5.09 9.83 17.01 24.01 31.04 37.91 q1 5.38 7.2 8.38 15.88 27.15 38.24 49.13 60.08 q0 7.56 10.05 11.67 21.97 37.41 52.46 67.37 82.18 Rise Time and Fall Times Rise time Fall Time q3 2.9059 9.065 q2 2.9076 9.02 q1 2.908 8.984 q0 2.8668 8.94 Refrences: 1. Digital Integrated Circuit Design by ken Martin 2. http://www.play-hookey.com/digital/ripple_counter.html 56 Test Result 57 58 59 60 61 62 63 64