Boston University ... SC571: VLSI Design Principles ...

advertisement

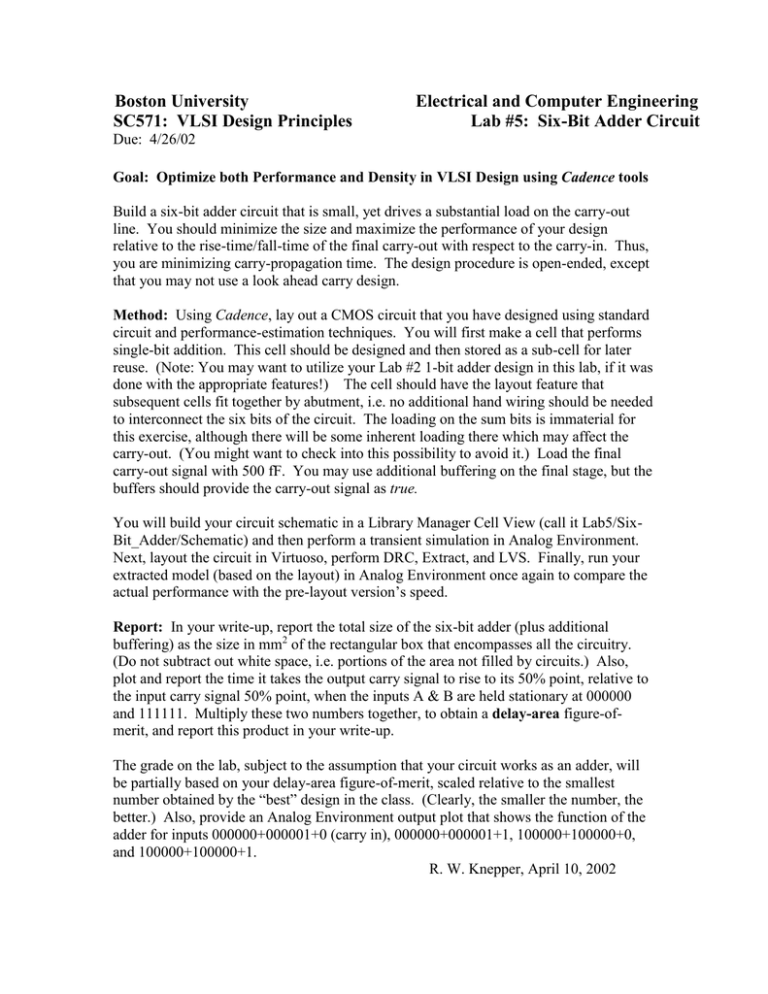

Boston University SC571: VLSI Design Principles Electrical and Computer Engineering Lab #5: Six-Bit Adder Circuit Due: 4/26/02 Goal: Optimize both Performance and Density in VLSI Design using Cadence tools Build a six-bit adder circuit that is small, yet drives a substantial load on the carry-out line. You should minimize the size and maximize the performance of your design relative to the rise-time/fall-time of the final carry-out with respect to the carry-in. Thus, you are minimizing carry-propagation time. The design procedure is open-ended, except that you may not use a look ahead carry design. Method: Using Cadence, lay out a CMOS circuit that you have designed using standard circuit and performance-estimation techniques. You will first make a cell that performs single-bit addition. This cell should be designed and then stored as a sub-cell for later reuse. (Note: You may want to utilize your Lab #2 1-bit adder design in this lab, if it was done with the appropriate features!) The cell should have the layout feature that subsequent cells fit together by abutment, i.e. no additional hand wiring should be needed to interconnect the six bits of the circuit. The loading on the sum bits is immaterial for this exercise, although there will be some inherent loading there which may affect the carry-out. (You might want to check into this possibility to avoid it.) Load the final carry-out signal with 500 fF. You may use additional buffering on the final stage, but the buffers should provide the carry-out signal as true. You will build your circuit schematic in a Library Manager Cell View (call it Lab5/SixBit_Adder/Schematic) and then perform a transient simulation in Analog Environment. Next, layout the circuit in Virtuoso, perform DRC, Extract, and LVS. Finally, run your extracted model (based on the layout) in Analog Environment once again to compare the actual performance with the pre-layout version’s speed. Report: In your write-up, report the total size of the six-bit adder (plus additional buffering) as the size in mm2 of the rectangular box that encompasses all the circuitry. (Do not subtract out white space, i.e. portions of the area not filled by circuits.) Also, plot and report the time it takes the output carry signal to rise to its 50% point, relative to the input carry signal 50% point, when the inputs A & B are held stationary at 000000 and 111111. Multiply these two numbers together, to obtain a delay-area figure-ofmerit, and report this product in your write-up. The grade on the lab, subject to the assumption that your circuit works as an adder, will be partially based on your delay-area figure-of-merit, scaled relative to the smallest number obtained by the “best” design in the class. (Clearly, the smaller the number, the better.) Also, provide an Analog Environment output plot that shows the function of the adder for inputs 000000+000001+0 (carry in), 000000+000001+1, 100000+100000+0, and 100000+100000+1. R. W. Knepper, April 10, 2002