AN-1248 APPLICATION NOTE

advertisement

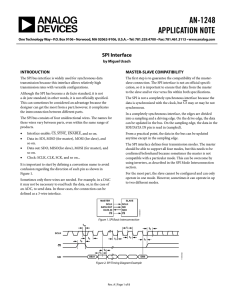

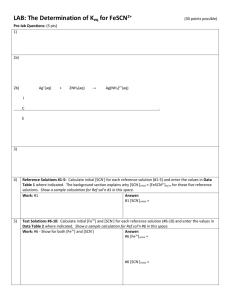

AN-1248 APPLICATION NOTE One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com SPI Interface by Miguel Usach INTRODUCTION MASTER-SLAVE COMPATIBILITY The SPI bus interface is widely used for synchronous data transmission because this interface allows relatively high transmission rates with versatile configurations. The first step is to guarantee the compatibility of the masterslave connection. The SPI interface is not an official specification, so it is important to ensure that data from the master to the slave and/or vice versa fits within both specifications. Although the SPI has become a de facto standard, it is not a de jure standard; in other words, it is not officially specified. This can sometimes be considered an advantage because the designer can get the most from a part; however, it complicates the interconnection between different parts. The SPI is not a completely synchronous interface because the data is synchronized with the clock, but CS may or may be not synchronous. The SPI bus consists of four unidirectional wires. The names for these wires vary between parts, even within the same range of products. In a completely synchronous interface, the edges are divided into a sampling and a driving edge. On the drive edge, the data can be updated in the bus. On the sampling edge, the data in the SDI/DATA IN pin is read in (sampled). • • From a practical point, the data in the bus can be updated anytime except in the sampling edge. It is important to start by defining a convention name to avoid confusion regarding the direction of each pin as shown in Figure 1. For the most part, the slave cannot be configured and can only operate in one mode. However, sometimes it can operate in up to two different modes. Sometimes only three wires are needed. For example, in a DAC it may not be necessary to read back the data, or, in the case of an ADC, to send data. In those cases, the connection can be defined as a 3-wire interface. MASTER SLAVE SCLK DATA OUT DATA IN CS SCLK SDI SDO CS Figure 1. SPI Basic Interconnection t10 t1 t9 SCLK t8 t4 t3 t2 t7 CS t5 SDI t6 DB31 DB0 Figure 2. SPI Timing Diagram Example Rev. 0 | Page 1 of 8 11585-002 • The SPI interface defines four transmission modes. The master should be able to support all four modes, but this needs to be confirmed beforehand because sometimes the master is not compatible with a particular mode. This can be overcome by using inverters, as described in the SPI Mode Interconnection section. 11585-001 • Interface enable: CS, SYNC, ENABLE, and so on. Data in: SDI, MISO (for master), MOSI (for slave), and so on. Data out: SDO, MISO(for slave), MOSI (for master), and so on. Clock: SCLK, CLK, SCK, and so on... AN-1248 Application Note TABLE OF CONTENTS Introduction ...................................................................................... 1 When is the Bus Data Updated? ......................................................4 Master-Slave Compatibility ............................................................. 1 Are There Additional Considerations? ...........................................5 Revision History ............................................................................... 2 SPI Mode Interconnection ...............................................................6 Which Transmission Mode is Used by the Slave? ........................ 3 Topologies...........................................................................................6 REVISION HISTORY 7/13—Revision 0: Initial Version Rev. 0 | Page 2 of 8 Application Note AN-1248 WHICH TRANSMISSION MODE IS USED BY THE SLAVE? The timing diagram is a figure with multiple lines and names as shown in Figure 2. Identifying the transmission mode is relatively easy. There is a line that connects the CS falling edge with SCLK as shown in Figure 4. The mode depends on the SCLK level, sometimes called polarity (CPOL), when the transmission is initiated (CS is pulled low) and the sampling edge, called phase (CPHA), as shown in Figure 3. Note that the phase is relative to the polarity and is not an absolute value. The SPI modes are captured in Table 1. t1 t6 DB31 11585-005 t5 DB0 Figure 4. Polarity Mode SCLK In this particular case, SCLK can be high or low; there is no restriction. CS 11585-003 SCLK CPHA = 1 Figure 3. SPI Timing Table 1. SPI Modes Mode t7 CS SDI CPOL = 0 t2 t3 CPHA = 0 CPOL = 1 t9 SCLK The SDI diagram should have a bit that is enclosed by two timings, setup and hold. The two timings refer to the time that the data should be present in the bus before and after the sample edge, so both timings use the sampling edge for reference as shown in Figure 5. t10 Polarity (CPOL) t1 t9 Phase (CPHA) SCLK 0 t8 t3 t2 t7 CS t5t5 2 11585-004 SDI tt66 DB31 DB0 Figure 5. Phase Mode In this case, the sample edge is falling. Correlating the findings with Table 1, the slave part is compatible with Mode 1 and Mode 2. Rev. 0 | Page 3 of 8 11585-006 1 3 t4 AN-1248 Application Note WHEN IS THE BUS DATA UPDATED? If the pin is updated several nanoseconds after the sampling edge, the slave has almost the full SCLK period to guarantee a stable value of the signal in the bus so that the readback can be done without reducing the SCLK frequency. The SDO is used to transfer data from slave to master as well as transferring data out from master to slave. Although the data can be updated anytime, typically two strategies are employed. One strategy is to update the SDO/DATA OUT pin in the driving edge as shown in Figure 7. The main trade-off is for slow masters because the data only is stable in the pin several nanoseconds after the sampling edge and the master hold time can be violated. This problem occurs because the hold time is high, that is, >15 ns. If this is the case, the recommendation is to use a logic gate to delay the new data in the DATA IN pin as long as it needed as shown in Figure 6. There are technical reasons behind both strategies, but it is important to understand the tradeoffs. Masters use the first strategy because the SDO drivers are designed to support fast transitions. SAMPLING EDGE U1 DATA IN SCLK CS CS ORIGINAL SCLK DELAYED Figure 6. Enable Time Several gate technologies and typical propagation delays for a NOR gate are shown in Table 2. To guarantee a correct readback, the SCLK should be reduced to guarantee that the signal is stable before the sampling edge. Table 2. Gate Technologies and Propagation Delays Technology AHC HC HCT For this example, assume a maximum transition time of 36 ns. t9 SCLK SDO MICROCONTROLLER If the SDO signal is updated in the driving edge, the pin has only one-half (or even less) of a clock period to update the signal because a signal should be stable several nanoseconds before the sampling edge. SDO Data Valid from SCLK Rising Edge SDI DATA OUT Slaves implement an internal SDO driver weaker than the master, thus the strategy implemented is dependent on the data transfer rate. 36 ns Propagation Delay 4.4 ns 9 ns 11 ns This mean that the maximum cycle time is 36 ns + master setup time (assume 10 ns) = 46 ns, so the maximum SCLK frequency for reading back is 10 MHz. t4 t1 t2 t7 SCLK t3 t8 tt99 C3 C2 C1 C0 D7 D6 D5 t10 D2 D1 D2 D0 11585-007 SYNC SDO Figure 7. SDO Driving Edge Update CS t8 1 2 3 4 5 18 t3 DOUT A THREE-STATE 19 20 20 t6 2121 t7 tt4 4 DB13A DB12A DB11A B13A DB12A DB11A Figure 8. Delayed SDO Update Rev. 0 | Page 4 of 8 31 32 33 t9 t5 t5 DB1A DB0A tQUIET THREESTATE 11585-008 t2 SCLK UPDATE SDO 11585-009 The other strategy is to update the SDO/DATA OUT pin several nanoseconds after the sampling edge as shown in Figure 8. Application Note AN-1248 ARE THERE ADDITIONAL CONSIDERATIONS? CS as Start Conversion Signal Enable Time Some ADCs, in order to reduce the pin count, and fit in small packages, or just to reduce the routing complexity, offer multiple functionality in a single pin. Enable time defines how fast the SPI interface is enabled and ready to receive or transmit data. This is typically referred to as the SCLK sampling edge as shown in Figure 9. When the CS is used to generate the internal start conversion signal, there are two different case scenarios. Disable Time Disable time defines how fast the SPI is disabled to ignore any new generated sampling edge transitions as shown in Figure 9. t10 First Scenario The SCLK signal is used as an internal clock, and continuous SCLK is needed. In this case, the SCLK is limited between a maximum and minimum value as shown in Table 3. tt 9 t1 9 SCLK tt44 t2 t3 t7 Table 3. Example of SCLK Frequency Limitation Parameter fSCLK CS SDI t6 DB31 11585-010 t5 DB0 Figure 9. Enable and Disable Time Min 0.01 Max 20 Unit MHz t1 CS tCONVERT t2t2 11 SCLK t6 2 3 4 SDATA Z ZERO B 5 13 t4 t3 THREESTATE Description SCLK frequency There is timing, restriction, similar to the enable time described below, in which the master cannot generate a sampling edge, or the conversion will be corrupted, as shown in Figure 10. ZERO ZERO DB11 14 DB10 15 16 t5 t7 t8 tQUIET DB2 DB1 DB0 THREE-STATE 4 LEADING ZEROS Figure 10.Continuous SCLK During Conversion Rev. 0 | Page 5 of 8 11585-016 t8 AN-1248 Application Note Second Scenario TOPOLOGIES The part includes an internal conversion clock. In this case, the recommendation is to not generate SCLK pulses to reduce the digital feedthrough impact in the LSB bits conversion as shown in Figure 11. The SPI interface permits different topologies allowing the master to control one or several slaves. CNV tCONV tCONV In this configuration, there is only one slave and one master, as shown in Figure 12. MASTER tACQ CONVERSION ACQUISITION CONVERSION 3 tHSDO SDO tQUIET 17 18 D16 tDIS D1 D0 Figure 11. Quiet SCLK During Conversion If the SPI interface is implemented by the hardware, rather than an FPGA, it is not possible to have accurate control of the SCLK and CS pin. If this is the case, the recommendation is to use a GPIO as CS, to accurately control the relation between CS and SCLK. Figure 12. Standalone Configuration Daisy-Chain Topology In this configuration, there is one master and multiple slaves connected in series as shown in Figure 13. MOSI MISO SCLK CS SDO SDI CS SCLK SDO U2 U1 CS SCLK Figure 13. Daisy-Chain Configuration In some ADCs, the SDO provides double functionality. This is typically noted as SDO/RDY. The SDO pin is disabled with CS and remains at high impedance until the conversion is completed at which point the pin is pulled low, indicating the end of the conversion. SPI MODE INTERCONNECTION Sometimes because the controller cannot be configured in a particular SPI mode used by the slave or because there is a need to operate all the devices with the same SPI mode, that is, daisychain mode, the mode needs to be modified externally. Consider these two cases: • SDI MICROCONTROLLER SDO as Conversion Ready Pin • CS 19 tSCKH tCSDO D17 SDO CS 11585-013 2 SDI DATA IN 11585-017 1 SCLK DATA OUT tSCK tSCKL SCK SLAVE SCLK (QUIET TIME) ACQUISITION 11585-012 tCNVH Standalone Topology The mode is complementary where MODE 1 = MODE 2 or MODE 0 = MODE 3 Using a inverter gate in the SCLK line the problem is fixed The modes are not complementary. The solution becomes a bit more elaborate, and involves the use of inverters and flip-flops, thus the recommendation is to avoid this because timing issues may arise. The main benefit of this configuration is the reduced number of connections required. Operating in this mode, the clock period may need to be increased because the propagation delay of the line between subsequent devices. In addition, the number of clocks should be increased because the required clocks are the sum of U1 and U2. Typical transmission in a daisy-chain configuration is shown in Figure 14. The first data-word is assigned to the last slave connected and the last data-word is assigned to the closest slave. There are parts that can be configured in daisy-chain mode but, by default, the part power-up in stand-alone mode, that is, the SDO pin does not clock out data. In this case, the recommendation is to place the part in the first place in the chain and enable daisy-chain mode by writing directly to the part. Because the SDO is in high impedance before enabling the mode, it is recommended to connect a pull-up (or pull-low) resistor in the SDO pin to control the data that is transferred to the second device in the chain. Similar problems occur when the SDO pin is used for multiple functionality, SDO/RDY. The recommendation is to place a pull-up resistor to avoid electrical issues and continue using the RDY functionality. Rev. 0 | Page 6 of 8 Application Note AN-1248 SCLK 1 2 16 17 18 32 CS DB15 DB0 DB15 DB0 MOSI DB15 INPUT WORD FOR U1 DB0 DB15 DB0 SDO_U1 UNDEFINED INPUT WORD FOR U2 11585-014 INPUT WORD FOR U2 Figure 14. Daisy-Chain Timing Diagram Parallel Configuration In this configuration, there is one master with multiple slaves connected in parallel as shown Figure 15. SLAVE MASTER DATA OUT SDI As a precaution, in this configuration, the SDO may be not disabled synchronously with SYNC in some parts, for example, if the part is configured in daisy-chain mode. SDO SCK SCLK CS1 CS CS2 In this case, to avoid electrical issues, the recommendation is to not connect the SDO pin to the bus. Alternatively, if it is possible to disable the SDO pin, place a serial resistance with the SDO pin to minimize electrical problems in the first transmission and disable the SDO pin at the beginning. SLAVE DATA IN CS3 SDO SDI SCLK CS SLAVE SDI In this configuration, SCLK and SDI are shared within all the parts. Due to the parasitic net (or track) capacitance, it is recommended to increase the clock period slightly. SDO CS 11585-015 SCLK Figure 15. Parallel Configuration Rev. 0 | Page 7 of 8 AN-1248 Application Note NOTES ©2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. AN11585-0-7/13(0) Rev. 0 | Page 8 of 8