Reference Design PRD1139 Isolated Flyback Converter; Input +30- 60V; Output 5V 100mA

advertisement

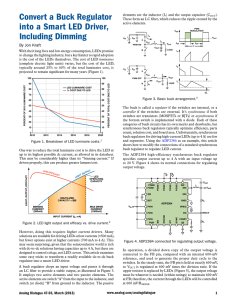

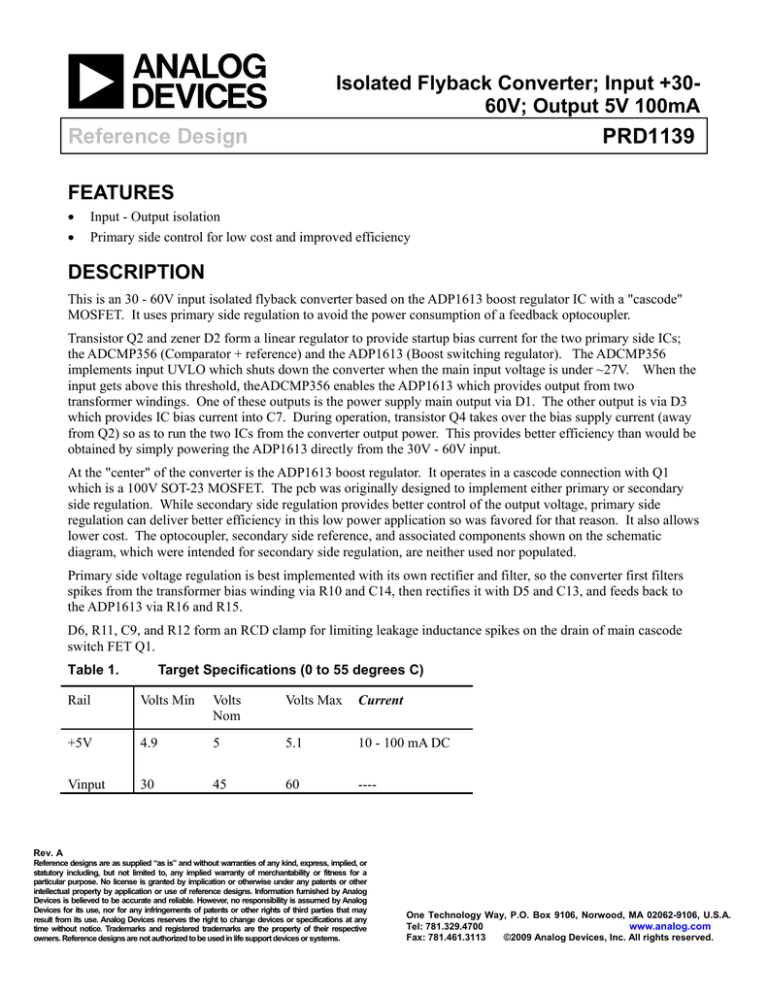

Isolated Flyback Converter; Input +3060V; Output 5V 100mA Reference Design PRD1139 FEATURES • • Input - Output isolation Primary side control for low cost and improved efficiency DESCRIPTION This is an 30 - 60V input isolated flyback converter based on the ADP1613 boost regulator IC with a "cascode" MOSFET. It uses primary side regulation to avoid the power consumption of a feedback optocoupler. Transistor Q2 and zener D2 form a linear regulator to provide startup bias current for the two primary side ICs; the ADCMP356 (Comparator + reference) and the ADP1613 (Boost switching regulator). The ADCMP356 implements input UVLO which shuts down the converter when the main input voltage is under ~27V. When the input gets above this threshold, theADCMP356 enables the ADP1613 which provides output from two transformer windings. One of these outputs is the power supply main output via D1. The other output is via D3 which provides IC bias current into C7. During operation, transistor Q4 takes over the bias supply current (away from Q2) so as to run the two ICs from the converter output power. This provides better efficiency than would be obtained by simply powering the ADP1613 directly from the 30V - 60V input. At the "center" of the converter is the ADP1613 boost regulator. It operates in a cascode connection with Q1 which is a 100V SOT-23 MOSFET. The pcb was originally designed to implement either primary or secondary side regulation. While secondary side regulation provides better control of the output voltage, primary side regulation can deliver better efficiency in this low power application so was favored for that reason. It also allows lower cost. The optocoupler, secondary side reference, and associated components shown on the schematic diagram, which were intended for secondary side regulation, are neither used nor populated. Primary side voltage regulation is best implemented with its own rectifier and filter, so the converter first filters spikes from the transformer bias winding via R10 and C14, then rectifies it with D5 and C13, and feeds back to the ADP1613 via R16 and R15. D6, R11, C9, and R12 form an RCD clamp for limiting leakage inductance spikes on the drain of main cascode switch FET Q1. Table 1. Target Specifications (0 to 55 degrees C) Rail Volts Min Volts Nom Volts Max Current +5V 4.9 5 5.1 10 - 100 mA DC Vinput 30 45 60 ---- Rev. A Reference designs are as supplied “as is” and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of reference designs. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Reference designs are not authorized to be used in life support devices or systems. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved. Reference Design PRD1139 TABLE OF CONTENTS Features ......................................................................................................................................................................1 Description .................................................................................................................................................................1 Revision History.........................................................................................................................................................2 TABLE OF FIGURES Figure 1. Schematic Diagram of Flyback Converter.............................................................................................3 Figure 2. Efficiency Test Data...............................................................................................................................6 Figure 3. Voltage Regulation Test Data.................................................................................................................7 Figure 4. Output ripple with 60 VDC Input and 100 mA Load ............................................................................7 Figure 5. Output ripple with 60 VDC Input and 10 mA Load ..............................................................................8 Figure 6. Output ripple with 30 VDC Input and 100 mA Load ............................................................................8 Figure 7. Output ripple with 30 VDC Input and 10 mA Load ..............................................................................9 REVISION HISTORY 11/20/2009—Revision A: Tested Prototype Rev. A | Page 2 of 10 3 4 5 D8 P0D801 P0R1802 1 P0U101 P0U105 4 2 P0R1902 U2 C1 4 P0U204 5 P0U205 P0R302 A P0R2101 pgnd R3 P0Q401 R19 P0R2001 R20 3 A P0R2002 P0U102 P0U104 P0R301 6 P0R1901 P0R1801 U1 5 P0R101 R18 R1 P0U203 P0D802 P0C102 P0C101 2 P0R102 1 R21 P0R2102 P0Q402 R22 P0R2201 P0Q403 P0R2202 J1 Q4 1 P0C1502 P0C1501 P0J101 U3 D1 6 P0R1102P0D602 P0D601 2P0T102 5 P0D301 pgnd pgnd Sgnd P0D401 D5 R10 P0R1001 P0R1002 P0D501 C7 P0D502 C14 pgnd C12 R16 C P0R701 Q3 P0R502 P0R401 P0J401 pgnd C2 R8 pgnd COMP SS 2 P0U502 FB RT 3 P0U503 SD IN 4 C3 P0U501 P0U504 GND SW 8 C8 P0U508 7 P0U507 R15 P0R1501 1 P0Q303 P0Q302 P0R1502 U5 P0C802 P0C801 3 P0U403 6 C18 P0U506 P0C1801 P0C1802 5 P0U505 pgnd Sgnd pgnd P0C1902 P0C1901 Gnd Vout P0C202 P0C201 R4 P0U402 P0R802 2 P0C302 P0C301P0R801 P0R402 P0U404 1 P0U401 4 Vin Vcc P0R501 P0Q301 P0R201 R5 U4 P0R1701 R7 P0R1601 P0R901 R17 P0R702 1 C13 P0R1702 P0R202 R9 R2 J4 pgnd P0R1602 P0R902 P0C701 P0C702 C B D4 P0C1402 P0C1401 Q2 1P0J301 C17 P0D402 D3 C4 J3 P0T105 P0D302 P0C402 P0C401 P0Q203 C16 Sgnd Q1 P0Q101 4 P0U304 P0D102 P0C1302 P0C1301 P0R1101 Gnd C15 pgnd P0C1702 P0C1701 P0R1201 P0R1301 P0R1402 P0Q102 P0Q201 P0D202 P0Q202 P0T106 P0D101 D6 R11 C5 P0D201 P0C502 P0C501 P0D902 D2 P0R1401 7 C9 P0Q103 R12 D9 R14 3 P0T103 P0C902 P0C901 R13 1P0T101 5 P0U305 NR D7 C11 P0C1202 P0C1201 P0R1202 P0D901 pgnd P0R1302 B P0T107 6 P0U306 SD P0C1602 P0C1601 C20 C10 OUT 2 P0U302 IN 3 P0U303 Err P0D702 + P0C1002 + 8 P0T108 P0U301 P0D701 P0C2001 P0C602 P0C601 C6 4 T1 P0T104 P0C2002 1 P0J201 P0C1102 P0C1101 J2 P0C1001 1 pgnd C19 D D pgnd Analog Devices Inc. Central Power Apps Fort Colins, Colorado USA Size: B 1 2 3 4 Number: PRD1139 5 Revision: 11/6/09 6 Reference Design PRD1139 Table 2. Bill Of Materials Sequence Ref Designation Description 1 C1 Open 2 C2 1 uF 16V X5R 3 C3 2.2 nF X7R 4 C4 100 nF 25V X7R 5 C5 1 uF 0805 25V X5R 6 C6 100V 1 uF 1210 X7R 7 C7 1 uF 16V X5R 8 C8 100 nF 100V X7R 9 C9 10 nF 50V X7R 10 C10 330 uF 16V low ESR Aluminum Electrolytic 11 C11 4.7 uF 10V 0805 X5R 12 C12 100 nF X7R 13 C13 2.2 uF 16V X5R 14 C14 100 pF NP0 15 C15 1 uF 16V X5R 16 C16 10 nF X7R 17 C17 Open 18 C18 100 nF 100V X7R 19 C19 1 uF 16V X5R 20 D1 MBR0540 21 D2 MMSZ5231B 22 D3 NSR0240 23 D4 NSR0240 24 D5 NSR0240 25 D6 BAV20 26 D7 BTZ52C6V8 Rev. A | Page 4 of 10 Reference Design PRD1139 Sequence Ref Designation Description 27 D8 Open 28 D9 NSR0240 29 Q1 Si2328DS 30 Q2 MMBTA06 31 Q3 Open 32 Q4 MMBT3904 33 R1 Open 34 R2 1.0M 35 R3 2.00K 36 R4 22.1K 37 R5 10K 38 R6 71.5K 39 R7 2.00 M 40 R8 20K 41 R9 Open 42 R10 100 43 R11 33 44 R12 100K 1206 45 R13 210K 1206 46 R14 40.2K 47 R15 15K 48 R16 46.4K 49 R17 Open 50 R18 Open 51 R19 Open 52 R20 Open 53 R21 Open Rev. A | Page 5 of 10 Reference Design PRD1139 Sequence Ref Designation Description 54 R22 Open 55 U1 Open 56 U2 Open 57 U3 Open 58 U4 ADCMP356 59 U5 ADP1613 Note: For a first test and demo, the plan is to use a transformer Coilcraft type B0226-EL. This type should work reasonably well however it is not completely optimized for this application, and may not provide the needed isolation voltage. Based upon results with this transformer another one can be specified which will be more accurately tailored to the needs of this converter design. It is anticipated that the dimensions will remain similar. Figure 2. Efficiency Test Data Efficiency ADP1613 Flyback PRD1139 80.0% 70.0% 30V Input Efficiency 60.0% 45V Input 50.0% 60V Input 40.0% 30.0% 20.0% 0.00 0.02 0.04 0.06 0.08 Amps Output Rev. A | Page 6 of 10 0.10 0.12 Reference Design PRD1139 Figure 3. Voltage Regulation Test Data Output Regulation ADP1613 Flyback PRD1139 6.0 Volts Output 5.8 5.6 30V Input 5.4 45V Input 60V Input 5.2 5.0 4.8 0.00 0.02 0.04 0.06 0.08 0.10 0.12 Amps Output Figure 4. Output ripple with 60 VDC Input and 100 mA Load Load Rev. A | Page 7 of 10 Reference Design PRD1139 Figure 5. Output ripple with 60 VDC Input and 10 mA Load Figure 6. Output ripple with 30 VDC Input and 100 mA Load Rev. A | Page 8 of 10 Reference Design Figure 7. PRD1139 Output ripple with 30 VDC Input and 10 mA Load Rev. A | Page 9 of 10 Reference Design PRD1139 NOTES ©2009 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Error! Unknow Rev. A | Page 10 of 10