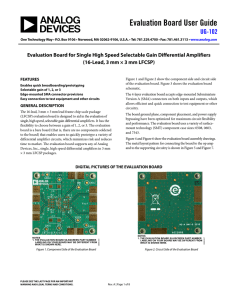

AD9643/AD6649 ENG (SOCKET) DUT PDWN OEN

advertisement

8 6 7 2 3 4 5 1 REVISIONS REV DESCRIPTION DATE APPROVED AD9643/AD6649 ENG (SOCKET) D D DUT THE FOOTPRINT FOR THIS SOCKED NEEDS TO BE CHECKED AGAINST THE DRAWING TP101 EXTRA CIRCUITRY FOR AD9258 COMPATIBILITY NOT NEEDED FOR AD9643/AD6649 DNC_SENSE 10K R106 AGND AGND DNI 0 AGND DNI C KP_ICELL DNI DNC_VREF C125 1UF R109 0 AVDD R111 B2 DNI 0 C126 R112 A2 AGND 0.1UF KP_VDDIO R110 0 DNI DNI CLK+ CLKSYNC 0 DNI DRVDD DNI D0D0+ DRVDD 1 2 3 4 FDA 5 FDB 6 DNC DNC6 7 DNC DNC7 8 9 10 11 12 13 14 15 16 SKT64QFN_PAD_A 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 D1D1+ D2D2+ D3D3+ PAD 64 AVDD 63 62 VIN+B 61 VIN-B 60 AVDD 59 DNC 58 DNC_RBIAS 57 VCM 56 DNC_SENSE DNC DNC 55 DNC_VREF 54 AVDD 53 52 VIN-A 51 VIN+A 50 AVDD 49 KP_ICELL R107 DNC_RBIAS VCM 1 C105 0.1UF AVDD AGND 1 2 PDWN U1010 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 P101 R104 10K PDWN OEN DUT_CSB DUT_SCLK DUT_SDIO OR+ ORD13+ D13D12+ D12- PDWN C DNI AGND AVDD P102 1 2 OEN DRVDD D11+ D11D10+ D10- R108 10K OEN DNI AGND SG-MLF64A-7008 SYNC J101 R101 1 0 2 3 4 5 AGND R105 49.9 C123 D8D8+ D9D9+ DRVDD DRVDD KP_VDDIO D4D4+ 2.0K R102 B D5D5+ D6D6+ DCODCO+ D7D7+ LAYOUT: DECOUPLING QUANTITY MAY VARY LAYOUT DEPENDING AVDD C107 1UF DNI C101 0.1UF C102 0.1UF C103 0.1UF C121 1UF C122 1UF B SYNC 0.1UF R103 2.0K AGND DNI SMA-J-P-X-ST-EM1 AGND AVDD AGND C109 0.1UF C110 0.1UF C111 0.1UF C112 0.1UF C113 0.1UF C114 0.1UF C115 0.1UF C117 1UF C118 1UF AGND A A AN A LOG DEV CES THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, SCHEMATIC 9643 & 6649 ENGINEERING EVAL. PCB AD9643 Engineering Board DESIGN VIEW <DESIGN_VIEW> DRAWING NO. REV 9643EE01 B OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. SIZE PTD ENGINEER THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 7 6 5 4 3 <PTD_ENGINEER> 2 D SCALE NONE SHEET 1 1 OF 6 8 6 7 2 3 4 5 1 2 3 4 6 5 REV AGND PGND DESCRIPTION DATE APPROVED POWER VIN SK33A-TP CR201 A C N 10UF C201 D AGND P103 E212 1 2 1 2 U201 ADP1708ARDZ-R7 P202 P 10UF AGND E214 1 2 10UF P N C236 0.1UF 100MHZ P110 100MHZ 1 2 100MHZ 5V_SUPPORT P106 AGND N Z5.531.3425.0 P203 AGND 1 2 3 4 P 3P3V_ANALOG 100MHZ N 100MHZ 0.1UF C240 E208 1 2 E216 1 2 C239 1 2 AGND 10UF 100MHZ 10UF 2 E215 1 2 P 4 1P8V_CLOCK 0.1UF C238 GND C E217 1 2 4.7UF 0.01UF DNI 4.7UF C242 100MHZ EN NC AGND C243 DNI 3P3V_DIGITAL C241 2 U207 ADP150AUJZ-1.8-R7 1 VIN 5 VOUT 3 1 2 4.7UF E204 1 2 C209 0.01UF DNI 4.7UF C208 C207 4 GND N 1 2 P105 U203 ADP150AUJZ-3.3-R7 1 VIN 5 VOUT 3 EN NC AGND 100MHZ AGND C AGND 3P3V_ANALOG E203 1 2 2 100MHZ AVDD 4.7UF 4 GND DRVDD Z5.531.3625.0 E202 1 2 C206 EN NC 0.01UF C204 4.7UF C205 DNI S2A-TP E213 1 2 0.1UF C234 AGND U202 ADP150AUJZ-3.3-R7 1 VIN 5 VOUT 3 AGND 1 2 3 4 5 6 C233 2 PAD 100MHZ P104 CR204 A C 10UF N 5V_SUPPORT C231 100MHZ 0.1UF C232 P 3P3V_DIGITAL E201 1 2 5 6 4.7UF C202 4.7UF 10K 1.91K R202 R203 EN SENSE IN OUT IN2 OUT2 ADJ GND1 PAD C203 1 7 3 4 8 VIN C235 D C237 PJ-202A 1 CR202 A C CR203 F201 1 2 1.1A P 1 2 3 FL201 BNX016-01 R201 P201 261 LNJ314G8TRA (GREEN) REVISIONS U204 ADP1706ARDZ-1.8-R7 EN2 VOUTB 0.01UF C218 AGND R214 10.5K 2200PF C214 100PF R216 0 DNI AGND PGOOD1 COMP1 SW1 SW2 L201 2.2UH PGOOD2 COMP2 SW3 SW4 R213 13K R215 TBD0603 C215 DNI E210 1 2 1 2 DNI 100MHZ 100MHZ C220 22UF DNI AGND AGND R218 0 DNI L202 TO EVALUATE SHARING OF AVDD AND DVDD P108 1 2 EN SENSE IN OUT IN2 OUT2 SS GND1 PAD 2 PAD E207 1 2 5 6 DRVDD 100MHZ P109 AGND E209 1 2 AGND 100PF 1 7 3 4 8 C221 22UF C219 TBD0603 B 100MHZ E206 1 2 4.7UF C227 0.01UF 4.7UF C226 R217 0 DNI 1500PF C216 PAD ADP2114_PRELIM JP203 1 2 0 VOUTA AGND VOUTB E211 1 2 100MHZ R219 0 A AGND R221 EN2 2.2UH 0 R220 TBD0603 1.00K DNI R222 VIN 2 PAD AVDD 1 2 SCFG FREQ SYNC_CLKOUT OPCFG EN1 V1SET FB1 SS1 EN2 V2SET FB2 SS2 GND PGND1 PGND2 PGND3 PGND4 C217 0.01UF VOUTA A E205 1 2 5 6 4.7UF EN1 R212 15K EN SENSE IN OUT IN2 OUT2 SS GND1 PAD U205 ADP1706ARDZ-1.8-R7 C213 C228 SW_FREQ VIN1 VIN2 VIN3 VIN4 VIN5 VIN6 AGND R210 4.64K AGND C230 1.00K R205 VDD AGND R208 100K AGND U206 R211 15K C225 10 R207 100K 0 R209 27K 1 7 3 4 8 0.01UF EN1 DNI S2A-TP 4.7UF C229 R204 S2A-TP JP201 1 2 0 OPTIONAL SWITCHING SUPPLY 1UF VIN CR206 A C AGND AGND C212 B C211 22UF R206 C210 22UF CR205 A C AGND P107 DNI 100MHZ C223 22UF C224 22UF AN A LOG DEV CES DNI C222 TBD0603 AGND THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR AGND DNI IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, AGND SCHEMATIC 9643 & 6649 ENGINEERING EVAL. PCB AD9643 Engineering Board DESIGN VIEW <DESIGN_VIEW> OF ANALOG DEVICES. OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 7 6 REV 9643EE01 B OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS SIZE PTD ENGINEER THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS 8 DRAWING NO. 5 4 3 <PTD_ENGINEER> 2 D SCALE NONE SHEET 2 1 OF 6 8 6 7 2 3 4 5 1 REVISIONS REV DESCRIPTION DATE APPROVED ANALOG INPUT PASSIVE PATH A C303 D 8.2PF THIS SECTION WILL CHANGE BASED ON 9644 EXPERIMENTS AMP_OUT_A+ D AGND DNI R311 0 C305 0.1UF 3 DNI 6 PRI 3 T303 SEC AGND 5 1 33 0 VCMA 0.1UF R314 AGND 36 R316 AGND C306 0.1UF SHARE PADS AGND C R319 VIN-A R320 VIN+A 0 33 R312 0 R318 49.9 C304 DNI AMP_OUT_A- LAYOUT: SMA'S SHOULD BE 540 MILS CENTER TO CENTER C 8.2PF 4 ETC1-1-13 2 1 AGND R315 R313 36 C301 4 DNI C313 3 AGND 0.1UF T302 ETC1-1-13 PRI DNI SEC T301 ADT1-1WT+ 1 4 5 R301 49.9 2 3 4 5 R317 49.9 8.2PF AIN_A SHARE PADS C302 J301 1 AGND R302 VCMA 33 VCM R303 VCMB NOTE: CUTS REQ'D FOR 2ND TRANSF USE B C309 PASSIVE PATH B 8.2PF 33 AMP_OUT_B+ AGND B DNI AIN_B C311 2 DNI 0.1UF 3 6 PRI AGND 5 1 T307 R335 R339 33 0 R333 36 C307 4 SEC ETC1-1-13 C314 AGND ETC1-1-13 T306 3 4 3 1 0.1UF PRI DNI AGND T305 4 SEC DNI 5 R321 49.9 1 2 3 4 5 ADT1-1WT+ R337 49.9 VCMB 0.1UF R334 AGND 36 R336 AGND C312 DNI 0.1UF SHARE PADS R340 33 VIN-B 0 R332 0 R338 49.9 C310 AGND VIN+B 8.2PF 1 R331 0 8.2PF SHARE PADS C308 J303 AMP_OUT_B- A LAYOUT: SMA'S SHOULD BE 540 MILS CENTER TO CENTER A AGND AN A LOG DEV CES THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, SCHEMATIC 9643 & 6649 ENGINEERING EVAL. PCB AD9643 Engineering Board DESIGN VIEW <DESIGN_VIEW> DRAWING NO. REV 9643EE01 B OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. SIZE PTD ENGINEER THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 7 6 5 4 3 <PTD_ENGINEER> 2 D SCALE NONE SHEET 3 1 OF 6 8 6 7 2 3 4 5 1 REVISIONS REV DESCRIPTION DATE APPROVED ACTIVE PATH - CHANNEL A AND B 3P3V_ANALOG D C413 0.1UF C414 0.1UF D C419 0.1UF AGND 3P3V_ANALOG R432 1K 5V_SUPPORT 5V_SUPPORT P400 C415 R410 3P3V_ANALOG 0 1200PF DNI DNI AGND R427 1K AGND 3 0.1UF TC3-1T+ 4 DNI AGND 0 J403 TC3-1T+ AMP_IN_A+ 1 0 DNI 3 2 3 4 5 DNI 2 AGND R438 49.9 0.1UF DNI 6 AGND B 0.1UF C404 T402 AGND R402 37 14 6 5 4 LATCHA LATCHB PM MODE0 MODE1 C405 R406 4 VINB_POS 0.1UF DNI DNI R405 130 C403 R404 AGND 15 VINB_NEG 16 R408 130 DNI R430 1K R431 1K R433 1K R434 1K 0 1UH L401 0 0 C418 22PF C417 2.7PF DNI DNI DNI L406 L404 120NH 1200PF DNI 5V_SUPPORT A0 A1 A2 A3 A4 A5 B0 B1 B2 B3 B4 B5 5V_SUPPORT THESE RLCS ARE PLACE HOLDERS... PLACE CORRECT VALUES & COMPONENTS... DNI C421 R414 1K 0 1200PF DNI 0.1UF L409 L411 120NH 120NH DNI DNI 0 R441 0 R442 R416 10K R417 10K R418 10K R419 10K R420 10K A0 R413 10K R421 10K R422 10K R423 10K R424 10K R425 10K DNI AGND ADL5202_CSB FPGA_SCLK DNI L410 C422 R415 DNI DNI L412 AMP_OUT_A+ 0 120NH 1200PF DNI DNI DNI 120NH DNI FPGA_SDIO 0 R409 10K B0 A1 B1 A2 B2 A3 A 3P3V_ANALOG C442 0.1UF B C424 22PF C423 2.7PF 150 0 R440 ADL5202_CSA R444 R439 AMP_OUT_A- DNI AGND 3P3V_ANALOG A B3 A4 B4 A5 B5 AN A LOG DEV CES THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, SCHEMATIC 9643 & 6649 ENGINEERING EVAL. PCB AD9643 Engineering Board DESIGN VIEW <DESIGN_VIEW> DRAWING NO. REV 9643EE01 B OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. SIZE PTD ENGINEER THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 C 120NH DNI DNI DNI DNI DNI DNI AMP_OUT_B+ DNI AGND R407 AMP_OUT_B- DNI C416 R411 R428 AGND 120NH ADL5202_PRELIM 3P3V_ANALOG 1 C406 DNI AGND R426 DNI 120NH 1UH T401 L405 1UH C401 2 AMP_IN_B+ R437 49.9 2 3 4 5 VINA_POS 30 29 32 31 19 20 21 22 38 39 40 1 2 3 13 12 11 10 9 8 L407 1 1 PWUPB GND_ZAP GND GND PAD 6 VOUTA_NEG VOUTA_POS NC4 NC3 NC1 NC2 VOUTB_NEG VOUTB_POS A0_UPDN_CLK_A DATA A2_FA_A CSA_N_A3 A4 A5 UPDN_CLK_B_B0 DATA GS0_FA_B_B2 GS1_CSB_N_B3 SCLK_B4 SDIO_B5 17 7 18 33 PAD J404 0.1UF DNI AGND 36 VINA_NEG 35 U401 L408 34 23 24 25 26 27 28 0 0 DNI C402 R403 R401 PWUPA VPOS VPOS_IDB VPOS_IGB VPOS_IGA VPOS_IDA VPOS DNI C C441 0.1UF 5V_SUPPORT R446 1K L403 5V_SUPPORT 3P3V_ANALOG R445 1K 150 R429 1K 150 AGND THESE RLCS ARE PLACE HOLDERS... PLACE CORRECT VALUES & COMPONENTS... R412 1 2 3 SAMTECTSW10608GS3PIN C411 0.1UF R443 C409 0.1UF 150 C408 0.1UF 1UH C407 0.1UF C412 10UF L402 C410 10UF 7 6 5 4 3 <PTD_ENGINEER> 2 D SCALE NONE SHEET 4 1 OF 6 8 6 7 2 3 4 5 1 REVISIONS REV ACTIVE CLOCK PATH R510 L507 0.1UF 100 R512 OUT2 DNI 3.9NH C521 OUT2_N CLK_OUT- 0.1UF EEPROM_SEL 3.3V_OUT_4-13 0.1UF C516 C515 0.1UF 3.3V_REF CLK- 0 0.1UF DNI 0 R534 0 DNI AGND C533 R523 R538 DNI 49.9 STATUS0_SP0 STATUS1_SP1 0.1UF 0.1UF C548 C547 0.1UF 0.1UF C539 0.1UF C538 0.1UF C537 1UH L505 3.3V_OUT_0-3 3.3V_OUT_4-13 AGND AGND SCHEMATIC AN A LOG DEV CES 9643 & 6649 ENGINEERING EVAL. PCB AD9643 Engineering Board CLK_IN+ IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, DESIGN VIEW <DESIGN_VIEW> DRAWING NO. REV 9643EE01 B OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. SIZE PTD ENGINEER THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 6 5 10UF A AGND IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR 7 10UF C530 10UF C527 C534 10UF C524 1UH J502 1 THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. 8 0.1UF 0.1UF C546 0.1UF C545 0.1UF C544 0.1UF C543 0.1UF C536 C535 3.3V_PLL1 5 4 3 2 49.9 DNI AGND E502 1 2 DNI CLK_OUTAGND 3.3V_PLL2 AGND 2 3 4 5 49.9 DNI R521 0 R537 49.9 DNI R529 R530 AGND 3.3V_REF 3 AGND DNI R520 T503 0.1UF 2 3 4 5 J503 1 R540 24.9 ETC1-1-13 C523 J506 1 R543 100 2 L504 0 AGND 0.1UF 1UH L503 E501 1 2 B 1.8V_OUT_0-13 1UH 3P3V_DIGITAL T501 3 1 3P3V_ANALOG C517 0.1UF 1 4 CR503 DNI 1UH L502 5 SEC SEC PRI PRI DNI DNI DNI 4 0.1UF 1 1 1UH L501 45OHMS 3 CLK 2 R539 24.9 C528 C529 AGND AGND 5 ETC1-1-13 AGND 0.1UF DNI L506 45OHMS CLK+ 0 T502 ADT1-1WT+ 3 6 C518 0.1UF C532 R522 0.1UF 2 3 4 5 100 4 C522 J505 1 AGND AD9523 0 0 R541 DNI DNI CLK_OUT+ R542 DNI DNI C AGND AGND 1P8V_CLOCK R511 CLK_IN- R533 DNI KP_ICELL A USB_CSB2 CYP_SCLK CYP_SDI CYP_SDO PASSIVE CLOCK LAYOUT: SMA'S SHOULD BE 540 MILS CENTER TO CENTER LAYOUT: SHARE PADS WITH ACTIVE CLOCK PATH R'S OUT9 OUT9_N 54 1.8V_OUT_0-13 R546 53 52 100 51 3.3V_OUT_4-13 R526 50 49 100 48 3.3V_OUT_4-13 R527 47 46 100 45 R531 44 43 100 42 R532 41 40 100 39 1.8V_OUT_0-13 R535 38 37 100 RESETB 10K B AGND TP503 C526 1 LNJ314G8TRA (GREEN) 10UF R515 CR502 200 GND NC7WZ16P6X 2 10UF C525 3.3V_OUT_4-13 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 TP505 R514 0.1UF C542 RESET_N CS_N SCLK_SCL 3.3V_REF 4 C540 3.3V_OUT_4-13 VDD_1_8_OUT4_5 1.8V_OUT_0-13 AGND 1 SYNCB 10K Y2 LNJ314G8TRA (GREEN) 100 3.3V_REF 3 A2 200 3.3V_OUT_0-3 OUT8 OUT8_N VDD3_OUT8_9 10K 0.47UF 0 PDB R519 DNI TP504 R509 10K 0 R508 3.3V_PLL2 0.47UF R516 0.001UF C510 0.001UF C509 R506 C512 6 AGND OUT7 OUT7_N VDD_1_8_OUT8_9 R536 C511 TBD0402 100 R507 Y1 CR501 R513 VCC 1 A1 1 DNI U300 5 U501 OUT6 OUT6_N VDD3_OUT6_7 R544 AGND 100 0.33UF STATUS0/SP0 STATUS1/SP1 OUT5 OUT5_N VDD_1_8_OUT6_7 R545 C508 0.1UF 1 OUT4 OUT4_N VDD3_OUT4_5 OUT13 3.3V_OUT_4-13 0.1UF C LDO_PLL1 VDD3_PLL1 REFA REFA_N REFB REFB_N LF1_EXT_CAP OSC_CTRL OSC_IN OSC_IN_N LF2_EXT_CAP LDO_PLL2 VDD3_PLL2 LDO_VCO PD_N REF_SEL SYNC_N VDD3_REF OUT13_N 3.3V_PLL1 C507 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 SDIO_SDA 0.1UF 0.47UF AGND 49.9 10K 3.3V_OUT_0-3 TP502 SDO REF_TEST OUT13_N OUT13 VDD3_OUT12_13 OUT12_N OUT12 VDD_1_8_OUT12_13 OUT11_N OUT11 VDD3_OUT10_11 OUT10_N OUT10 VDD_1_8_OUT10_11 C513 R505 C506 3 PAD PLL1_OUT DNI ZD_IN_N ZD_IN VDD_1_8_OUT0_1 OUT0 OUT0_N VDD3_OUT0_1 OUT1 OUT1_N VDD_1_8_OUT2_3 OUT2 OUT2_N VDD3_OUT2_3 OUT3 OUT3_N EEPROM_SEL 60-800MHZ 4 5 49.9 VC OUT+ OUTGND 0.1UF 49.9 VCC R503 Y501 1 AGND C504 R604 6 C514 PAD 0.1UF 72 71 70 69 1.8V_OUT_0-13 68 OUT0 67 OUT0_N 66 65 R524 64 100 63 62 61 60 59 R525 58 100 57 56 55 R502 1K 0.33UF C503 AGND C505 0.1UF 1 SI04 VCXO_CTRL 10K D 3.3V_OUT_0-3 0.1UF R518 AGND C519 AGND TP501 R517 0.1UF C541 49.9 R501 C502 CLK_IN- 3.3V_PLL1 C531 12PF C501 0.1UF APPROVED CLK_OUT+ 100 CLK_IN+ DATE C520 PECL/CML/LVDS CLK CIRCUITRY D DESCRIPTION 4 3 <PTD_ENGINEER> 2 D SCALE NONE SHEET 5 1 OF 6 8 6 7 2 3 4 5 1 REVISIONS REV DESCRIPTION APPROVED DATE FAST_SPI_EN 1 DRVDD 3P3V_DIGITAL DNI AGND 10K R629 DRVDD R626 1.1K 5 Y1 3 A2 Y2 4 IN 1 FPGA_SDIO DUT_SDIO 10 SA SB 9 7 D 8 3P3V_DIGITAL IN CYP_SDO R606 GND 2 DNI 0 C602 0.1UF 1 AGND 3P3V_DIGITAL DNI LAYOUT: PLACE C705 NEAR DUT AGND KP_VDDIO R608 DNI 0 TP601 AGND D U603 ADG734BRUZ TP604 6 1 A1 100K R602 10K R601 U601 NC7WZ07P6X VCC CYP_SDI R605 1.1K DNI 3 D R603 1.1K C601 0.1UF D U603 2 SA ADG734BRUZ 4 SB DRVDD C603 0.1UF DNI 16 CYP_SDIO VDD 15 NC15 6 GND 5 VSS AGND DNI AGND CYP_CSB 3 A2 Y2 4 R612 GND NC7WZ16P6X 2 AGND AGND 13 D DUT_CSB R616 0 0 DUT_SCLK SPI & FPGA CONN. DNI DCO+ DNC7 D1+ D3+ D5+ D7+ D9+ D11+ D13+ A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 FDB D0+ D2+ D4+ D6+ D8+ D10+ D12+ OR+ C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 PLUG HEADER PLUG HEADER PLUG HEADER D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 DCODNC6 D1D3D5D7D9D11D13- D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 DCO+ R633 DNC7 100 DNI R634 DCO- 100 R635 DNI DNI D3+ 100 R636 D5+ 100 DNI R637 D7+ 100 DNI R638 D1+ DNC6 D1- D3- D5D7- FDB R642 D0+ 100 R643 D9+ R639 D11+ 100 DNI R640 D4+ 100 DNI R645 D6+ 100 DNI R646 D8+ 100 DNI R647 100 D10+ R648 D11- D12+ 100 DNI R649 100 100 OR+ 100 B D4D6- D8- D10D12- DNI OR- R650 DNI D2- DNI D9- D13- R641 D0- 100 DNI R644 100 DNI D13+ DNI D2+ 100 DNI FDA D0D2D4D6D8D10D12OR- FDA DNI P602 P602 BG1 BG2 BG3 BG4 BG5 BG6 BG7 BG8 BG9 BG10 DG1 DG2 DG3 DG4 DG5 DG6 DG7 DG8 DG9 DG10 AGND 6469169-1 AGND B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 P602 P602 P601 P601 BG1 BG2 BG3 BG4 BG5 BG6 BG7 BG8 BG9 BG10 PLUG HEADER 1 PLUG HEADER 1 DNI DNI TP612 1 TP611 DNI TP610 TP609 DNI DNI TP608 TP607 1 P601 P601 C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 1 P602 PLUG HEADER BRINGING SYNC, OEN AND PDWN TO FPGA PLACE 0R RESISTORS NEAR THE DUT 1 P602 PLUG HEADER 0 DNI 0 DNI 0 DNI ADL5202_CSA A DG1 DG2 DG3 DG4 DG5 DG6 DG7 DG8 DG9 DG10 A SCHEMATIC AGND AN A LOG DEV CES AGND THIS DRAWING IS THE PROPERTY OF ANALOG DEVICES INC. IT IS NOT TO BE REPRODUCED OR COPIED, IN WHOLE OR IN PART, OR USED IN FURNISHING INFORMATION TO OTHERS, 9643 & 6649 ENGINEERING EVAL. PCB AD9643 Engineering Board DESIGN VIEW <DESIGN_VIEW> DRAWING NO. REV 9643EE01 B OR FOR ANY OTHER PURPOSE DETRIMENTAL TO THE INTERESTS OF ANALOG DEVICES. SIZE PTD ENGINEER THE EQUIPMENT SHOWN HEREON MAY BE PROTECTED BY PATENTS OWNED OR CONTROLLED BY OWNED ANALOG DEVICES. 8 7 C USING FIFO5 PLUG HEADER PDWN R630 R631 R632 TP606 DNI 0 SYNC OEN PLUG HEADER CYP_CSB2 CYP_CSB 1 CYP_CSB2 1 B1 B2 B3 FAST_SPI_EN B4 CYP_SDO B5 CYP_SDI B6 CYP_SCLK B7 FPGA_SCLK FPGA_CSB B8 B9 FPGA_SDIO B10 ADL5202_CSB PLUG HEADER TP605 PLUG HEADER B 10K R627 DNI A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 PLUG HEADER P601 P601 R628 AGND AGND 3P3V_DIGITAL USB_CSB2 ADG734BRUZ 1 LAYOUT: ROUTE ALL TRACES TO THE TYCO CONN ON TOP OF BOARD DNI AGND TP603 FPGA_SCLK R613 DNI DNI DNI 12 SA 14 SB 18 D 19 SA 17 SB 100K R611 FPGA_CSB NOTE: THIS SYMBOL IS DRAWN GIVEN INPUT 1 LOGIC TP602 100K 6 10K Y1 R610 1 A1 U603 ADG734BRUZ 11 DNI VCC CYP_SCLK IN IN R615 10K 1 AGND U602 5 C ADG734BRUZ U603 C604 0.1UF 10K R609 DRVDD 20 FAST_SPI_EN DNI U603 6 5 4 3 <PTD_ENGINEER> 2 D SCALE NONE SHEET 6 1 OF 6