12-Bit, 80 MSPS, 3 V A/D Converter AD9236 Data Sheet FEATURES

advertisement

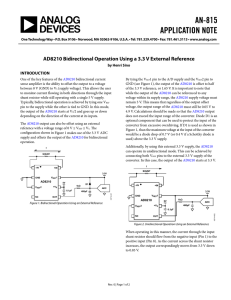

12-Bit, 80 MSPS, 3 V A/D Converter AD9236 Data Sheet FEATURES FUNCTIONAL BLOCK DIAGRAM Single 3 V supply operation (2.7 V to 3.6 V) SNR = 70.4 dBc to Nyquist SFDR = 87.8 dBc to Nyquist Low power: 366 mW Differential input with 500 MHz bandwidth On-chip reference and sample-and-hold DNL = ±0.4 LSB Flexible analog input: 1 V p-p to 2 V p-p range Offset binary or twos complement data format Clock duty cycle stabilizer AVDD DRVDD AD9236 VIN+ 8-STAGE 1 1/2-BIT PIPELINE MDAC1 SHA VIN– 4 A/D 16 3 A/D REFT REFB CORRECTION LOGIC OTR 12 OUTPUT BUFFERS D11 (MSB) VREF APPLICATIONS D0 (LSB) SENSE High end medical imaging equipment IF sampling in communications receivers WCDMA, CDMA-One, CDMA-2000 Battery-powered instruments Hand-held scopemeters Low cost digital oscilloscopes DTV subsystems CLOCK DUTY CYCLE STABILIZER CLK AGND MODE SELECT PDWN MODE DGND 03066-0-001 Figure 1. GENERAL DESCRIPTION The AD9236 is a monolithic, single 3 V supply, 12-bit, 80 MSPS analog-to-digital converter featuring a high performance sampleand-hold amplifier (SHA) and voltage reference. The AD9236 uses a multistage differential pipelined architecture with output error correction logic to provide 12-bit accuracy at 80 MSPS and guarantee no missing codes over the full operating temperature range. The wide bandwidth, truly differential SHA allows a variety of user-selectable input ranges and common modes, including single-ended applications. It is suitable for multiplexed systems that switch full-scale voltage levels in successive channels and for sampling single-channel inputs at frequencies well beyond the Nyquist rate. Combined with power and cost savings over previously available analog-to-digital converters, the AD9236 is suitable for applications in communications, imaging, and medical ultrasound. A single-ended clock input is used to control all internal conversion cycles. A duty cycle stabilizer (DCS) compensates for wide variations in the clock duty cycle while maintaining excellent overall ADC performance. The digital output data is Rev. C 0.5V REF SELECT presented in straight binary or twos complement formats. An out-of-range (OTR) signal indicates an overflow condition that can be used with the most significant bit to determine low or high overflow. Fabricated on an advanced CMOS process, the AD9236 is available in a 28-lead TSSOP and a 32-lead LFCSP and is specified over the industrial temperature range (−40°C to +85°C). PRODUCT HIGHLIGHTS 1. The AD9236 operates from a single 3 V power supply and features a separate digital output driver supply to accommodate 2.5 V and 3.3 V logic families. 2. Operating at 80 MSPS, the AD9236 consumes a low 366 mW. 3. The patented SHA input maintains excellent performance for input frequencies up to 100 MHz, and can be configured for single-ended or differential operation. 4. The AD9236 is pin compatible with the AD9215, AD9235, and AD9245. This allows a simplified migration from 10 bits to 14 bits and 20 MSPS to 80 MSPS. 5. The DCS maintains overall ADC performance over a wide range of clock pulse widths. 6. The OTR output bit indicates when the signal is beyond the selected input range. Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com AD9236 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 Equivalent Circuits ......................................................................... 10 Applications ....................................................................................... 1 Typical Performance Characteristics ........................................... 11 General Description ......................................................................... 1 Theory of Operation ...................................................................... 14 Functional Block Diagram .............................................................. 1 Analog Input and Reference Overview ................................... 14 Product Highlights ........................................................................... 1 Clock Input Considerations ...................................................... 15 Revision History ............................................................................... 2 Power Dissipation and Standby Mode .................................... 16 DC Specifications ............................................................................. 3 Digital Outputs ........................................................................... 16 AC Specifications .............................................................................. 4 Timing.......................................................................................... 17 Digital Specifications........................................................................ 5 Voltage Reference ....................................................................... 17 Switching Specifications .................................................................. 6 Operational Mode Selection ..................................................... 18 Absolute Maximum Ratings ............................................................ 7 Evaluation Board ........................................................................ 18 Thermal Resistance ...................................................................... 7 Outline Dimensions ....................................................................... 33 ESD Caution .................................................................................. 7 Ordering Guide .......................................................................... 34 Terminology ...................................................................................... 8 Pin Configurations and Function Descriptions ........................... 9 REVISION HISTORY 2/13—Rev. B to Rev. C Changed CP-32-2 Package to CP-32-7 Package ............. Universal Changes to Figure 4 .......................................................................... 9 Updated Outline Dimensions ....................................................... 33 Changes to Ordering Guide .......................................................... 34 1/06—Rev. A to Rev. B Changes to Figure 29 ...................................................................... 15 Changes to Equation in Jitter Considerations Section .............. 16 Changes to Internal Reference Connection Section, Figure 34, and Table 10..................................................................................... 17 Changes to Figure 35 ...................................................................... 18 Changes to Figure 38 ...................................................................... 20 Changes to Figure 39 ...................................................................... 21 Changes to Figure 48 ...................................................................... 27 Changes to Figure 49 ...................................................................... 28 Changes to Figure 50 ...................................................................... 29 Changes to Table 12 ........................................................................ 32 Updated Outline Dimensions ....................................................... 33 Changes to Ordering Guide .......................................................... 34 10/03—Rev. 0 to Rev. A Changes to Figure 30...................................................................... 15 Changes to Figure 33 ..................................................................... 17 Changes to Figure 40...................................................................... 22 Changes to Figure 49...................................................................... 28 Changes to Figure 50...................................................................... 29 Changes to Table 11 ....................................................................... 32 Changes to Ordering Guide .......................................................... 33 Rev. C | Page 2 of 36 Data Sheet AD9236 DC SPECIFICATIONS AVDD = 3 V, DRVDD = 2.5 V, sample rate = 80 MSPS, 2 V p-p differential input, 1.0 V external reference, unless otherwise noted. Table 1. Parameter RESOLUTION ACCURACY No Missing Codes Offset Error 1 Gain Error Gain Error1 Differential Nonlinearity (DNL) 2 Integral Nonlinearity (INL)2 TEMPERATURE DRIFT Offset Error1 Gain Error Gain Error1 INTERNAL VOLTAGE REFERENCE Output Voltage Error (1 V) Load Regulation @ 1.0 mA Output Voltage Error (0.5 V) Load Regulation @ 0.5 mA INPUT REFERRED NOISE VREF = 0.5 V VREF = 1.0 V ANALOG INPUT Input Span, VREF = 0.5 V Input Span, VREF = 1.0 V Input Capacitance 3 REFERENCE INPUT RESISTANCE POWER SUPPLIES Supply Voltage AVDD DRVDD Supply Current IAVDD 4 IDRVDD4 PSRR POWER CONSUMPTION Low Frequency Input4 Standby Power 5 Min 12 AD9236BRU/AD9236BCP Typ Max Temp Full Test Level VI Full Full 25°C Full Full Full VI VI V VI VI VI Guaranteed ±0.30 ±0.10 ±0.30 ±0.40 ±0.35 Full Full Full V V V ±6 ±12 ±18 Full 25°C 25°C 25°C VI V V V ±2 0.8 ±1 0.1 25°C 25°C V V 0.55 0.28 LSB rms LSB rms Full Full Full Full IV IV V V 1 2 7 7 V p-p V p-p pF kΩ Full Full IV IV Full 25°C 25°C 25°C 25°C 2.7 2.25 ±1.30 ±4.34 ±0.65 ±1.20 Unit Bits % FSR % FSR % FSR LSB LSB ppm/°C ppm/°C ppm/°C ±35 mV mV mV mV 3.0 2.5 3.6 3.6 V V VI V V 122 8 ±0.01 137 mA mA % FSR V V 366 1.0 mW mW With a 1.0 V internal reference. Measured at low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit. 3 Input capacitance refers to the effective capacitance between one differential input pin and AGND. Refer to Figure 5 for the equivalent analog input structure. 4 Measured at AC Specifications conditions without output drivers. 5 Measured with a dc input, CLK pin inactive (that is, set to AVDD or AGND). 1 2 Rev. C | Page 3 of 36 AD9236 Data Sheet AC SPECIFICATIONS AVDD = 3 V, DRVDD = 2.5 V, sample rate = 80 MSPS, 2 V p-p differential input, 1.0 V external reference, AIN = –0.5 dBFS, DCS off, unless otherwise noted. Table 2. Parameter SIGNAL-TO-NOISE-RATIO (SNR) fIN = 2.4 MHz fIN = 40 MHz fIN = 70 MHz fIN = 100 MHz SIGNAL-TO-NOISE AND DISTORTION (SINAD) fIN = 2.4 MHz fIN = 40 MHz fIN = 70 MHz fIN = 100 MHz EFFECTIVE NUMBER OF BITS (ENOB) fIN = 2.4 MHz fIN = 40 MHz fIN = 70 MHz fIN = 100 MHz WORST SECOND OR THIRD fIN = 2.4 MHz fIN = 40 MHz fIN = 70 MHz fIN = 100 MHz SPURIOUS FREE DYNAMIC RANGE (SFDR) fIN = 2.4 MHz fIN = 40 MHz fIN = 70 MHz fIN = 100 MHz Temp Test Level Min Full 25°C 25°C Full 25°C 25°C VI V V IV V V 68.6 Full 25°C 25°C Full 25°C 25°C VI V V IV V V 68.4 Full 25°C 25°C Full 25°C 25°C VI V V IV V V 11.1 Full 25°C 25°C Full 25°C 25°C VI V V VI V V Full 25°C 25°C Full 25°C 25°C VI V V IV V V Rev. C | Page 4 of 36 AD9236BRU/AD9236BCP Typ Max dB dB dB dB dB dB 70.9 70.4 67.8 70.1 69.0 dB dB dB dB dB dB 70.8 70.2 67.4 69.8 68.0 Bits Bits Bits Bits Bits Bits 11.5 11.4 10.9 11.3 11.0 –75.6 –91.3 –87.8 –73.2 –81.4 –76.4 75.6 91.3 87.8 73.2 81.4 76.4 Unit dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc dBc Data Sheet AD9236 DIGITAL SPECIFICATIONS AVDD = 3 V, DRVDD = 2.5 V, 1.0 V external reference, unless otherwise noted. Table 3. Parameter LOGIC INPUTS (CLK, PDWN) High Level Input Voltage Low Level Input Voltage High Level Input Current Low Level Input Current Input Capacitance DIGITAL OUTPUTS (D0–D11, OTR) 1 DRVDD = 3.3 V High Level Output Voltage (IOH = 50 µA) High Level Output Voltage (IOH = 0.5 mA) Low Level Output Voltage (IOH = 1.6 mA) Low Level Output Voltage (IOH = 50 µA) DRVDD = 2.5 V High Level Output Voltage (IOH = 50 µA) High Level Output Voltage (IOH = 0.5 mA) Low Level Output Voltage (IOH = 1.6 mA) Low Level Output Voltage (IOH = 50 µA) 1 AD9236BRU/AD9236BCP Min Typ Max Temp Test Level Full Full Full Full Full IV IV IV IV V 2.0 Full Full Full Full IV IV IV IV 3.29 3.25 Full Full Full Full IV IV IV IV 2.49 2.45 Output voltage levels measured with 5 pF load on each output. Rev. C | Page 5 of 36 0.8 +10 +10 –10 –10 2 Unit V V µA µA pF 0.2 0.05 V V V V 0.2 0.05 V V V V AD9236 Data Sheet SWITCHING SPECIFICATIONS AVDD = 3 V, DRVDD = 2.5 V, unless otherwise noted. Table 4. Parameter CLOCK INPUT PARAMETERS Maximum Conversion Rate Minimum Conversion Rate CLK Period CLK Pulse Width High1 CLK Pulse Width Low1 DATA OUTPUT PARAMETERS Output Propagation Delay (tPD)2 Pipeline Delay (Latency) Aperture Delay (tA) Aperture Uncertainty (Jitter, tJ) Wake-Up Time3 OUT OF RANGE RECOVERY TIME 1 2 3 Temp Test Level Min Full Full Full Full Full VI V V V V 80 Full Full Full Full Full Full V V V V V V AD9236BRU/AD9236BCP Typ Max Unit MSPS MSPS ns ns ns 1 12.5 4.0 4.0 3.5 7 1.0 0.3 7 2 ns Cycles ns ps rms ms Cycles With duty cycle stabilizer (DCS) enabled. Output propagation delay is measured from CLK 50% transition to DATA 50% transition, with 5 pF load. Wake-up time is dependant on the value of the decoupling capacitors; typical values shown with 0.1 μF and 10 μF capacitors on REFT and REFB. N N+1 N+2 N–1 tA ANALOG INPUT N+8 N+3 N+7 N+4 N+5 N+6 CLK DATA OUT N–9 N–8 N–7 N–6 N–5 N–4 N–3 N–2 N–1 N tPD = 6.0ns MAX 2.0ns MIN 03066-0-002 Figure 2. Timing Diagram Table 5. Explanation of Test Levels Test Level I II III IV V VI Definitions 100% production tested. 100% production tested at 25°C and guaranteed by design and characterization at specified temperatures. Sample tested only. Parameter is guaranteed by design and characterization testing. Parameter is a typical value only. 100% production tested at 25°C and guaranteed by design and characterization for industrial temperature range. Rev. C | Page 6 of 36 Data Sheet AD9236 ABSOLUTE MAXIMUM RATINGS Table 6. With Respect to Parameter ELECTRICAL AVDD AGND DRVDD DGND AGND DGND AVDD DRVDD D0 to D11 DGND CLK, MODE AGND VIN+, VIN– AGND VREF AGND SENSE AGND REFT, REFB AGND PDWN AGND ENVIRONMENTAL Storage Temperature Operating Temperature Range Lead Temperature (Soldering 10 sec) Junction Temperature THERMAL RESISTANCE Min Max Unit –0.3 –0.3 –0.3 –3.9 –0.3 –0.3 –0.3 –0.3 –0.3 –0.3 –0.3 +3.9 +3.9 +0.3 +3.9 DRVDD + 0.3 AVDD + 0.3 AVDD + 0.3 AVDD + 0.3 AVDD + 0.3 AVDD + 0.3 AVDD + 0.3 V V V V V V V V V V V –65 –40 +125 +85 300 °C °C °C 150 °C θJA is specified for the worst-case conditions on a 4-layer board in still air, in accordance with EIA/JESD51-1. Table 7. Package Type RU-28 CP-32-7 θJA 67.7 32.5 θJC Unit 32.71 °C/W °C/W Airflow increases heat dissipation effectively, reducing θJA. In addition, more metal directly in contact with the package leads from metal traces, through holes, ground, and power planes reduces the θJA. It is recommended that the exposed paddle be soldered to the ground plane for the LFCSP package. There is an increased reliability of the solder joints, and maximum thermal capability of the package is achieved with the exposed paddle soldered to the customer board. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. ESD CAUTION ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. Rev. C | Page 7 of 36 AD9236 Data Sheet TERMINOLOGY Analog Bandwidth (Full Power Bandwidth) The analog input frequency at which the spectral power of the fundamental frequency (as determined by the FFT analysis) is reduced by 3 dB. Signal-to-Noise and Distortion (SINAD)1 The ratio of the rms input signal amplitude to the rms value of the sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. Aperture Delay (tA) The delay between the 50% point of the rising edge of the clock and the instant at which the analog input is sampled. Effective Number of Bits (ENOB) The effective number of bits for a sine wave input at a given input frequency can be calculated directly from its measured SINAD using the following formula Aperture Uncertainty (Jitter, tJ) The sample-to-sample variation in aperture delay. ENOB = Integral Nonlinearity (INL) The deviation of each individual code from a line drawn from negative full scale through positive full scale. The point used as negative full scale occurs ½ LSB before the first code transition. Positive full scale is defined as a level 1½ LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line. Differential Nonlinearity (DNL, No Missing Codes) An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 12-bit resolution indicates that all 4096 codes must be present over all operating ranges. Offset Error The major carry transition should occur for an analog value ½ LSB below VIN+ = VIN–. Offset error is defined as the deviation of the actual transition from that point. Gain Error The first code transition should occur at an analog value ½ LSB above negative full scale. The last transition should occur at an analog value 1½ LSB below positive full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions. Temperature Drift The temperature drift for offset error and gain error specifies the maximum change from the initial (25°C) value to the value at TMIN or TMAX. Power Supply Rejection Ratio The change in full scale from the value with the supply at the minimum limit to the value with the supply at its maximum limit. Total Harmonic Distortion (THD) 1 The ratio of the rms input signal amplitude to the rms value of the sum of the first six harmonic components. (SINAD − 1.76 ) 6.02 Signal-to-Noise Ratio (SNR)1 The ratio of the rms input signal amplitude to the rms value of the sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc. Spurious Free Dynamic Range (SFDR)1 The difference in dB between the rms input signal amplitude and the peak spurious signal. The peak spurious component may or may not be a harmonic. Two-Tone SFDR1 The ratio of the rms value of either input tone to the rms value of the peak spurious component. The peak spurious component may or may not be an IMD product. Clock Pulse Width and Duty Cycle Pulse width high is the minimum amount of time that the clock pulse should be left in the Logic 1 state to achieve rated performance. Pulse width low is the minimum time the clock pulse should be left in the low state. At a given clock rate, these specifications define an acceptable clock duty cycle. Minimum Conversion Rate The clock rate at which the SNR of the lowest analog signal frequency drops by no more than 3 dB below the guaranteed limit. Maximum Conversion Rate The clock rate at which parametric testing is performed. Output Propagation Delay (tPD) The delay between the clock rising edge and the time when all bits are within valid logic levels. Out-of-Range Recovery Time The time it takes for the ADC to reacquire the analog input after a transition from 10% above positive full scale to 10% above negative full scale, or from 10% below negative full scale to 10% below positive full scale. 1 AC specifications may be reported in dBc (degrades as signal levels are lowered) or in dBFS (always related back to converter full scale). Rev. C | Page 8 of 36 Data Sheet AD9236 1 28 D11 (MSB) 2 27 D10 SENSE 3 26 D9 VREF 4 25 D8 REFB 5 24 DRVDD REFT 6 23 DGND AVDD 7 AGND 8 VIN+ 9 20 D5 VIN– 10 19 D4 22 D7 21 D6 AGND 11 18 D3 AVDD 12 17 D2 CLK 13 AD9236 TOP VIEW (Not to Scale) 24 23 22 21 20 19 18 17 VREF SENSE MODE OTR D11 (MSB) D10 D9 D8 NOTES 1. DNC = DO NOT CONNECT. 2. IT IS RECOMMENDED THAT THE EXPOSED PADDLE BE SOLDERED TO THE GROUND PLANE FOR THE LFCSP. THERE IS AN INCREASED RELIABILITY OF THE SOLDER JOINTS, AND THE MAXIMUM THERMAL CAPABILITY OF THE PACKAGE IS ACHIEVED WITH THE EXPOSED PADDLE SOLDERED TO THE CUSTOMER BOARD. 03066-0-022 16 D1 PDWN 14 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 TOP VIEW (Not to Scale) DNC CLK DNC PDWN DNC DNC (LSB) D0 D1 D2 D3 D4 D5 D6 D7 DGND DRVDD AD9236 32 31 30 29 28 27 26 25 OTR MODE AVDD AGND VIN– VIN+ AGND AVDD REFT REFB PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS 15 D0 (LSB) 03066-0-021 Figure 3. 28-Lead TSSOP Figure 4. 32-Lead LFCSP Table 8. Pin Function Descriptions—28-Lead TSSOP Table 9. Pin Function Descriptions—32-Lead LFCSP Pin No. 1 2 Mnemonic OTR MODE 3 4 5 6 7, 12 8, 11 9 10 13 14 15 to 22, 25 to 28 23 24 SENSE VREF REFB REFT AVDD AGND VIN+ VIN– CLK PDWN D0 (LSB) to D11 (MSB) DGND DRVDD Pin No. 1, 3, 5, 6 2 4 7 to 14, 17 to 20 15 16 21 22 Mnemonic DNC CLK PDWN D0 (LSB) to D11 (MSB) DGND DRVDD OTR MODE 23 24 25 26 27, 32 28, 31 29 30 SENSE VREF REFB REFT AVDD AGND VIN+ VIN– EP Description Out-of-Range Indicator Data Format Select and DCS Mode Selection Reference Mode Selection Voltage Reference Input/Output Differential Reference (–) Differential Reference (+) Analog Power Supply Analog Ground Analog Input Pin (+) Analog Input Pin (–) Clock Input Pin Power-Down Function Select Data Output Bits Digital Output Ground Digital Output Driver Supply Rev. C | Page 9 of 36 Description Do Not Connect Clock Input Pin Power-Down Function Select Data Output Bits Digital Output Ground Digital Output Driver Supply Out-of-Range Indicator Data Format Select and DCS Mode Selection Reference Mode Selection Voltage Reference Input/Output Differential Reference (–) Differential Reference (+) Analog Power Supply Analog Ground Analog Input Pin (+) Analog Input Pin (–) Exposed Pad. It is recommended that the exposed paddle be soldered to the ground plane for the LFCSP. There is an increased reliability of the solder joints, and the maximum thermal capability of the package is achieved with the exposed paddle soldered to the customer board. AD9236 Data Sheet EQUIVALENT CIRCUITS AVDD DRVDD D11-D0, OTR VIN+, VIN– 03600-0-005 03600-0-003 Figure 5. Equivalent Analog Input Circuit Figure 7. Equivalent Digital Output Circuit AVDD AVDD CLK, PDWN MODE 20k 03600-0-004 03600-0-006 Figure 6. Equivalent MODE Input Circuit Figure 8. Equivalent Digital Input Circuit Rev. C | Page 10 of 36 Data Sheet AD9236 TYPICAL PERFORMANCE CHARACTERISTICS AVDD = 3.0 V, DRVDD = 2.5 V, sample rate = 80 MSPS, DCS disabled, TA = 25°C, 2 V p-p differential input, AIN = –0.5 dBFS, VREF = 1.0 V external, unless otherwise noted. 0 100 AIN = –0.5dBFS SNR = 71.0dBc ENOB = 11.5 BITS SFDR = 93.6dBc –10 90 SNR/SFDR (dBc AND dBFS) –20 SFDR (dBFS) AMPLITUDE (dBFS) –30 –40 –50 –60 –70 –80 –90 –100 SFDR (dBc) 80 SFDR = 90dB REFERENCE LINE 70 SNR (dBFS) 60 SNR (dBc) 50 –110 –120 0 5 10 15 20 25 30 35 40 –30 40 –25 FREQUENCY (MHz) –20 –15 –10 –5 03066-0-031 Figure 9. Single Tone 8K FFT @ 2.5 MHz 03066-0-048 Figure 12. Single Tone SNR/SFDR vs. Input Amplitude (AIN) @ 2.5 MHz 0 100 AIN = –0.5dBFS SNR = 70.6dBc ENOB = 11.4 BITS SFDR = 87.8dBc –10 SFDR (dBFS) 90 SNR/SFDR (dBc AND dBFS) –20 –30 AMPLITUDE (dBFS) 0 INPUT AMPLITUDE (dBFS) –40 –50 –60 –70 –80 –90 –100 SFDR (dBc) 80 SFDR = 90dB REFERENCE LINE 70 SNR (dBFS) SNR (dBc) 60 50 –110 –120 0 5 10 15 20 25 30 35 40 –30 40 –25 FREQUENCY (MHz) –20 –15 –10 –5 0 INPUT AMPLITUDE (dBFS) 03066-0-032 Figure 10. Single Tone 8K FFT @ 39 MHz 03066-0-049 Figure 13. Single Tone SNR/SFDR vs. Input Amplitude (AIN) @ 39 MHz 0 100 AIN = –0.5dBFS SNR = 70.1dBc ENOB = 11.3 BITS SFDR = 81.9dBc –10 –20 SFDR (DIFF) 90 –40 SNR/SFDR (dBc) AMPLITUDE (dBFS) –30 –50 –60 –70 –80 SFDR (SE) 80 SNR (DIFF) 70 SNR (SE) –90 60 –100 –110 –120 50 0 5 10 15 20 25 30 35 40 0 FREQUENCY (MHz) 20 40 60 80 100 SAMPLE RATE (MSPS) 03066-0-033 03066-0-042 Figure 11. Single Tone 8K FFT @ 70 MHz Figure 14. SNR/SFDR vs. Sample Rate @ 10 MHz Rev. C | Page 11 of 36 AD9236 Data Sheet 0 SFDR (dBFS) AIN = –6.5dBFS SNR = 71.3dBFS SFDR = 92.5dBc –10 100 SNR/SFDR (dBc AND dBFS) –20 AMPLITUDE (dBFS) –30 –40 –50 –60 –70 –80 –90 90 SFDR (dBc) 80 70 SNR (dBFS) SFDR = 90dB REFERENCE LINE 60 SNR (dBc) 50 –100 –110 40 –30 –120 0 5 10 15 20 25 30 35 40 –27 –24 –21 –18 –15 –12 –9 –6 INPUT AMPLITUDE (dBFS) FREQUENCY (MHz) 03066-0-039 03066-0-036 Figure 15. Two-Tone 8K FFT @ 30 MHz and 31 MHz Figure 18. Two-Tone SNR/SFDR vs. Input Amplitude @ 30 MHz and 31 MHz 0 100 AIN = –6.5dBFS SNR = 71.0dBFS SFDR = 79.3dBc –10 –20 SNR/SFDR (dBc AND dBFS) –30 AMPLITUDE (dBFS) SFDR (dBFS) 90 –40 –50 –60 –70 –80 –90 –100 SFDR (dBc) 80 70 SNR (dBFS) 60 SFDR = 90dB REFERENCE LINE SNR(dBc) 50 –110 –120 0 5 10 15 20 25 30 35 40 –30 40 –27 –24 FREQUENCY (MHz) –21 –18 –15 –12 03066-0-037 Figure 16. Two-Tone 8K FFT @ 69 MHz and 70 MHz –6 03066-0-040 Figure 19. Two-Tone SNR/SFDR vs. Input Amplitude @ 69 MHz and 70 MHz 1.0 1.0 0.8 0.8 0.6 0.6 0.4 0.4 0.2 0.2 DNL (LSB) INL (LSB) –9 INPUT AMPLITUDE (dBFS) 0 –0.2 0 –0.2 –0.4 –0.4 –0.6 –0.6 –0.8 –0.8 –1.0 –1.0 0 1024 2048 3072 4096 0 CODE 1024 2048 3072 4096 CODE 03066-0-038 03066-0-041 Figure 17. Typical INL Figure 20. Typical DNL Rev. C | Page 12 of 36 Data Sheet AD9236 72.0 100 71.5 95 71.0 –40C –40C 90 SFDR (dBc) SNR (dBc) 70.5 +25C 70.0 +85C 69.5 +85C 85 +25C 80 69.0 75 68.5 68.0 70 0 25 50 75 100 125 0 25 INPUT FREQUENCY (MHz) 50 75 100 125 INPUT FREQUENCY (MHz) 03066-0-045 03066-0-047 Figure 21. SNR vs. Input Frequency Figure 24. SFDR vs. Input Frequency 95 0 SFDR (DCS ON) –10 90 –20 –30 SFDR (DCS OFF) AMPLITUDE (dBFS) SNR/SFDR (dBc) 85 80 SNR (DCS OFF) 75 70 65 –40 –50 –60 –70 –80 –90 SNR (DCS ON) –100 60 –110 55 30 35 40 45 50 55 60 65 –120 70 0 DUTY CYCLE (%) 0 –20 AMPLITUDE (dBFS) –30 –40 –50 –60 –70 –80 –90 –100 –110 –120 15.36 23.04 23.04 30.72 Figure 25. 32K FFT WCDMA Carrier @ FIN =76.8 MHz, Sample Rate = 61.44 MSPS –10 7.68 15.36 03066-0-061 Figure 22. SNR/SFDR vs. Clock Duty Cycle 0 7.68 FREQUENCY (MHz) 03066-0-046 30.72 FREQUENCY (MHz) 03066-0-060 Figure 23. 32K FFT CDMA-2000 Carrier @ FIN = 46.08 MHz, Sample Rate = 61.44 MSPS Rev. C | Page 13 of 36 AD9236 Data Sheet THEORY OF OPERATION The AD9236 architecture consists of a front-end sample-andhold amplifier (SHA) followed by a pipelined switched capacitor ADC. The pipelined ADC is divided into three sections, consisting of a 4-bit first stage followed by eight 1.5-bit stages and a final 3-bit flash. Each stage provides sufficient overlap to correct for flash errors in the preceding stages. The quantized outputs from each stage are combined into a final 12-bit result in the digital correction logic. The pipelined architecture permits the first stage to operate on a new input sample, while the remaining stages operate on preceding samples. Sampling occurs on the rising edge of the clock. Each stage of the pipeline, excluding the last, consists of a low resolution flash ADC connected to a switched capacitor DAC and interstage residue amplifier (MDAC). The residue amplifier magnifies the difference between the reconstructed DAC output and the flash input for the next stage in the pipeline. One bit of redundancy is used in each stage to facilitate digital correction of flash errors. The last stage simply consists of a flash ADC. Referring to Figure 27, the clock signal alternately switches the SHA between sample mode and hold mode. When the SHA is switched into sample mode, the signal source must be capable of charging the sample capacitors and settling within one-half of a clock cycle. A small resistor in series with each input can help reduce the peak transient current required from the output stage of the driving source. In addition, a small shunt capacitor can be placed across the inputs to provide dynamic charging currents. This passive network creates a low-pass filter at the ADC’s input; therefore, the precise values are dependant upon the application. In IF undersampling applications, any shunt capacitors should be reduced or removed. In combination with the driving source impedance, they would limit the input bandwidth. H 5pF CPAR T The input stage contains a differential SHA that can be ac- or dc-coupled in differential or single-ended modes. The outputstaging block aligns the data, carries out the error correction, and passes the data to the output buffers. The output buffers are powered from a separate supply, allowing adjustment of the output voltage swing. During power-down, the output buffers go into a high impedance state. ANALOG INPUT AND REFERENCE OVERVIEW The analog input to the AD9236 is a differential switched capacitor SHA that has been designed for optimum performance while processing a differential input signal. The SHA input can support a wide common-mode range (VCM) and maintain excellent performance, as shown in Figure 26. An input common-mode voltage of midsupply minimizes signaldependant errors and provides optimum performance. T T VIN+ 5pF VIN– CPAR T H 03066-0-012 Figure 27. Switched-Capacitor SHA Input For best dynamic performance, the source impedances driving VIN+ and VIN– should be matched such that common-mode settling errors are symmetrical. These errors are reduced by the common-mode rejection of the ADC. An internal differential reference buffer creates positive and negative reference voltages, REFT and REFB, that define the span of the ADC core. The output common mode of the reference buffer is set to midsupply, and the REFT and REFB voltages and span are defined as follows: 100 REFT = ½(AVDD + VREF) 95 SFDR (2.5MHz) REFB = ½(AVDD + VREF) 90 Span = 2 × (REFT − REFB) = 2 × VREF SNR/SFDR (dBc) 85 SFDR (39MHz) 80 It can be seen from the previous equations that the REFT and REFB voltages are symmetrical about the midsupply voltage and, by definition, the input span is twice the value of the VREF voltage. 75 SNR (2.5MHz) 70 SNR (39MHz) 65 60 55 50 0.5 1.0 1.5 2.0 2.5 3.0 COMMON-MODE LEVEL (V) 03066-0-016 The internal voltage reference can be pin strapped to fixed values of 0.5 V or 1.0 V, or adjusted within the same range as discussed in the Internal Reference Connection section. Maximum SNR performance is achieved with the AD9236 set to the largest input span of 2 V p-p. The relative SNR degradation is 3 dB when changing from 2 V p-p mode to 1 V p-p mode. Figure 26. SNR, SFDR vs. Common-Mode Level Rev. C | Page 14 of 36 Data Sheet AD9236 The SHA can be driven from a source that keeps the signal peaks within the allowable range for the selected reference voltage. The minimum and maximum common-mode input levels are defined as: VCM MIN = 33Ω 2V p-p 49.9Ω 20pF 33Ω VREF 2 VCM MAX = AVDD VIN+ AD9236 VIN– AGND 1kΩ ( AVDD + VREF ) 0.1µF 2 1kΩ 03600-0-014 The minimum common-mode input level allows the AD9236 to accommodate ground referenced inputs. Although optimum performance is achieved with a differential input, a single-ended source can be applied to VIN+ or VIN–. In this configuration, one input accepts the signal, while the opposite input should be set to midscale by connecting it to an appropriate reference. For example, a 2 V p-p signal can be applied to VIN+ while a 1 V reference is applied to VIN–. The AD9236 then accepts an input signal varying between 2 V and 0 V. In the single-ended configuration, distortion performance can degrade significantly as compared to the differential case. However, the effect is less noticeable at lower input frequencies. Differential Input Configurations Figure 29. Differential Transformer-Coupled Configuration The signal characteristics must be considered when selecting a transformer. Most RF transformers saturate at frequencies below a few MHz, and excessive signal power can also cause core saturation, which leads to distortion. Single-Ended Input Configuration A single-ended input can provide adequate performance in cost-sensitive applications. In this configuration, there is a degradation in SFDR and distortion performance due to the large input common-mode swing (see Figure 14). However, if the source impedances on each input are matched, there should be little effect on SNR performance. Figure 30 details a typical single-ended input configuration. As previously detailed, optimum performance is achieved while driving the AD9236 in a differential input configuration. For baseband applications, the AD8138 differential driver provides excellent performance and a flexible interface to the ADC. The output common-mode voltage of the AD8138 is easily set to AVDD/2, and the driver can be configured in a Sallen-Key filter topology to provide band limiting of the input signal. 1kΩ 2V p-p 33Ω 0.33µF 1kΩ 49.9Ω 20pF 1kΩ + 10µF 0.1µF 33Ω AVDD VIN+ AD9236 VIN– 1kΩ AGND 03600-A-015 1V p-p 49.9Ω Figure 30. Single-Ended Input Configuration 499Ω 33Ω 499Ω AD8138 1kΩ CLOCK INPUT CONSIDERATIONS VIN+ AD9236 33Ω 523Ω 0.1µF 20pF AVDD 1kΩ 499Ω VIN– AGND 03066-0-013 Figure 28. Differential Input Configuration Using the AD8138 At input frequencies in the second Nyquist zone and above, the performance of most amplifiers is not adequate to achieve the true performance of the AD9236. This is especially true in IF undersampling applications where frequencies in the 70 MHz to 100 MHz range are being sampled. For these applications, differential transformer coupling is the recommended input configuration. The value of the shunt capacitor is dependent on the input frequency and source impedance and should be reduced or removed. An example is shown in Figure 29. Typical high speed ADCs use both clock edges to generate a variety of internal timing signals, and as a result can be sensitive to clock duty cycle. Commonly a 5% tolerance is required on the clock duty cycle to maintain dynamic performance characteristics. The AD9236 contains a clock duty cycle stabilizer (DCS) that retimes the nonsampling edge, providing an internal clock signal with a nominal 50% duty cycle. This allows a wide range of clock input duty cycles without affecting the performance of the AD9236. As shown in Figure 22, noise and distortion performance is nearly flat for a 30% to 70% duty cycle with the DCS on. The duty cycle stabilizer uses a delay-locked loop (DLL) to create the nonsampling edge. As a result, any changes to the sampling frequency require approximately 100 clock cycles to allow the DLL to acquire and lock to the new rate. Rev. C | Page 15 of 36 AD9236 Data Sheet Jitter Considerations High speed, high resolution ADCs are sensitive to the quality of the clock input. The degradation in SNR at a given input frequency (fINPUT) due only to aperture jitter (tJ) can be calculated with the following equation: 425 120 400 The clock input should be treated as an analog signal in cases where aperture jitter can affect the dynamic range of the AD9236. Power supplies for clock drivers should be separated from the ADC output driver supplies to avoid modulating the clock signal with digital noise. Low jitter, crystal controlled oscillators make the best clock sources. If the clock is generated from another type of source (by gating, dividing, or other methods), it should be retimed by the original clock at the last step. 75 SNR (dBc) 0.2ps MEASURED SNR 60 0.5ps 55 1.0ps 1.5ps 50 2.0ps 2.5ps 3.0ps 45 40 10 100 80 TOTAL POWER 60 350 40 325 20 DIGITAL CURRENT 300 10 20 30 40 50 60 70 80 90 0 100 SAMPLE RATE (MSPS) 03066-0-044 Figure 32. Power and Current vs. Sample Rate @ 2.5 MHz Reducing the capacitive load presented to the output drivers can minimize digital power consumption. The data in Figure 32 was taken with the same operating conditions as the Typical Performance Characteristics, and with a 5 pF load on each output driver. By asserting the PDWN pin high, the AD9236 is placed in standby mode. In this state, the ADC typically dissipates 1 mW if the CLK and analog inputs are static. During standby, the output drivers are placed in a high impedance state. Reasserting the PDWN pin low returns the AD9236 to its normal operational mode. 70 65 375 CURRENT (mA) 100 In the equation, the rms aperture jitter represents the rootmean square of all jitter sources, which include the clock input, analog input signal, and ADC aperture jitter specification. IF undersampling applications are particularly sensitive to jitter (see Figure 31). 1 140 ANALOG CURRENT POWER (mW) 1 SNR 20 log 10 2f INPUT t J which is determined by the sample rate and the characteristics of the analog input signal. 1000 INPUT FREQUENCY (MHz) 03066-0-043 Figure 31. SNR vs. Input Frequency and Jitter POWER DISSIPATION AND STANDBY MODE As shown in Figure 32, the power dissipated by the AD9236 is proportional to its sample rate. The digital power dissipation is determined primarily by the strength of the digital drivers and the load on each output bit. The maximum DRVDD current (IDRVDD) can be calculated as IDRVDD = VDRVDD × CLOAD × fCLK × N I DRVDD VDRVDD C LOAD f CLK N where N is the number of output bits, 12 in the case of the AD9236. This maximum current occurs when every output bit switches on every clock cycle, that is, a full-scale square wave at the Nyquist frequency, fCLK/2. In practice, the DRVDD current is established by the average number of output bits switching, Low power dissipation in standby mode is achieved by shutting down the reference, reference buffer, and biasing networks. The decoupling capacitors on REFT and REFB are discharged when entering standby mode and then must be recharged when returning to normal operation. As a result, the wake-up time is related to the time spent in standby mode, and shorter standby cycles result in proportionally shorter wake-up times. With the recommended 0.1 μF and 10 μF decoupling capacitors on REFT and REFB, it takes approximately 1 second to fully discharge the reference buffer decoupling capacitors and 7 ms to restore full operation. DIGITAL OUTPUTS The AD9236 output drivers can be configured to interface with 2.5 V or 3.3 V logic families by matching DRVDD to the digital supply of the interfaced logic. The output drivers are sized to provide sufficient output current to drive a wide variety of logic families. However, large drive currents tend to cause current glitches on the supplies, which can affect converter performance. Applications requiring the ADC to drive large capacitive loads or large fanouts can require external buffers or latches. As detailed in Table 11, the data format can be selected for either offset binary or twos complement. Rev. C | Page 16 of 36 Data Sheet AD9236 TIMING The AD9236 provides latched data outputs with a pipeline delay of seven clock cycles. Data outputs are available one propagation delay (tPD) after the rising edge of the clock signal. Refer to Figure 2 for a detailed timing diagram. In all reference configurations, REFT and REFB drive the A/D conversion core and establish its input span. The input range of the ADC always equals twice the voltage at the reference pin for either an internal or an external reference. VIN+ The length of the output data lines and the loads placed on them should be minimized to reduce transients within the AD9236. These transients can degrade the converter’s dynamic performance. VIN– 0.1F ADC CORE + 0.1F 10F REFB The lowest typical conversion rate of the AD9236 is 1 MSPS. At clock rates below 1 MSPS, dynamic performance can degrade. 0.1F VREF 10F VOLTAGE REFERENCE REFT + 0.1F SELECT LOGIC A stable and accurate 0.5 V voltage reference is built into the AD9236. The input range can be adjusted by varying the reference voltage applied to the AD9236 using either the internal reference or an externally applied reference voltage. The input span of the ADC tracks reference voltage changes linearly. The various reference modes are summarized in Table 10 and described in the following sections. SENSE 0.5V AD9236 03066-A-017 Figure 33. Internal Reference Configuration If the ADC is being driven differentially through a transformer, the reference voltage can be used to bias the center tap (common-mode voltage). VIN+ VIN– REFT Internal Reference Connection A comparator within the AD9236 detects the potential at the SENSE pin and configures the reference into four possible states, which are summarized in Table 10. If SENSE is grounded, the reference amplifier switch is connected to the internal resistor divider (see Figure 33), setting VREF to 1 V. Connecting the SENSE pin to VREF switches the reference amplifier output to the SENSE pin, completing the loop and providing a 0.5 V reference output. If a resistor divider is connected as shown in Figure 34, the switch is again set to the SENSE pin. This puts the reference amplifier in a noninverting mode with the VREF output defined as follows: ADC CORE 0.1F 0.1F REFB 0.1F VREF + 10F 0.1F R2 VREF 0.5 1 R1 SELECT LOGIC R2 SENSE R1 0.5V AD9236 03066-0-018 Figure 34. Programmable Reference Configuration Table 10. Reference Configuration Summary Selected Mode External Reference Internal Fixed Reference Programmable Reference SENSE Voltage AVDD VREF 0.2 V to VREF Resulting VREF (V) N/A 0.5 Internal Fixed Reference AGND to 0.2 V 1.0 R2 (See Figure 34) 0 . 5 1 R1 Resulting Differential Span (V p-p) 2 × External Reference 1.0 2 × VREF 2.0 Rev. C | Page 17 of 36 + 10F AD9236 Data Sheet If the internal reference of the AD9236 is used to drive multiple converters to improve gain matching, the loading of the reference by the other converters must be considered. Figure 35 depicts how the internal reference voltage is affected by loading. A 2 mA load is the maximum recommended load. 0.05 As discussed in the Digital Outputs section, the AD9236 can output data in either offset binary or twos complement format. There is also a provision for enabling or disabling the clock duty cycle stabilizer (DCS). The MODE pin is a multilevel input that controls the data format and DCS state. The input threshold values and corresponding mode selections are outlined in Table 11. Table 11. Mode Selection 0 –0.05 ERROR (%) OPERATIONAL MODE SELECTION MODE Voltage AVDD 2/3 AVDD 1/3 AVDD AGND (Default) 0.5V ERROR (%) –0.10 1.0V ERROR (%) –0.15 Data Format Twos Complement Twos Complement Offset Binary Offset Binary Duty Cycle Stabilizer Disabled Enabled Enabled Disabled –0.20 EVALUATION BOARD –0.25 0 0.5 1.0 1.5 LOAD (mA) 2.0 2.5 3.0 03066-0-019 Figure 35. VREF Accuracy vs. Load External Reference Operation The use of an external reference can be necessary to enhance the gain accuracy of the ADC or to improve thermal drift characteristics. When multiple ADCs track one another, a single reference (internal or external) can be necessary to reduce gain matching errors to an acceptable level. Figure 36 shows the typical drift characteristics of the internal reference in both 1.0 V and 0.5 V modes. When the SENSE pin is tied to AVDD, the internal reference is disabled, allowing the use of an external reference. An internal reference buffer loads the external reference with an equivalent 7 kΩ load. The internal buffer still generates the positive and negative full-scale references, REFT and REFB, for the ADC core. The input span is always twice the value of the reference voltage; therefore, the external reference must be limited to a maximum of 1.0 V. 1.0 0.9 0.8 VREF ERROR (%) 0.7 0.6 VREF = 1.0V 0.5 0.4 VREF = 0.5V 0.3 0.2 0.1 0 –40 –30 –20 –10 0 10 20 30 40 50 60 70 80 The AD9236 evaluation board provides all of the support circuitry required to operate the ADC in its various modes and configurations. Complete schematics and layout plots follow and demonstrate the proper routing and grounding techniques that should be applied at the system level. It is critical that signal sources with very low phase noise (< 1 ps rms jitter) be used to realize the ultimate performance of the converter. Proper filtering of the input signal, to remove harmonics and lower the integrated noise at the input, is also necessary to achieve the specified noise performance. TSSOP Evaluation Board Figure 37 shows the typical bench setup used to evaluate the ac performance of the AD9236. The AD9236 can be driven singleended or differentially through an AD8138 driver or a transformer. Separate power pins are provided to isolate the DUT from the support circuitry. Each input configuration can be selected by proper connection of various jumpers (refer to the schematics). The AUXCLK input should be selected in applications requiring the lowest jitter and SNR performance (that is, IF undersampling characterization). It allows the user to apply a clock input signal that is 4× the target sample rate of the AD9236. A low jitter, differential divide-by-4 counter, the MC100LVEL33D, provides a 1× clock output that is subsequently returned back to the CLK input via JP9. For example, a 260 MHz signal (sinusoid) is divided down to a 65 MHz signal for clocking the ADC. Note that R1 must be removed with the AUXCLK interface. Lower jitter is often achieved with this interface since many RF signal generators display improved phase noise at higher output frequencies and the slew rate of the sinusoidal output signal is 4× that of a 1× signal of equal amplitude. TEMPERATURE (C) 03066-0-011 Figure 36. Typical VREF Drift Rev. C | Page 18 of 36 Data Sheet AD9236 LFCSP Evaluation Board An alternative differential analog input path using an AD8351 op amp is included in the layout but is not populated in production. Designers interested in evaluating the op amp with the ADC should remove C15, R12, and R3 and populate the op amp circuit. The passive network between the AD8351 outputs and the AD9236 allows the user to optimize the frequency response of the op amp for their application. The typical bench setup used to evaluate the ac performance of the AD9236 is similar to the TSSOP evaluation board connections. The AD9236 can be driven single-ended or differentially through a transformer. Separate power pins are provided to isolate the DUT from the support circuitry. Each input configuration can be selected by proper connection of various jumpers (see Figure 48). 3V – REFIN HP8644, 2V p-p SIGNAL SYNTHESIZER BAND-PASS FILTER 3V + – 3V + – 3V + AVDD GND DUT GND DUT S4 DRVDD AVDD XFMR INPUT AD9236 EVALUATION BOARD 10MHz HP8644, 2V p-p REFOUT CLOCK SYNTHESIZER CLOCK DIVIDER S1 CLOCK – + DVDD J1 DATA CAPTURE AND PROCESSING 03066-0-024 Figure 37. TSSOP Evaluation Board Connections Rev. C | Page 19 of 36 TB1 TB1 TB1 TB1 TB1 AVDDIN DRVDDIN AGND DVDDIN TB1 Rev. C | Page 20 of 36 Figure 38. TSSOP Evaluation Board Schematic, DUT 6 4 5 1 3 2 C6 22µF 25V 25V C48 22µF 25V C47 22µF 25V C58 22µF 4 RP4 22Ω 5 3 RP4 22Ω 6 2 RP4 22Ω 7 1 RP4 22Ω 8 4 RP3 22Ω 5 3 RP3 22Ω 6 2 RP3 22Ω 7 1 RP3 22Ω 8 AGND DUTAVDDIN D7O D6O D5O D4O D3O D2O D1O D0O L1 OTRO D11O D10O D9O D8O C14 0.1µF FBEAD 21 C53 0.1µF FBEAD 2 C52 0.1µF FBEAD 2 L4 L3 1 L2 1 C59 0.1µF F FBEAD 21 D7 D6 D5 D4 D3 D2 D1 D0 JP11 AVDD DUTDRVDD 5kΩ R27 JP13 DUTAVDD OTR D11 D10 D9 D8 AVDD TP11 TP12 TP13 TP14 BLK BLK BLK BLK TP4 RED DVDD TP10 TP15 TP16 TP9 BLK BLK BLK BLK TP3 RED JP12 AVDD RED TP1 RED TP2 4 RP6 22Ω 5 3 RP6 22Ω 6 2 RP6 22Ω 7 1 RP6 22Ω 8 4 RP5 22Ω 5 3 RP5 22Ω 6 2 RP5 22Ω 7 22Ω 1 RP5 8 1kΩ R42 1kΩ R17 1kΩ R20 R4 10kΩ R3 10kΩ JP2 JP1 JP6 JP7 C21 10µF 10V C57 0.1µF 0.1µF C35 C33 0.1µF JP24 JP25 JP23 C23 10µF 10V DUTAVDD C32 0.1µF C34 0.1µF 10V 10µF C20 WHT TP5 C38 0.1µF C22 10µF 10V JP22 C41 0.001µF C50 0.1µF VIN+ VIN– WHT TP17 0.001µF C39 C36 0.1µF DUTAVDD C1 10µF 10V C37 0.1µF OTR D11 28 D10 27 D9 26 D8 25 D7 22 D6 21 D5 20 D4 19 D3 18 D2 17 D1 16 D0 15 CLK 13 AD9236 AVDD 71 AGND 8 SENSE 3 VREF 4 PDWN 14 REFB 5 REFT 6 MODE U1 2 VIN+ 9 VIN– 10 AGND 11 AVDD 12 DGND 23 DRVDD 24 C40 0.001µF 03066-0-007 OTRO D0O D1O D2O D3O D4O D5O D6O D7O D8O D9O D10O D11O DUTCLK WHT TP6 DUTDRVDD AD9236 Data Sheet 1 Rev. C | Page 21 of 36 2 1 CLOCK S1 R14 90 R1 49.9 JP9 C27 0.1F R11 49.9 AUXCLK R12 113 AVDD 2 S5 0.1F C13 R19 500 AVDD CW R2 10k C24 0.1F 1 2 3 4 R18 500 74VHC04 2 C26 0.1F 5 Figure 39. TSSOP Evaluation Board Schematic, Clock Inputs and Output Buffering 9 11 13 3 6 1N5712 8 74VHC04 U8 10 74VHC04 U8 12 74VHC04 U8 4 74VHC04 U8 JP3 JP4 R7 22 R26 10k D2 D1 C28 10F 10V 74VHC04 U8 AVDD;14 AGND;7 AVDD U3 DECOUPLING AVDD TP7 WHT U8 1 R15 90 R13 113 AVDD MC100LVEL33D 8 VCC NC 7 OUT U3 INA 6 REF INB 5 VEE INCOM 3 4 T2 2 1 5 6 T1-1T R25 10k D0 D1 D2 D3 D4 D5 D6 D7 C10 0.1F OTR D9 D10 D11 D8 G1 G2 2 A1 3 A2 4 A3 5 A4 6 A5 7 A6 8 A7 9 A8 1 19 U8 DECOUPLING AVDD R9 22 DUTCLK AVDD C3 10F 10V Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 16 15 14 13 12 11 18 17 G2 U7 74VHC541 GND 10 20 C5 10F 10V 2 1 VCC C11 0.1F 15 14 13 12 11 18 17 16 DVDD C4 10F 1 G1 2 A1 3 A2 4 A3 5 A4 6 A5 7 A6 8 A7 9 A8 1 19 10V 2 VCC 20 10 GND U6 74VHC541 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 C12 0.1F 8 7 6 5 4 3 2 1 8 7 6 5 4 3 2 1 22 22 22 12 RP1 RP1 RP1 22 11 22 10 22 9 RP2 RP2 RP2 12 22 RP2 14 15 22 13 RP2 9 16 RP2 22 RP2 22 22 RP2 22 22 10 RP1 RP1 22 11 RP1 13 14 15 22 RP1 16 22 RP1 DACLK DOTR DD0 DD1 DD2 DD3 DD4 DD5 DD6 DD7 DD8 DD9 DD10 DD11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 11 1 3 5 7 9 HEADER RIGHT ANGLE MALE NO EJECTORS J1 03066-0-008 14 16 18 20 22 24 26 28 30 32 34 36 38 40 10 12 2 4 6 8 Data Sheet AD9236 1N5712 Rev. C | Page 22 of 36 2 AMP INPUT 1 S2 Figure 40. TSSOP Evaluation Board Schematic, Analog Inputs 12 R31 49.9 C19 10F 1 10V C18 0.1F 2 B JP8 A R35 499 R34 523 3 C2 R37 499 VAL C69 0.33F C15 10F 10V 1 + 2 ALT VEE TP8 RED 3 6 VAL C17 R36 499 VCC 4 VO+ –IN 2 1 VOC U2 8 +IN VO– AD8138 VEE 5 AVDD C8 0.1F 1 R10 40 R6 40 2 XFMR INPUT 1 S4 2 R33 1k R32 1k AVDD S3 SINGLE INPUT R24 49.9 VAL VAL C9 0.33F R5 49.9 JP5 4 5 6 C45 C42 T1 T1-1T R41 1k R23 1k 3 2 1 AVDD C7 0.1F R8 1k R16 1k AVDD C25 0.33F C16 0.1F JP43 JP41 JP46 JP45 JP40 JP42 03066-A-009 R22 33 R21 33 C43 DNP C44B 20pF C44 DNP VIN– VIN+ AD9236 Data Sheet Data Sheet AD9236 DACLK DD0 DD1 DD2 DD3 DD4 DD5 DD6 DD7 DD8 DD9 DD10 DD11 1 2 3 4 5 6 7 8 9 10 11 12 13 14 MSB–DB11 CLOCK DB10 DVDD DB19 DCOM DB8 AD9762 NC3 DB7 AVDD DB6 COMP2 DB5 IOUTA U4 DB4 IOUTB DB3 ACOM DB2 COMP1 DB1 FSADJ DB0 REFIO NC1 REFLO SLEEP NC2 28 27 26 25 24 23 22 21 20 19 18 17 16 15 DVDD C30 0.1F C31 0.01F C29 0.1F C46 0.01F TP18 WHT C56 0.01F S6 R29 49.9 C51 0.01F R30 2k C49 0.01F C55 22pF R28 49.9 C54 22pF 03066-0-010 Figure 41. TSSOP Evaluation Board Schematic, Optional D/A Converter 03066-0-025 Figure 42. TSSOP Evaluation Board Layout, Primary Side Rev. C | Page 23 of 36 AD9236 Data Sheet 03066-0-026 Figure 43. TSSOP Evaluation Board Layout, Secondary Side 03066-0-027 Figure 44. TSSOP Evaluation Board Layout, Ground Plane Rev. C | Page 24 of 36 Data Sheet AD9236 03066-0-028 Figure 45. TSSOP Evaluation Board Layout, Power Plane 03066-0-029 Figure 46. TSSOP Evaluation Board Layout, Primary Silkscreen Rev. C | Page 25 of 36 AD9236 Data Sheet 03066-0-030 Figure 47. TSSOP Evaluation Board Layout, Secondary Silkscreen Rev. C | Page 26 of 36 Rev. C | Page 27 of 36 GND J1 GND 0.1F C12 Figure 48. LFCSP Evaluation Board Schematic, Analog Inputs and DUT PRI SEC GND C9 0.10F GND R11 36 R12 0.1F C11 C18 0.10F GND R2 XX AVDD GND D R36 1k R15 33 R13 1k C23 10pF GND OR L1 FOR FILTER AVDD C19 20pF P4 P3 R25 1k GND AVDD 3 2 4 P1 AVDD GND VIN+ VIN– R6 1k R7 1k R5 1k GND GND GND C21 10pF R26 1k C22 10F GND GND R4 33 R SINGLE ENDED R3 0 C5 0.1F C26 10pF GND R18 25 AMPINB R3, R16, C18 ONLY ONE SHOULD BE ON BOARD AT A TIME XOUTB GND C16 0.1F R10 36 E 45 XOUT AMPIN p10 C C29 10F E C7 0.1F R12, R42, C17 ONLY ONE SHOULD BE ON BOARD AT A TIME. 6 2 CT 4 PRI SEC OPTIONAL XFR T2 FT C1–1–13 5 1 XOUT X FRIN 2 CT 3 4 GND XOUTB C15 AMP 0.1F R42 0 T1 ADT1–1WT XFRIN1 1 5 NC 3 GND L1 10nH C6 0.1F FOR SINGLE ENDED INPUT PLACE R18, R19, R42, C6, AND C18. REMOVE R3, R12, C15, C17, AND C27. GND R9 10k P7 A B AVDD C13 GND 0.10F P11 P9 P8 REFB GND 26 REFT 27 AVDD 28 AGND 29 VIN+ 30 VIN– 31 AGND 32 AVDD 25 MODE 2 P5 24 R1 10k 23 22 21 P6 GND C8 0.1F U4 AD9236 AVDD P14 CLK P13 R8 1k 12 11 10 9 6 7 8 GND MODE PIN SOLDERABLE JUMPER: 5 TO 1: TWOS COMPLEMENT/DCS OFF 5 TO 2: TWOS COMPLEMENT/DCS ON 5 TO 3: OFFSET BINARY/DCS ON 5 TO 4: OFFSET BINARY/DCS OFF 03066-A-050 D0X 10 9 7 8 SENSE PIN SOLDERABLE JUMPER: E TO A: EXTERNAL VOLTAGE DIVIDER E TO B: INTERNAL 1V REFERENCE (DEFAULT) E TO C: EXTERNAL REFERENCE E TO D: INTERNAL 0.5V REFERENCE D2X D1X 11 12 5 D4X D3X D6X D5X D8X D7X D9X D10X D12X D11X DRX D13X 6 13 15 14 4 RP1 220 13 4 5 16 15 14 2 3 1 16 1 RP2 220 H4 MTHOLE6 H3 MTHOLE6 H2 MTHOLE6 H1 MTHOLE6 10 D2 9 (LSB) DRVDD GND (MSB) 6 5 GND 2 3 12 13 15 14 16 3 GND OVERRANGE BIT 4 GND 2.5V DRVDD 2 P2 11 DRVDD DGND D7 D6 D5 D4 D3 1 AVDD 3.0V 1 20 19 VDL 2.5V AVDD 18 17 VREF SENSE MODE OTR D11 D10 D9 D8 1 DNC 2 CLK 3 DNC 4 PDWN 5 DNC 6 DNC 7 D0 8 D1 VAMP 5.0V EXTREF 1V MAX E1 Data Sheet AD9236 LSB MSB Rev. C | Page 28 of 36 2DB IN 26 2D7 27 GND 28 2D6 29 2D5 30 V 31 CC 2D4 32 2D3 33 GND 34 2D2 35 2D1 36 1D8 37 1D7 38 GND 39 1D6 40 1D5 41 VCC 42 1D4 43 1D3 44 GND 45 1D2 46 1D1 47 1CLK 48 25 2CLK 1 U1 Figure 49. LFCSP Evaluation Board Schematic, Digital Path GND R19 50 AMP IN AMP R41 10k VAMP 24 1Q1 2 1 GND GND DRVDD GND GND DRVDD GND GND C35 0.10F R33 RPG2 5 25 6 COMM 7 OPLO INLO 4 10 VOCM 9 VPOS 8 OPHI R34 1.2k U3 AD8351 C44 0.1F R38 1k INHI 3 PWDN 1 RGP1 2 DRY VAMP GND TO USE AMPLIFIER PLACE ALL COMPONENTS SHOWN HERE (RIGHT) EXCEPT R40 OR R41. REMOVE R12, R3, R18, R42, C6, C15, AND C18. OUT 1OE 3 7 6 1Q3 5 GND 4 1Q2 CC 1Q4 C28 0.1F R35 25 GND 2OE 2QB 23 2Q7 22 GND 21 2Q6 20 2Q5 19 VCC 18 2Q4 17 2Q3 16 GND 15 2Q2 14 2Q1 13 1Q8 12 1Q7 11 GND 10 1Q6 9 1Q5 8 V R40 10k GND POWER DOWN USE R40 OR R41 CLKLAT/DAC GND D0X DRVDD D2X D1X D4X D3X GND D5X D7X D6X GND D8X D10X D9X DRVDD GND D12X D11X DRX D13X CLKAT/DAC 74LVTH162374 GND R14 25 VAMP R39 1k C45 0.1F C24 10F R17 0 R16 0 GND GND GND MSB C17 0.1F C27 0.1F GND DRY GND DR GND AMPINB AMPIN 4 6 8 2 10 10 12 12 14 14 16 16 18 18 20 20 22 22 24 24 26 26 28 28 30 30 32 32 34 34 36 36 38 38 40 40 8 4 6 2 P12 HEADER 40 11 7 9 3 5 1 13 13 15 15 17 17 19 19 21 21 23 23 25 25 27 27 29 29 31 31 33 33 35 35 37 37 39 39 11 9 3 5 7 1 03066-A-051 GND AD9236 Data Sheet C4 10F GND Figure 50. LFCSP Evaluation Board Schematic, Clock Input Rev. C | Page 29 of 36 J2 GND R29 50 C43 0.1F ENC ENCX GND R30 1k R31 1k VDL R27 0 R28 0 VDL VDL E43 E44 E35 E51 E52 VDL E31 VDL E50 CLK ENC C33 C14 0.1F 0.001F ANALOG BYPASSING C32 0.001F CLOCK TIMING ADJUSTMENTS GND ENCODE C25 10F GND AVDD FOR A BUFFERED ENCODE USE R28 FOR A DIRECT ENCODE USE R27 AVDD C3 10F DUT BYPASSING C10 10F VDL DRVDD R20 1k GND GND R24 1k GND R21 1k GND E53 GND R32 1k C41 0.1F DRVDD C30 0.001F 5 9 10 12 13 3A 3B 4A 4B 2B 1 1A 2 1B 4 2A C31 0.1F U5 4Y 3Y 2Y 1Y 74VCX86 DIGITAL BYPASSING C2 10F PWR GND 14 8 11 6 7 3 C34 0.1F VDL GND ENCX C36 0.1F R23 0 C1 C39 0.001F 0.1F CLKLAT/DAC R37 25 Rx DNP DR VDL R22 0 GND C49 0.001F LATCH BYPASSING C47 0.1F SCHEMATIC SHOWS TWO GATE DELAY SETUP. FOR ONE DELAY, REMOVE R22 AND R37 AND ATTACH Rx (Rx = 0). C38 0.001F C48 0.001F GND VAMP C20 10F C40 0.001F 03066-A-052 C46 10F C37 0.1F Data Sheet AD9236 AD9236 Data Sheet 03066-0-055 03066-0-053 Figure 51. LFCSP Evaluation Board Layout, Primary Side Figure 53. LFCSP Evaluation Board Layout, Ground Plane 03066-0-056 03066-0-054 Figure 54. LFCSP Evaluation Board Layout, Power Plane Figure 52. LFCSP Evaluation Board Layout, Secondary Side Rev. C | Page 30 of 36 Data Sheet AD9236 03066-0-057 03066-0-058 Figure 56. LFCSP Evaluation Board Layout, Secondary Silkscreen Figure 55. LFCSP Evaluation Board Layout, Primary Silkscreen Rev. C | Page 31 of 36 AD9236 Data Sheet Table 12. LFCSP Evaluation Board Bill of Materials Item Qty. Omit 1 Reference Designator 1 18 C1, C5, C7, C8, C9, C11, C12, C13, C15, C16, C31, C33, C34, C36, C37, C41, C43, C47 8 C6, C18, C27, C17, C28, C35, C45, C44 2 8 C2, C3, C4, C10, C20, C22, C25, C29 2 C46, C24 Device Chip Capacitors Package 0603 Value 0.1 µF Tantalum Capacitors TAJC 10 µF 3 8 Chip Capacitors 0603 0.001 µF 4 1 C14, C30, C32, C38, C39, C40, C48, C49 C19 Chip Capacitor 0603 20 pF 5 1 C26 Chip Capacitors 0603 10 pF Headers EHOLE 2 6 9 Jumper Blocks E1, E45 7 2 J1, J2 SMA Connectors/50 Ω SMA 8 1 L1 Inductor 0603 9 1 P2 Terminal Block TB6 10 1 P12 Header Dual 20-Pin RT Angle HEADER40 11 5 R3, R12, R23, R28, RX Chip Resistors 0603 0Ω 12 2 R4, R15 Chip Resistors 0603 33 Ω 13 14 Chip Resistors 0603 1 kΩ 14 2 R5, R6, R7, R8, R13, R20, R21, R24, R25, R26, R30, R31, R32, R36 R10, R11 Chip Resistors 0603 36 Ω 15 1 R29 Chip Resistor 0603 50 Ω 220 Ω 6 1 Supplied by ADI C21, C23 E31, E35, E43, E44, E50, E51, E52, E53 2 Recommended Vendor/Part No. 10 nH Coilcraft/0603CS10NXGBU Wieland/25.602.2653.0, z5-530-0625-0 Digi-Key S2131-20-ND R37, R22, R42, R16, R17, R27 R19 16 2 RP1, RP2 Resistor Pack R_742 Digi-Key CTS/742C163221JTR Mini-Circuits 17 1 T1 ADT1-1WT AWT1-1T 18 1 U1 74LVTH162374 CMOS Register TSSOP-48 19 1 U4 AD9236BCP ADC (DUT) CSP-32 Analog Devices, Inc. 20 1 U5 74VCX86M SOIC-14 Fairchild 21 1 PCB AD92XXBCP/PCB PCB Analog Devices, Inc. X X 22 1 U3 AD8351 Op Amp MSOP-8 Analog Devices, Inc. 23 1 T2 M/A-COM Transformer ETC1-1-13 1-1 TX M/A-COM/ETC1-1-13 24 5 R9, R1, R2, R38, R39 Chip Resistors 0603 SELECT 25 4 R18, R14, R33, R35 Chip Resistors 0603 25 Ω 26 2 R40, R41 Chip Resistors 0603 10 kΩ 27 1 R34 Chip Resistor Total 81 35 1 These items are included in the PCB design, but are omitted at assembly. Rev. C | Page 32 of 36 1.2 kΩ X Data Sheet AD9236 OUTLINE DIMENSIONS 9.80 9.70 9.60 28 15 4.50 4.40 4.30 6.40 BSC 1 14 PIN 1 0.65 BSC 0.15 0.05 COPLANARITY 0.10 0.30 0.19 1.20 MAX SEATING PLANE 8° 0° 0.20 0.09 0.75 0.60 0.45 COMPLIANT TO JEDEC STANDARDS MO-153-AE Figure 57. 28-Lead Thin Shrink Small Outline Package [TSSOP] (RU-28) Dimensions shown in millimeters 0.30 0.25 0.18 32 25 0.50 BSC TOP VIEW 0.80 0.75 0.70 SEATING PLANE 3.25 3.10 SQ 2.95 EXPOSED PAD 8 17 0.50 0.40 0.30 16 0.05 MAX 0.02 NOM COPLANARITY 0.08 0.20 REF 9 BOTTOM VIEW 0.25 MIN FOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONS SECTION OF THIS DATA SHEET. COMPLIANT TO JEDEC STANDARDS MO-220-WHHD. Figure 58. 32-Lead Frame Chip Scale Package [LFCSP_WQ] 5 mm × 5 mm Body, Very Very Thin Quad (CP-32-7) Dimensions shown in millimeters Rev. C | Page 33 of 36 PIN 1 INDICATOR 1 24 112408-A PIN 1 INDICATOR 5.10 5.00 SQ 4.90 AD9236 Data Sheet ORDERING GUIDE Model 1 AD9236BRUZ-80 AD9236BRUZRL7-80 AD9236BCPZ-80 AD9236BCPZRL7-80 1 Temperature Range –40°C to +85°C –40°C to +85°C –40°C to +85°C –40°C to +85°C Package Description 28-Lead Thin Shrink Small Outline Package (TSSOP) 28-Lead Thin Shrink Small Outline Package (TSSOP) 32-Lead Lead Frame Chip Scale (LFCSP_WQ) 32-Lead Lead Frame Chip Scale (LFCSP_WQ) Z = RoHS Compliant Part. Rev. C | Page 34 of 36 Package Option RU-28 RU-28 CP-32-7 CP-32-7 Data Sheet AD9236 NOTES Rev. C | Page 35 of 36 AD9236 Data Sheet NOTES © 2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D03066-0-2/13(C) Rev. C | Page 36 of 36