Circuit Note CN-0143

Circuits from the Lab® reference designs are engineered and tested for quick and easy system integration to help solve today’s analog, mixed-signal, and RF design challenges. For more information and/or support, visit www.analog.com/CN0143 .

Circuit Note

CN-0143

Devices Connected/Referenced

AD8042 Dual, 160 MHz Rail-to-Rail Op Amp

AD5620 Single, 12-Bit Buffered Voltage Output DAC

AD5443

High Bandwidth 12-Bit CMOS Current

Output DAC

ADR444 Precision 4.096 V Low Noise Reference

Single-Ended-to-Differential Converters for Voltage Output and

Current Output DACs Using the

AD8042

Op Amp

CIRCUIT FUNCTION AND BENEFITS

With single-ended signaling, one wire from the signal source is routed throughout the system to the data acquisition interface.

The voltage measured is the difference between the signal and the ground. Unfortunately, “ground” can be a different level in different places because the ground impedance can never be zero. This can lead to errors when using single-ended inputs, especially where the signal trace is long and grounds currents contain large digital transients. Single-ended signal runs are sensitive to noise pickup because they act as an antenna, picking up electrical activity. With single-ended inputs there is no way of distinguishing between the signal and the interfering noise. Most of the ground and noise problems are solved by differential signaling.

5V

5V

U1

2.5V

8 1

GND V

DD

0V

V

IN

DIN

SCLK

7

6

DIN

SCLK

V

REFOUT

AD5620

V

FB

2

3

R1

10kΩ

SYNC_BF

5

SYNC V

OUT

4

2.5V

With differential signaling, two signal wires run from the signal source to the data acquisition interface. This can solve both of the problems caused by single-ended connections. Noise between the sending and receiving ground planes acts as a common-mode signal and is, therefore, greatly attenuated.

The use of twisted pair wire causes noise pickup to appear as a common-mode signal, which is also greatly attenuated at the receiver. Another advantage of differential transmission is that the differential signal has twice the amplitude of the equivalent single-ended signal, therefore giving greater noise immunity.

R2

10kΩ

R5

2.21kΩ

U2-A

3

5V

8

1

2

AD8042

R3

2.21kΩ

R6

2.21kΩ

5V

2.5V

0V

V+

R4

6

2.21kΩ

AD8042

7

5

4

U2-B

5V

2.5V

0V

V–

C5 0.1µF

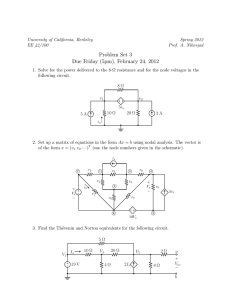

Figure 1. Differential Driver for the AD5620 Voltage Output DAC

Rev. A

Circuits from the Lab® reference designs from Analog Devices have been designed and built by Analog

Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall

Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010–2014 Analog Devices, Inc. All rights reserved.

CN-0143

Circuit Note

Here we describe a differential driver that can be adapted to either a voltage or current output DAC. The driver is based on the dual AD8042 op amp configured as a cross-coupled differential driver. The AD8042 has a rail-to-rail output stage that operates within 30 mV of either rail and an input stage that can operate 200 mV below the negative supply (ground in this circuit) and within 1 V of the positive supply. In addition, the

AD8042 has 160 MHz bandwidth and fast settling time, making it an ideal choice for the output driver.

The voltage output DAC is the 12-bit AD5620 , a member of the nano DAC® family. The DAC contains an on-chip 5 ppm/°C reference and is available in an 8-lead SOT-23 or MSOP package. The current output DAC is the 12-bit AD5443 , which is available in a 10-lead MSOP package.

The two circuits represent a cost effective, low power, and small board area solution for generating differential signals from industrial CMOS DACs. Both circuits operate on a single +5 V supply.

CIRCUIT DESCRIPTION

The circuit shown in Figure 1 operates on a single +5 V supply

and utilizes the AD5620 voltage output DAC. The input to the

DAC is controlled by an SPI port. The output of the DAC swings between 0 V and +5 V. The on-chip DAC reference (+2.5

V) is used to set the common-mode voltage of the AD8042 differential driver circuit. This reference has a temperature coefficient of 5 ppm/°C. The output at V− is the inverted DAC output centered around a common-mode

5V 5V

3.75V

2.5V

C2

0.1µF

SCLK

DIN

SYNC_BF

SDO

U1

8

V

DD

4

SCLK

5

6

7

SDIN

SYNC

AD5443

10

R

FB

1

I

OUT

1

2

I

OUT

2

GND

3

SDO

9

V

REF

1.5pF

C1

3

2

5V

8

1 voltage of +2.5 V. The feedback network and U2-B force the voltage at V+ to be 180° out of phase with respect to V−.

Waveforms for the input and output of the driver are shown in

Figure 2. The differential outputs will only go to within about

30 mV of each rail; therefore, there will be some clipping if the

DAC is operated in these regions.

1

2

V

IN

R1

10kΩ

2.21kΩ

R5

3

R2

10kΩ

5V

8

1

2

AD8042

U3-A

R3

2.21kΩ

2.21kΩ

R6

5V

3.75V

2.5V

5V

3.75V

2.5V

V+

V

IN

V+

V–

3

CH1 2V CH2 2V M50.0µs CH1 2.61V

CH3 2V

Figure 2. V

IN

, V+, and V− for Figure 1 Circuit at 100 kSPS Update Rate

The circuit shown in Figure 3 also operates on a single +5 V

supply and utilizes the AD5443 current output DAC in a mode where the IOUT2 pin is connected to +2.5 V, and the VREF pin is grounded. The ADR444 precision 4.096 V reference and a divider network are used to generate the +2.5 V for the IOUT2 pin of the DAC and the +3.75 V common-mode voltage for the output driver stage.

AD8042

U2-A

V–

0.1µF

C3

1

TP

2

3

V

IN

NC

4

GND

U4

TP

NC

ADR444

V

OUT

TRIM

8

7

6

C4

0.1µF

5

R7

3.32kΩ

R8

12kΩ

R9

24kΩ

2.5V

6

5

3.75V

AD8042

U2-B

7

4

R10

C5 0.1µF

R4

6

2.21kΩ

AD8042

U3-B

7

5

4

2.21kΩ

Figure 3. Differential Driver for the AD5443 Current Output DAC

Rev. A | Page 2 of 3

Circuit Note

Under these conditions the output of U2-A swings between

+2.5 V and +5 V. The differential outputs of the driver will only go to within about 30 mV of the positive rail; therefore, there will be some clipping if the DAC is operated in this region.

Figure 4 shows the corresponding input and output waveforms

for the output driver stage of Figure 3.

V

IN

1

V+

2

V–

3

CH1 2V CH2 2V M50.0µs CH1 3.81V

CH3 2V

Figure 4. V

IN

, V+, and V− for Figure 3 Circuit at 100 kSPS Update Rate

The single-ended-to-differential converter stage has a bandwidth of typically 10 MHz. However, the maximum output frequency is controlled by a DAC update rate, which is 125 kSPS for the AD5620 and 2.5 MSPS for the AD5443 . Sampling theory limits the maximum output frequency to about onethird the maximum update rate.

Excellent layout, grounding, and decoupling techniques must be utilized to achieve the desired performance from the circuits discussed (see Tutorial MT-031 and Tutorial MT-101 ).

COMMON VARIATIONS

The AD5640 and AD5660 are 14-bit and 16-bit versions of the

AD5620 . The AD5446 is a 14-bit version of the AD5443 .

CN-0143

LEARN MORE

Kester, Walt. The Data Conversion Handbook . Chapter 3, 7.

Analog Devices. 2005.

MT-015 Tutorial, Basic DAC Architectures II: Binary DACs .

Analog Devices.

MT-031 Tutorial, Grounding Data Converters and Solving the

Mystery of AGND and DGND . Analog Devices.

MT-101 Tutorial, Decoupling Techniques . Analog Devices.

Voltage Reference Wizard Design Tool, Analog Devices.

Data Sheets and Evaluation Boards

AD5443 Data Sheet

AD5443 Evaluation Board

AD5620 Data Sheet

AD5620 Evaluation Board

AD8042 Data Sheet

ADR444 Data Sheet

REVISION HISTORY

2/14—Rev. 0 to Rev. A

Changes to Figure 1 .......................................................................... 1

Changes to Figure 2 .......................................................................... 2

3/10—Revision 0: Initial Version

(Continued from first page) Circuits from the Lab reference designs are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors.

While you may use the Circuits from the Lab reference designs in the design of your product, no other license is granted by implication or otherwise under any patents or other intellectual property by application or use of the Circuits from the Lab reference designs. Information furnished by Analog Devices is believed to be accurate and reliable. However, Circuits from the

Lab reference designs are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability, noninfringement or fitness for a particular purpose and no responsibility is assumed by Analog Devices for their use, nor for any infringements of patents or other rights of third parties that may result from their use. Analog Devices reserves the right to change any Circuits from the Lab reference designs at any time without notice but is under no obligation to do so.

©2010–2014 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

CN08806-0-2/14(A)

Rev. A | Page 3 of 3