Volume 46, Number 4, 2012

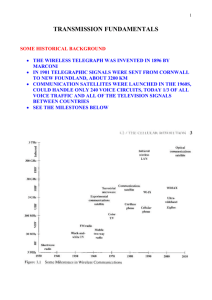

advertisement