Towards Low-Power yet High-Performance Networks-on-Chip Sunghyun Park by

advertisement

Towards Low-Power yet High-Performance

Networks-on-Chip

by

Sunghyun Park

B.S. in Korea Advanced Institute of Science and Technology (2009)

S.M. in Massachusetts Institute of Technology (2011)

Submitted to the

Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in Electrical Engineering and Computer Science

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2014

c Massachusetts Institute of Technology 2014. All rights reserved.

Author . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Department of Electrical Engineering and Computer Science

September 2, 2014

Certified by . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Li-Shiuan Peh

Professor of Electrical Engineering and Computer Science

Thesis Supervisor

Certified by . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Anantha P. Chandrakasan

Joseph F. and Nancy P. Keithley Professor of Electrical Engineering

Thesis Supervisor

Accepted by . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Leslie A. Kolodziejski

Chair, Department Committee on Graduate Students

2

Towards Low-Power yet High-Performance

Networks-on-Chip

by

Sunghyun Park

Submitted to the Department of Electrical Engineering and Computer Science

on September 2, 2014, in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

Abstract

A network-on-chip (NoC), the de-facto communication backbone in manycore processors, consumes a significant portion of total chip power, competing against the

computation cores for the limited power and thermal budget. On the other hand,

overall system performance of manycore chips increasingly relies on on-chip latency

and bandwidth as core counts scale. This thesis aims to design low-power yet highperformance NoCs through circuit and microarchitecture co-design contrary to the

traditional approaches where NoCs sacrifice latency and/or bandwidth for low-power

operation; then demonstrate such design concepts through test chip prototyping,

enabling detailed measurements for rigorous analysis of the pros and cons of the

proposed NoCs.

The thesis starts with a 4×4 mesh NoC chip prototype that tries to simultaneously optimize energy, latency and throughput for all kinds of traffic (unicasts,

multicasts and broadcasts). Its extensive experiment results make it possible to accurately analyze energy/performance benefits and timing/area overheads of the virtually

bypassed, multicast-optimized router design; energy savings, area overheads and reduced reliability of the clocked low-swing datapath circuits; and a power gap between

simulated estimations and measurement results.

Next demonstrated is a link test chip of two clockless low-swing repeater designs, a

self-resetting logic repeater (SRLR) optimized for transmission energy and a voltagelocked repeater (VLR) for transmission delay. This second chip prototype shows that

the clockless, single-ended low-swing signaling of SRLRs armed with variation-robust

circuit techniques has lower energy and smaller area than clocked, differential lowswing signaling. Featured with lower delay than full-swing repeaters, VLRs provide

the fundamental building block to the single-cycle reconfigurable NoC that enables potential power saving at architecture level through single-cycle multi-hop asynchronous

link traversal on dynamically configurable routes.

The last one-third of this thesis explores a 3D-IC chip prototype of a throughsilicon via (TSV) interconnect that can support simultaneously bi-directional (SBD)

3

signaling. While TSVs, as 3D-IC NoC links, offer an appealing solution to manycore

architectures that require huge off-die bandwidth, existing TSV technologies impose

considerable power and area overheads (using spare TSVs) to improve reliability.

The proposed SBD TSV circuit shows better energy efficiency and smaller area than

unidirectional TSVs, thus providing reliable 3D signaling within tight power/silicon

budget. Such SBD signaling also enables configurable off-die bandwidth, and hence,

can be the basis of a bandwidth-adaptive 3D NoC that efficiently supports highly

dynamic traffic on manycore chips.

Thesis Supervisor: Li-Shiuan Peh

Title: Professor of Electrical Engineering and Computer Science

Thesis Supervisor: Anantha P. Chandrakasan

Title: Joseph F. and Nancy P. Keithley Professor of Electrical Engineering

4

To my parents,

Doosoo Park and Soonsil Shin

5

6

Acknowledgments

The LORD is my shepherd, I shall not be in want. He makes me lie down in green

pastures, he leads me beside quiet waters, he restores my soul. He guides me in paths

of righteousness for his name’s sake. Even though I walk through the valley of the

shadow of death, I will fear no evil, for you are with me; your rod and your staff, they

comfort me.

Psalm 23:1-4

First and foremost, I give thanks to God for allowing me to have the best advisors,

Professor Li-Shiuan Peh and Professor Anantha Chandrakasan. Their complementary research interests and advising styles have made this possible; while Li-Shiuan’s

accurate yet wide-ranging comprehension of Networks-on-Chip (NoCs) has enabled

me to freely play in the playground of NoCs without worrying about my wrong assumptions and technical mistakes, Anantha’s sharp insight and extensive experience

in low-power digital circuit design has allowed my rough ideas to be well-positioned

and shaped in detail. Indeed, being co-advised by Li-Shiuan and Anantha was the

best opportunity that I have ever been given at MIT in that I was able to explore

unique research questions between circuit and architecture under their excellent guidance. Even from the viewpoint of humanity, they are truly great mentors. I sincerely

thank Anantha and Li-Shiuan for being my advisors.

It is my honor and pleasure to have Professor Srinivas Devadas on my thesis

committee. I would like to thank him for the contributions to my PhD work. Actually, he helped me shape the thesis direction even before being my thesis committee

through the DARPA Angstrom Project and Research Qualifying Examination (RQE).

His comprehensive system-level view and objective standpoint on my work have motivated me to view my research from other angles. I deeply appreciate him for spending

7

time and energy despite his busy schedule.

I would also like to express my appreciation to Professor Vladimir Stojanovic

for his feedback and suggestions as my RQE committee. His standpoint on on-chip

interconnects (that differs from the angle of my advisors) widened my understanding

of scalable Networks-on-Chip. In addition, his distinguished work on physical model

of on-chip wires motivated me to investigate circuit-wire codesign.

I want to extend the appreciation to my MIT colleagues who are always willing

to help me out. While all members of my both research groups deserve my gratitude,

I have to leave a special thanks to the following eight people: Tushar Krishna (NoC

architecture discussion), Masood Qazi (variation-robust circuit design and analysis),

Owen Chen (NoC architecture discussion), Gilad Yahalom (3D-IC test chip implementation), Arun Paidimarri (chip measurement), Sunghyuk Lee (PCB design), Bhavya

Daya (mesh NoC chip comparison) and SungWon Jung (high-frequency clocking circuit design).

I should leave a thanks to our friendly administrative staffs for all the help through

my PhD years at MIT: Maria Rebelo (CSAIL administration), Margaret Flaherty

(MTL administration), Janet Fischer and Alicia Duarte (EECS Department administration).

I am proud to acknowledge the support of the following companies for my research projects: MediaTek (3D-IC test chip fabrication), Samsung (financial support

during my entire PhD years) and Freescale (filp chip packaging). I would like to

thank Dr. Alice Wang for her excellent management at MediaTek to enable successful completion of our 3D-IC project. I also thank Mr. Stacy Ho to mercifully take

care of my MediaTek internship at the Woburn site. In particular, I want to express

my deepest gratitude to Samsung Scholarship not only for financially supporting my

PhD program but also for giving me an opportunity to become a part of their superior community. It was my great honor to serve as Jar-Chi-Wii-Won-Chang at 2013

Samsung Scholarship Academic Camp in Yosemite National Park.

8

No words can do justice to express how deeply grateful I am to my family members.

I truly appreciate my lovely penguin, Seonghee Nam, for always being with me as my

wife and as my best friend. Without her devoted support, I would not have completed

my PhD journey. I also thank my adorable little girl, Seohee Park, and my brave

little boy, Seungwoo Park, for giving me the strongest motivation to finish my school

life. Indeed, their existence itself is a blessing to me everyday. I should not forget to

thank my sister, Haejin Park, for her trust and encouragement. I am always proud

of her career as a professor in a medical school. I should also thank my parents-inlaw, I-hyun Nam and Soonae Song, for treating me like their son. Finally, reserving

the best for last, I would like to exhibit the most heartfelt gratitude to my parents,

Doosoo Park and Soonsil Shin, for their unconditional love and trust. I thank you, I

respect you, I love you, my dad and my mom.

9

10

List of Acronyms

3D − IC

3 Dimensional Integrated Circuit

BER

Bit Error Rate

BW

Buf f er W ritng (in Router P ipeline)

CAD

Computer Aided Design

CMOS

Complementary M etal Oxide Semiconductor

CMP

Chip M ultiP rocessor

DM

(P ulse) DeM odulator

DOR

Dimesion Ordered Routing

DRC

Design Rule Check

ECC

Error Correction Code

F2B

F ace to Back (T hrough Silicon V ia)

F2F

F ace to F ace (T hrough Silicon V ia)

FIFO

F irst In F irst Out (Buf f ers)

I/O

Input/Output

IP

Intellectual P roperty

LA

LookAhead generation (in Router P ipeline)

LT

Link T raversal (in Router P ipeline)

MC

M essage Class (of V irtual Channels)

MMS

M ultiscale M odeling and Simulation (SoC Application)

MOSFET

M etal Oxide Semiconductor F ield Ef f ect T rasistor

MPSoC

M ultiP rocessor System on Chip

11

mSA

multiple (Crossbar) Switch Allocation

NIC

N etwork Interf ace Circuit

NMOS

N − channel M OSF ET

NoC

N etwork on Chip

NRC

N ext Route Computation

PDK

P rocessor Design Kit

PE

P rocessor Element

PIP

P ersonal Interest P roject (SoC application)

PM

P ulse M odulator

PMOS

P − channel M OSF ET

PRBS

P seudo Random Binary Sequence

PVT

P rocess, V oltage and T emperature

QoS

Quality of Service

RC

Resistance − Capacitance

RSD

Reduced Swing Driver

Rx

Receiver

SA

(Crossbar) Switch Allocation (in Router P ipeline)

SBD

Simultaneously BiDirectional

Si

Silicon

SMART

Single cycle M ulti hop Asynchronous Repeated T raversal

SoC

System on Chip

SOI

Silicon On Insulator

12

SRLR

Self Resetting Logic Repeater

TSV

T hrough Silicon V ia

Tx

T ransmitter

ST

(Crossbar) Switch T raversal (in Router P ipeline)

VA

V irtual channel Allocation (in Router P ipeline)

VC

V irtual Channel

VLR

V oltage Locked Repeater

VOPD

V ideo Object P lane Decoder

WLAN

W ireless Local Area N etwork

13

14

Contents

1 Introduction

27

1.1

Research Motivation . . . . . . . . . . . . . . . . . . . . . . . . . . .

27

1.2

Mesh Network-on-Chip (NoC) . . . . . . . . . . . . . . . . . . . . . .

28

1.3

Rethinking Router Microarchitecture . . . . . . . . . . . . . . . . . .

32

1.4

Thesis Contributions and Overview . . . . . . . . . . . . . . . . . . .

38

2 Towards the Theoretical Limits of a Mesh NoC

43

2.1

Theoretical Mesh NoC Limits . . . . . . . . . . . . . . . . . . . . . .

43

2.2

Related Work: Existing Mesh NoC Chips . . . . . . . . . . . . . . . .

45

2.3

Chip Design and Fabrication . . . . . . . . . . . . . . . . . . . . . . .

49

2.3.1

Towards Theoretical Latency Limits

. . . . . . . . . . . . . .

51

2.3.2

Towards Theoretical Throughput Limits . . . . . . . . . . . .

52

2.3.3

Towards Theoretical Energy Limits . . . . . . . . . . . . . . .

53

Evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

57

2.4.1

Latency, Throughput and Energy . . . . . . . . . . . . . . . .

57

2.4.2

Virtual bypassing . . . . . . . . . . . . . . . . . . . . . . . . .

61

2.4.3

Low-Swing Signaling . . . . . . . . . . . . . . . . . . . . . . .

62

2.4.4

Power Modeling and Estimation . . . . . . . . . . . . . . . . .

65

Chapter Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . .

67

2.4

2.5

15

3 Low-Swing Datapath for Reconfigurable NoCs

71

3.1

Background: Reconfigurable NoCs . . . . . . . . . . . . . . . . . . . .

71

3.2

Introduction: Clockless Low-Swing Repeaters . . . . . . . . . . . . . .

73

3.3

Related Work: Existing Low-Swing Links . . . . . . . . . . . . . . . .

74

3.4

Self-Resetting Logic Repeater (SRLR) . . . . . . . . . . . . . . . . .

76

3.4.1

SRLR Circuit Design . . . . . . . . . . . . . . . . . . . . . . .

77

3.4.2

Test Chip Fabrication and Measurement . . . . . . . . . . . .

84

Voltage-Locked Repeater (VLR) . . . . . . . . . . . . . . . . . . . . .

87

3.5.1

VLR Circuit Design

. . . . . . . . . . . . . . . . . . . . . . .

87

3.5.2

Test Chip Fabrication and Measurement . . . . . . . . . . . .

90

Chapter Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . .

94

3.5

3.6

4 Energy and Area Efficient TSV Signaling for 3D-IC NoCs

97

4.1

Chapter Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2

Design Considerations of SBD TSV Links . . . . . . . . . . . . . . . 102

4.3

SBD Transmitter Design . . . . . . . . . . . . . . . . . . . . . . . . . 104

4.4

4.5

4.6

97

4.3.1

Case 1: EN=0 (no data to be transmitted) . . . . . . . . . . . 104

4.3.2

Case 2: EN=1 and CLK=1 (first half clock cycle) . . . . . . . 105

4.3.3

Case 3: EN=1 and CLK=0 (next half clock cycle) . . . . . . . 106

Rx Design: Switched Dual-Tree Sense Amplifier . . . . . . . . . . . . 112

4.4.1

Switched Scheme for Low Sensing Delay . . . . . . . . . . . . 112

4.4.2

Dual-Tree Sense Amplifier for Reliable SBD Signaling . . . . . 113

Prototyping and Testing of TSV Interconnects . . . . . . . . . . . . . 117

4.5.1

Maximum Data Rate . . . . . . . . . . . . . . . . . . . . . . . 119

4.5.2

Energy Efficiency . . . . . . . . . . . . . . . . . . . . . . . . . 122

4.5.3

Area Comparison . . . . . . . . . . . . . . . . . . . . . . . . . 126

4.5.4

Comparison with Other Low-Power TSV Circuits . . . . . . . 127

Chapter Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

16

5 Conclusions and Future Work

5.1

133

Thesis Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

5.1.1

Regular Mesh Network in CMPs . . . . . . . . . . . . . . . . . 134

5.1.2

Low-Swing Datapath of Configurable Meshes in SoCs . . . . . 134

5.1.3

Towards Low-Cost 3D Meshes in 3D-ICs . . . . . . . . . . . . 135

5.2

Low-Swing Signaling Reliability . . . . . . . . . . . . . . . . . . . . . 136

5.3

Future Projects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

5.3.1

Broadcast-Intensive Cache Coherent Protocols . . . . . . . . . 139

5.3.2

Error-Tolerant NoCs with Low-Swing Links . . . . . . . . . . 140

5.3.3

Bandwidth-Adaptive 3D NoCs . . . . . . . . . . . . . . . . . . 140

17

18

List of Figures

1-1 Simplified router microarchitecture for 2D mesh NoCs. . . . . . . . .

29

1-2 Detailed router microarchitecture and pipeline of a packet-switched,

input-buffered VC NoC. . . . . . . . . . . . . . . . . . . . . . . . . .

31

1-3 Ideal point-to-point interconnect only through a metal wire. . . . . .

33

1-4 Repeated interconnect for lower wire delay (starting point of wire sharing). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

33

1-5 Input wire sharing through a demultiplexer. . . . . . . . . . . . . . .

33

1-6 Output wire sharing through a multiplexer. . . . . . . . . . . . . . . .

33

1-7 Input and output wire sharing through a demultiplexer and a multiplexer. 34

1-8 Input and output wire sharing through a crossbar switch. . . . . . . .

34

1-9 Efficient wire sharing with a SA logic and buffers. . . . . . . . . . . .

34

1-10 Packet-switched, input-buffered VC router microarchitecture. . . . . .

35

2-1 Latency calculation example for broadcast traffic on a k×k mesh network. 44

2-2 Broadcast example and overview of the fabricated 4×4 mesh NoC. . .

49

2-3 Die photo and design layout of the 4×4 mesh NoC and stand-alone

low-swing crossbar switch connected to longer links (1mm and 2mm

wires). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

50

2-4 64bits 5×5 tri-state RSD-based matrix crossbar switch and link circuitry. 54

19

LIST OF FIGURES

2-5 Proposed router microarchitecture and pipeline. . . . . . . . . . . . .

56

2-6 Network performance evaluation with mixed traffic at 1GHz. . . . . .

58

2-7 Network performance evaluation with broadcast-only traffic at 1GHz.

59

2-8 Measured network power reduction at 653Gb/s at 1GHz (A: full-swing

unicast network, B: low-swing unicast network, C:low-swing broadcast

network without virtual buffer bypassing, D: low-swing broadcast network with virtual buffer bypassing). . . . . . . . . . . . . . . . . . . .

60

2-9 1mm link energy efficiency of full-swing and RSD-based signaling. . .

63

2-10 2mm link energy efficiency of full-swing and RSD-based signaling. . .

63

2-11 Low-swing signaling trade-off between reliability and energy efficiency.

65

2-12 Comparison of power estimates with measurements (A: ORION 2.0

simulations, B: Post-layout simulations, C: Measured results). . . . .

66

3-1 Single-cycle reconfigurable NoC [1] with SMART links (red bold lines)

where its backbone mesh network is reconfigured at run time. . . . .

72

3-2 10mm SRLR-based link for the mesh-based reconfigurable NoC where

the local router-to-router distance is 1mm. . . . . . . . . . . . . . . .

77

3-3 Proposed SRLR circuit and its simulated waveforms. . . . . . . . . .

78

3-4 1000-run Monte-Carlo simulation results that show the impact of each

variation-robust design technique. . . . . . . . . . . . . . . . . . . . .

82

3-5 Process variation robust SRLR circuit with (1) an alternating delay

cell design, (2) NMOS-based drivers and (3) an adaptive swing voltage

scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

83

3-6 Die photograph of the SRLR test chip in 45nm SOI CMOS that includes an on-chip test circuit and an on-chip clocking circuit. . . . . .

84

3-7 1cm link traversal (LT) energy versus bandwidth density. . . . . . . .

86

3-8 Proposed clockless low-swing voltage-locked repeater (VLR) for singlecycle multi-hop link traversal. . . . . . . . . . . . . . . . . . . . . . .

20

89

LIST OF FIGURES

3-9 Simulated waveforms at 6.8Gb/s: (a) original input data and (b) VLR’s

low-swing signaling at node X. . . . . . . . . . . . . . . . . . . . . . .

89

3-10 1bit 10mm VLR-based on-chip link and its equivalent full-swing link

fabricated on the same die as SRLRs in 45nm SOI CMOS. . . . . . .

90

3-11 SMART NoC performance across SoC applications. Reference: [1]. . .

93

3-12 SMART NoC power breakdown across SoC applications. Reference: [1]. 93

4-1 Example of hop count reduction through greater spatial locality in 3DICs. The reduced hop counts translate into lower interconnect delay

and energy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

98

4-2 Uni-directional TSV signaling versus proposed SBD TSV signaling at

the same clock frequency, e.g. 5GHz in this example. . . . . . . . . .

99

4-3 4 voltage-level SBD signaling with weaker driving strength required

(pros) and smaller noise margin between SBD signaling symbols (cons). 100

4-4 3 voltage-level SBD signaling with bigger noise margin between SBD

signaling symbols (pros) and stronger driving strength required (cons). 100

4-5 Upward die-to-die static current path through a low resistance TSV:

bottom die PMOS → micro bump → landing pad → top die NMOS.

101

4-6 Downward die-to-die static current path through a low resistance TSV:

top die PMOS → landing pad → micro bump → bottom die NMOS.

101

4-7 Proposed SBD TSV Tx circuits: a simple NAND-enabled inverter on

a bottom die and a half-clocked driver on a top die. . . . . . . . . . . 105

4-8 Tx circuit connectivity of Case 1 (EN=0). No die-to-die current path

is formed when there is no data to be transmitted through a TSV. . . 106

4-9 Tx circuit connectivity of Case 2 (EN=1 and CLK=1, first half clock

cycle) where a TSV is driven by a bottom driver only, consuming dynamic energy only. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

21

LIST OF FIGURES

4-10 Tx circuit connectivity of Case 3 (EN=1 and CLK=0, next half clock

cycle) where a TSV is driven by a bottom driver and a top driver

together, forming a static current path through a TSV for the three

voltage-level SBD signaling. The coupling capacitor, which acts as

a high-pass filter, compensates the bandwidth loss without adding to

inter-die static current. . . . . . . . . . . . . . . . . . . . . . . . . . . 108

4-11 TSV voltage transitions of uni-directional TSVs versus our SBD TSV. 110

4-12 While a floating TSV during the first half clock period also enables 50%

lower static die-to-die current, such a floating state incurs bandwidth

loss at 00 → 11 bi-directional data transition. . . . . . . . . . . . . . 111

4-13 The coupling capacitor on a top die driver enables shorter switching

time when a TSV is driven to VDD/2 by a pull-up PMOS and a pulldown NMOS together during the second half clock period. . . . . . . 111

4-14 Reduced symbol noise margin of SBD signaling due to process variation. When designing 3D-IC circuits, we should consider die-to-die

variation mismatch as well as on-die variation mismatch described in

(c). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

4-15 Switched dual-tree sense amplifiers for variation-robust SBD signaling

and low sensing delay. . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4-16 Overall circuit implementation of the proposed TSV SBD signaling.

Two types of sense amplifiers, a PMOS-input and an NMOS-input

sense amplifier, are switched on and off according to the transmitted

data (txIN) for low sensing delay. . . . . . . . . . . . . . . . . . . . . 116

4-17 Top die photograph of a 2-tier 3D-IC test chip fabricated with a 28nm

Low-Power (LP) CMOS process. . . . . . . . . . . . . . . . . . . . . . 118

4-18 Bottom die photograph of a 2-tier 3D-IC test chip fabricated with the

same process as a top die, 28nm LP CMOS. . . . . . . . . . . . . . . 118

22

LIST OF FIGURES

4-19 Four types of TSV interconnects implemented in a 3D-IC test chip: two

uni-directional TSVs (baseline #1); an inverter-based SBD TSV (baseline #2); a proposed SBD TSV without a coupling capacitor (baseline

#3); and a completed design (proposed SBD TSV). . . . . . . . . . . 119

4-20 Measured maximum die-to-die bandwidth comparison at 1.05V between uni-directional TSVs (baseline #1) and proposed SBD TSVs. . 120

4-21 Maximum bi-directional bandwidth of our fabricated F2B TSV interconnects. The proposed SBD signaling can deliver up to 9.1Gb/s/TSV

bi-directional data (i.e. 4.55GHz maximum clock frequency) at 1.05V. 121

4-22 Four bi-directional input data sets for energy comparison. . . . . . . . 123

4-23 Measured TSV interconnect energy efficiency over various input data

sets at 9.1Gb/s bi-directional data rate (i.e. 4.55GHz clock frequency)

at 1.05V. The proposed SBD signaling circuits consume 10.3-31.1% less

energy than uni-directional TSVs. . . . . . . . . . . . . . . . . . . . . 124

4-24 Normalized area comparison of the fabricated TSV signaling circuits.

While baseline #1 includes two TSV landing pads, other three SBD

TSV interconnects have only one TSV landing pad.

. . . . . . . . . 126

5-1 Lower voltage swing enables higher energy efficiency, but results in

higher signaling error probability (hence bigger system overheads).

This figure is identical to Figure 2-11. . . . . . . . . . . . . . . . . . . 137

23

LIST OF FIGURES

24

List of Tables

2.1

Theoretical limits of a k×k mesh NoC for unicast and broadcast traffic. 48

2.2

Comparison of mesh NoC chip prototypes. . . . . . . . . . . . . . . .

48

2.3

Critical path analysis results. . . . . . . . . . . . . . . . . . . . . . .

61

2.4

Area comparison with full-swing signaling. . . . . . . . . . . . . . . .

64

3.1

Comparison of silicon-proven low-swing on-chip interconnects. . . . .

86

3.2

Maximum hop counts in a single cycle at high data rate. . . . . . . .

92

3.3

Maximum hop counts in a single cycle at low data rate. . . . . . . . .

92

4.1

Comparison of Energy-efficient Face-to-Back TSV Interconnects (CMOSon-CMOS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

25

LIST OF TABLES

26

1

Introduction

This thesis challenges the conventional wisdom that involves NoC design in trading

off latency, bandwidth and energy, leading to poor performance in low-power NoCs or

high performance but with unacceptable network power.

1.1

Research Motivation

Moore’s law scaling and diminishing performance returns of complex uniprocessor

chips have led to the advent of manycore systems such as chip multiprocessors (CMPs)

and multiprocessor systems-on-chip (MPSoCs). The scalability of these manycore

chips relies highly on the on-chip communication fabric connecting the cores/IPs. An

ideal communication fabric would incur only metal-wire delay and energy between

the source and destination node. However, there is insufficient wiring for dedicated

global point-to-point wires between all nodes [2], and hence, a network-on-chip (NoC)

with routers that multiplex wires across traffic flows is becoming the de-facto communication fabric in manycore chips [3].

These on-chip routers, however, impose substantial power overhead. For instance,

36% and 39% of entire chip power are consumed by such NoC routers at the peak

network throughput in MIT’s Raw [4] and Intel’s TeraFLOPS [5], respectively. Since

27

Chapter 1. Introduction

each chip cannot cross its power wall, this power-hungry network competes against

the cores/IPs, leading to lower power and thermal budget for actual computation

work. On the other hand, overall manycore chip performance increasingly depends

on NoC performance such as bandwidth and latency with a growing number of onchip components [3, 6, 7]. Therefore, a low-power yet high-performance NoC is sorely

needed to allow more cores/IPs to be integrated on one die.

Designing a low-power NoC without the loss of network performance is almost

always a challenging task. To take a couple of easy examples (other challenges will be

discussed in Section 1.3), link drivers with a lower power supply voltage, i.e. simple

low-swing links, enable both dynamic and leakage power saving but at the cost of

longer wire propagation delay, resulting in longer latency and lower bandwidth in the

network. While smaller buffer size at a router also makes NoCs energy-efficient, it

leads to poor link utilization (hence lower bandwidth). Due to these design challenges,

prior NoC chips [4, 5, 8, 9, 10, 11] sacrificed network performance for acceptable NoC

power consumption, or endured substantial network power overheads to meet the

aggressive performance requirements. This thesis seeks to break such conventional

trade-offs to pave the way to the low-power yet high-performance NoC.

1.2

Mesh Network-on-Chip (NoC)

A mesh network, which is formed by laying out a regular grid in each dimension

and adding routers at the grid intersections, maps readily to the planar layout that

current CMOS technology requires (e.g. 2D meshes on a single Si wafer or 3D meshes

in a vertically-stacked 3D-ICs). Thanks to such planar regularity and scalability, a

mesh is the most widely-used NoC topology for high-performance manycore chips [4,

5, 8, 9, 10, 11, 12]. In addition, unlike indirect, multi-stage NoC topologies such as

Clos or Butterflies [13], a mesh supports the locality present in many applications,

allowing nearby traffic to be transported at lower delay and energy.

28

1.2. Mesh Network-on-Chip (NoC)

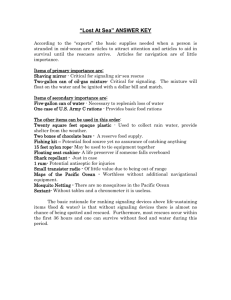

Figure 1-1: Simplified router microarchitecture for 2D mesh NoCs.

Figure 1-1 shows a simplified 5-port 2D mesh router microarchitecture composed

of four main components: input buffers, control logic, a crossbar switch and links.

The input buffers store incoming data till they are sent to the next router. The

control logic determines when data proceed through the router pipeline and sets up

the crossbar switch. The crossbar switch physically moves data from input ports to

output ports, followed by links that forward output port data to the next router.

These actions can be pipelined to improve throughput, depending on operating clock

frequency, process technology and specific logic implementation.

Let us now look at how a packet-switched NoC works in a manycore processor.

Each core communicates with other cores by sending and receiving messages through

a network interface controller (NIC) that connects the core to a router (hence the

network). Before a message is injected into the network, it is first segmented into

packets that are then divided into fixed-length flits, short for flow-control units. A

packet consists of a head flit that contains the destination address, body flits, and a

29

Chapter 1. Introduction

tail flit that indicates the end of a packet. If the amount of information the packet

carries is little, single-flit packets are also possible, i.e. where a flit is both the head

and tail flit. Because only the head flit carries the destination information, all flits of

a packet must follow the same route through the network. Virtual channels (VCs),

logically-separate input buffers, allow multiple data streams to share physical channel (link wires) by interleaving flits from different packets. Such decoupled input

buffers can be utilized to improve throughput by eliminating the head-of-line blocking; prevent deadlocks in the network without deadlock-free routing algorithms; or

offer quality of service (QoS) for system level optimization [13, 14].

Figure 1-2 shows an example of the packet-switched, input-buffered VC router microarchitecture and pipeline. One distinguishing feature of this design is the routerlevel multicast capability through multiport switch allocation (mSA) by which multicasts do not require multiple unicast packets to be injected. At the first pipeline stage,

flits get buffered (BW) and each input port chooses 1 output port request (mSA-I)

with a round-robin logic that guarantees fair and starvation-free arbitration. Since

multicast flits can require multiple output ports, the request is a 5b vector. The next

router VC is selected (VA) from a free VC queue in this stage, too. These 3 independent operations are executed in parallel without decreasing operating frequency.

At the second stage, output port requests for the next routers are computed (NRC)

for the winners of mSA-I, and concurrently, a matrix arbiter at each output port

grants the crossbar ports to the input port requests (mSA-II). Multicast requests get

granted multiple output ports. In the third and fourth stages, flits physically traverse

a crossbar switch (ST) and a link (LT). It is notable that out of all these actions,

only the last two actions (ST and LT) actually move the flits toward the destination.

Throughout the thesis, we will refer to this design (Figure 1-2) as a state-of-the-art

router microarchitecture or a comparison baseline after slight modifications required

for fair comparison.

30

Header

Generation

Input Buffer

VC1

64b

5ports X 64b

VC2

VC3

NIC

VC4

VC5

VC6

5b

N

Input Port (BW)

E

Credit Signals to Previous Routers

5b

31

Outport Request (VC1)

5b

S

Outport Request (VC2)

Outport Request (VC3)

Outport Request (VC4)

W

Outport Request (VC5)

64b 5X5 Crossbar

(ST)

Link

(LT)

Pipeline Stage 3

Pipeline Stage 4

Outport Request (VC6)

Round-robin circuit (mSA-I)

Output Port

(mSA-II)

VC allocation (VA)

5ports X 3b

Credit Signals

from Next Routers

Pipeline Stage 1

Pipeline Stage 2

Figure 1-2: Detailed router microarchitecture and pipeline of a packet-switched, input-buffered VC NoC.

1.2. Mesh Network-on-Chip (NoC)

Next Route

Computation

(NRC)

64b

Chapter 1. Introduction

1.3

Rethinking Router Microarchitecture

The previous section (as well as most existing NoC literatures) tried to explain a

NoC router microarchitecture by diving directly into the state-of-the-art design followed by description of individual components. This top-down approach is able to

provide a quick way to understand the packet-switched VC router microarchitecture,

but often makes it difficult to accurately analyze router overheads due to a significant gap between an ideal interconnect and the packet-switched NoC. Indeed, design

optimization starts with finding its overheads and recognizing if such overheads are

avoidable or not. To explicitly reveal the router overheads, this section explores the

bottom-up approach through the step-by-step router building process, rethinking the

state-of-the-art NoC router microarchitecture.

As mentioned earlier, the ideal interconnect would be a point-to-point link provided by full network connectivity that delivers the highest possible throughput at

the lowest possible latency and energy. Figure 1-3 shows such a point-to-point wire

between a source (SRC) and a destination (DST). It should be noted that even the

ideal incurs physical constraints like metal-wire delay and energy, and accordingly,

the first step towards designing low-power high performance NoCs should be the optimization of the metal-wire delay and energy. Trade-off wise, higher supply voltage

in link drivers (greater driving strength) enables shorter wire delay, but requires more

propagation energy. While a wider wire pitch reduces coupling capacitance between

wires (hence lower propagation delay and energy), it leads to lower wire density, resulting in poor bandwidth in the network. Metal-wire links comprise 17-39% of total

network power in mesh NoC chips [4, 5, 8], and form the unavoidable portion of network power as link power is a physical constraint. Furthermore, as wire performance

benefit from CMOS scaling does not keep up with gate performance benefit, link

power will increase in percentage relative to control and storage circuitry power as

process technology scales down [15, 16].

32

1.3. Rethinking Router Microarchitecture

Figure 1-3: Ideal point-to-point interconnect only through a metal wire.

Figure 1-4: Repeated interconnect for lower wire delay (starting point of wire sharing).

Figure 1-5: Input wire sharing through a demultiplexer.

Figure 1-6: Output wire sharing through a multiplexer.

33

Chapter 1. Introduction

Figure 1-7: Input and output wire sharing through a demultiplexer and a multiplexer.

Figure 1-8: Input and output wire sharing through a crossbar switch.

Figure 1-9: Efficient wire sharing with a SA logic and buffers.

34

1.3. Rethinking Router Microarchitecture

Figure 1-10: Packet-switched, input-buffered VC router microarchitecture.

When DST is too far from SRC, i.e. an interconnect wire is too long, intermediate

drivers in a long wire (known as repeaters) can significantly reduce the propagation

delay by converting the quadratic RC delay growth with the wire length into a linear

RC delay growth [17, 18]. If a wire is long enough, the extra delay and energy of

repeaters are easily offset by the long wire. Besides, repeaters offer a wire sharing

opportunity for free by decoupling a long wire into multiple wire segments. In other

words, the repeated interconnect shown in Figure 1-4 has 3 source and destination

pairs (SRC to a repeater, a repeater to DST and SRC to DST) while the point-topoint interconnect in Figure 1-3 has only one SRC and DST pair.

While point-to-point connection is always preferable between one SRC and DST

pair, full connectivity of all possible SRC and DST pairs is too expensive in terms of

global wiring area to be incorporated in manycore chips; building a fully-connected

NoC with higher node counts (e.g. 32 nodes) is practically impossible in existing

CMOS technology due to insufficient wiring [2]. Thus, wire sharing is inevitable for a

scalable on-chip communication fabric. Figure 1-5 shows input wire sharing through a

demultiplexer by which multiple destination nodes (DST1-5) share the wire segment

35

Chapter 1. Introduction

from SRC to the demultiplexer. Similarly, as shown in Figure 1-6, a multiplexer

enables output wire sharing where multiple source nodes (SRC1-5) share the tail

wire from the multiplexer to DST. The demultiplexer/multiplexer along with drivers

optimized for a single segmented wire can be viewed as the most primitive form of

NoCs in that wire sharing is the essence of NoCs.

We can also share both input and output wires by the combination of a demultiplexer and a multiplexer (Figure 1-7). This naive implementation, however, imposes

severe bandwidth loss since only one SRC and DST pair can communicate at a time.

A crossbar switch, which allows multiple SRCs to be connected to multiple DSTs,

can prevent such a bandwidth loss (Figure 1-8). The straightforward implementation

of the crossbar switch is to use redundant multiplexer arrays to provide all possible connections between multiple SRCs and DSTs [13]. Actually, this is the design

that most commercial synthesis CAD tools generate for crossbar switch functionality. While its static feature ensures stable operation, higher counts of SRCs and

DSTs cause substantial propagation delay and energy as compared to matrix crossbar switches whose transistor counts are much lower than the mux-based crossbar

switch [6]. On the other hand, the matrix crossbar switch requires careful circuit design on the matrix crosspoint switch which is typically implemented with pass gates,

transmission gates, or dynamic tri-state gates. This is because simple pass gates

and transmission gates do not work properly in an advanced CMOS process such as

silicon-on-insulator (SOI) technology and dynamic tri-state gates make their output

noise-sensitive. The Crossbar switch consumes 15-33% of the entire network power

in mesh NoC chips [4, 5, 8], and if wire sharing is inevitable for scalable NoCs then

this crossbar power consumption is also unavoidable.

For efficient wire sharing, a crossbar switch requires its allocation logic as shown

in Figure 1-9. In addition to the bandwidth improvement, such an allocation logic can

support QoS or packet/message fairness, depending on system requirements. While

the switch allocation logic contributes a negligible portion of overall NoC power, its

36

1.3. Rethinking Router Microarchitecture

computation delay can add significant packet latency. Trade-off wise, bandwidthoptimized allocation algorithms generally need more computation, thus resulting in

longer flit latency.

To further enhance wire sharing efficiency, a crossbar switch can incorporate

buffers to house flits when they cannot go forward right away to their destinations due

to contention. These buffers have a substantial impact on network bandwidth [19]

so that all existing NoC chips include buffers dedicated to their routers [4, 5, 8, 9,

10, 11, 12]. While flits can be buffered on the input ports or output ports, only an

input-buffered microarchitecture permits the single-ported memories that are more

power and area-efficient than multiple-port memories [13, 19]. For this reason, most

NoC router designs have buffers at the input ports, and as described in Figure 1-2, we

also selected the input-buffered router microarchitecture as a baseline in the thesis.

However, if the allocation rate of a crossbar switch is faster than the rate of output

wires (links in NoCs), output buffering allows more efficient wire sharing and higher

bandwidth, and hence, the output-buffered microarchitecture can be a better choice

for some systems. Router buffers consume 22-35% of total NoC power [4, 5, 8], and

add buffering delay to flit latency (1 clock cycle in general). Unlike links and a crossbar switch, the buffering power and delay are not unavoidable overheads. In fact,

minimizing buffer size and actual buffering counts at given target performance stands

at the center of NoC optimization.

Buffer allocation also has a huge impact on bandwidth of the packet-switched

NoC. If each input port allows only one buffer queue, head-of-line blocking can occur,

leading to poor link utilization. In other words, when a packet at the entrance of such

a single queue is blocked, it can stall other packets that are lined up behind the blocked

packet even if free buffers are available. Multiple buffer queues can resolve this headof-line blocking, but assigning several physical queues at each input port is expensive

in terms of area and energy [13]. Alternatively, we can split one physical queue into

multiple logically-separate queues. These logically-separate buffer queues can share

37

Chapter 1. Introduction

one physical channel (that’s why they are called virtual channels!), and hence, flits

can be interleaved from different packets. Similar to a crossbar switch, these virtual

channels (VCs) need their own allocation logic for efficient VC arbitration. Figure 110 shows the additional allocation logic for logically-separate buffers. Actually, this

figure design (a 5×5 crossbar switch along with its allocation logic, link drivers,

logically-separate input buffers and a VC allocation logic) is architecturally-identical

to the 2D mesh router design described in the previous section. Insights developed

through this step-by-step router building process from the ideal interconnect to the

packet-switched VC router will be the basis of our approaches towards the low-power

yet high-performance NoC designs.

1.4

Thesis Contributions and Overview

This thesis presents novel low-power NoC designs that depart from the traditional

trade-offs between network power and latency/bandwidth performance through circuit and microarchitecture co-design, then proves such design concepts on silicon

with a thorough analysis of the chip measurement results. To be specific, the thesis demonstrates three test chip designs: a 4×4 mesh NoC in Chapter 2, clockless

low-swing repeaters in Chapter 3 and a 3D through-silicon via (TSV) interconnect

in Chapter 4. The mesh NoC chip first optimizes the crossbar switch (Figure 1-8),

then co-designs the logic to minimize buffering (Figure 1-10). The second test chip

of clockless low-swing repeaters targets the repeated link (Figure 1-4) while the third

3D-IC chip seeks to develop the TSV point-to-point interconnect (Figure 1-3) whose

design constraints totally differ from the conventional 2D metal wires. An overview

of each chip prototype and corresponding chapter is as follows:

• 4×4 Mesh NoC Chip. Chapter 2 explores our first test chip of a mesh network

design for chip multiprocessors (CMPs) that aims to simultaneously optimize

energy-latency-throughput for unicasts, multicasts and broadcasts. We first

38

1.4. Thesis Contributions and Overview

define and analyze the theoretical limits of a mesh NoC in latency, throughput

and energy, then describe how we approach these limits through a combination

of microarchitecture and circuit techniques. Fabricated in 45nm SOI CMOS,

the 1.1V 1GHz NoC chip achieves 1-cycle router-and-link latency at each hop

and energy-efficient router-level multicast support, delivering 892Gb/s (87.1%

of the theoretical bandwidth limit) at 531.4mW for a mixed traffic of unicasts

and broadcasts. Armed with detailed measurement results, this chapter deeply

compares and analyzes the pros and cons of the proposed mesh NoC design:

(1) energy/performance improvement and timing/area penalties of the virtual

bypassed, multicast-optimized router design; (2) energy benefits, area overheads

and reduced reliability of the clocked low-swing datapath circuits; and (3) a

gap between simulated power estimation (ORION 2.0 [20]) and actual power

consumption. Here, I would like to acknowledge that the architectural design

of this test chip [6] was done by Tushar Krishna, a former PhD student at MIT.

• Clockless Low-Swing Repeaters Chip. Traffic on multiprocessor systemson-chip (MPSoCs) is highly dynamic, i.e. the traffic considerably varies depending on SoC applications. To efficiently support such dynamic traffic, reconfigurable NoCs on a flexible network topology like a mesh have been developed [21, 22, 23, 24, 25]. These networks pre-reserve (parts of) the route to

match application traffic by making unnecessary routers contention-free. If existing clocked low-swing circuits are applied to the pre-reserved routes, flits will

pay needless clocking energy and latency even at the contention-free nodes. To

prevent such wastage (hence maximize low-swing signaling benefits in the reconfigurable NoCs), Chapter 3 proposes two types of clockless low-swing repeaters,

self-resetting logic repeaters (SRLRs) and voltage-locked repeaters (VLRs), and

analyzes experimental results of the test chip fabricated in 45nm SOI CMOS.

Featured with variation-robust circuit techniques, the 0.8V 4.1Gb/s SRLRs enable single-ended low-swing pulses to be asynchronously repeated, and there-

39

Chapter 1. Introduction

fore, consume less energy than differential, clocked low-swing signaling. On the

other hand, the 1.0V 6.8Gb/s VLRs outperform energy-equivalent full-swing repeaters in terms of delay (35% reduction) and bandwidth (23% improvement),

enabling single-cycle multi-hop asynchronous link traversal for a single-cycle

reconfigurable NoC [1].

• 3D TSV Interconnect Chip. Many multi-threaded applications of CMPs

and MPSoCs require heavy off-die bandwidth that cannot be handled by existing off-chip I/Os. While three-dimensional integrated circuits (3D-ICs) offer

an appealing solution to such bandwidth-hungry manycore chips, current 3DIC fabrication technologies inevitably require redundant through-silicon vias

(TSVs) for reliable 3D vertical signaling, leading to significant power and area

overheads. To alleviate these 3D signaling overheads (hence incorporate TSVs

as 3D-IC NoC links within tight power and area budget), Chapter 4 proposes

and demonstrates the concept of simultaneously bi-directional (SBD) TSV signaling that can send and receive data at the same time through a single TSV.

The proposed SBD interconnect enables area and power-efficient, variationrobust 3D signaling with a relatively small bandwidth loss (less than 13%).

Implemented with 28nm Low-Power CMOS process and MediaTek TSV technology, our SBD TSV interconnect achieves 10.3-31.1% lower energy and 34.4% less

area than equivalent two uni-directional TSVs at 9.1Gb/s/TSV bi-directional

data rate (i.e. 4.55GHz clock frequency) at 1.05V.

40

1.4. Thesis Contributions and Overview

41

Chapter 1. Introduction

42

2

Towards the Theoretical Limits of a Mesh NoC

This chapter first derives the theoretical mesh NoC bounds, followed by an analysis of

a power and performance gap with existing mesh NoC chips. It then presents a chip

prototype of the proposed mesh NoC which tries to eliminate the gap, thus approaching

the theoretical limits.

2.1

Theoretical Mesh NoC Limits

A mesh topology by itself imposes theoretical limits on latency, throughput and

energy (i.e. minimum latency and energy, and maximum throughput). Chapter 2

starts with the derivation of these theoretical bounds of a k × k mesh NoC for two

traffic types, unicast and broadcast traffic. In our analysis, each network interface

circuit (NIC) injects flits into the network according to a Bernoulli process of rate

R, to a random, uniformly distributed destination for unicasts; and from a random,

uniformly distributed source to all nodes for broadcasts. All derived bounds are for

a complete action: from initiation at the source NIC, till the flit is received at all

destination NICs. We also make three NoC-level assumptions for our derivation:

1. Perfect Routing. A router would route all packets with minimal hop-counts,

balancing injected packets (termed channel load in our analysis) across multiple

routes perfectly, thereby keeping the load on all links optimally balanced.

43

Chapter 2. Towards the Theoretical Limits of a Mesh NoC

k

k-j

Furthest destination

S

Source (i, j)

k-i

Figure 2-1: Latency calculation example for broadcast traffic on a k×k mesh network.

2. Perfect Flow Control. A router maintains maximum utilization of the links,

i.e. a link is never left idle when there is traffic routed across it.

3. Perfect Router Microarchitecture. All flits only incur the delay and energy of the datapath (ST and LT). In other words, a router arbitrates between

competing flits; performs crossbar and link traversal all in a single cycle; and

do not expend extraneous energy for buffering and control.

Based on these assumptions, we derive the theoretical limits for unicast and broadcast traffic. For unicasts, we analyze the theoretical limits for latency and throughput

using the same technique as in [13]. We then derive the energy limit by multiplying

44

2.2. Related Work: Existing Mesh NoC Chips

hop count with crossbar and link energy costs. For broadcast traffic, to the best of

our knowledge, no prior theoretical analysis exists. Here, we define the time till a flit

is received by all destination NICs as equivalent to when this flit is received by the

furthest NIC relative to the source NIC (Figuire 2-1). Hence, we derive the theoretical latency limit for received packets by averaging the hop delay from each source

NIC to its furthest destination NIC. Throughput wise, we obtain the theoretical limit

by analyzing the channel load across the ejection links and bisection links [13], and

observe that the maximum throughput for broadcast traffic is limited by the ejection

links. This differs from unicast traffic where throughput is always limited by the

bisection links. As for the theoretical energy limit, intuitively, due to the nature of

broadcasting, a broadcast flit needs to visit all k 2 routers in the network and traverse

k 2 crossbars and links connecting them. Therefore, the energy limit grows quadratically with the number of routers in the network. Table 2.1 summarizes our derivation

results.

2.2

Related Work: Existing Mesh NoC Chips

There have been chip prototypes that incorporate mesh NoCs [4, 5, 8, 9, 10,

11, 12] or other heterogeneous NoCs [26, 27, 28] as their on-chip communication

fabric. The prototypes range from full manycore processors to stand-alone NoCs.

As heterogeneous NoC chips [26, 27, 28] have irregular topologies which make it

difficult to characterize them against the theoretical mesh limits, we focus here on the

manycore chips with mesh networks in our related work investigation. In particular,

three chip prototypes were selected for comparison, each differing significantly with

respect to targeted design goals and optimizations: Intel TeraFLOPS which is the

precursor of the Intel IA-32 NoC, Tilera TILE64 which is the successor of the MIT

Raw, and SWIFT, a NoC with low-swing signaling. These three chips and their

corresponding NoC architectures are described in detail as follows:

45

Chapter 2. Towards the Theoretical Limits of a Mesh NoC

• Tilera TILE64 [9] is a multiprocessor consisting of 64 tiles interconnected by

five 2D mesh networks, where each tile contains a CPU, cache and a router,

fabricated on the TSMC 90nm process and running at a speed of 700 to 866

MHz. Four of the five networks are dynamically routed, each servicing a different type of traffic: user dynamic network (UDN) for user-level messages,

I/O dynamic network (IDN) for I/O traffic, memory dynamic network (MDN)

for traffic to/from the memory controllers, and tile dynamic network (TDN)

for cache-to-cache transfers. The dynamic networks are packetized, wormhole

routed, with a one cycle pipeline for straight-through traffic and two cycles for

turning traffic. The static network is software scheduled, and has a single-cycle

pipeline.

• Intel TeraFLOPS [5] has a more complex NoC architecture, but the cores are

much simpler than a standard RISC processor. Since simpler cores are more area

and energy-efficient than larger ones, more functional units can be integrated

within a single chip’s area and power budget. TeraFLOPS is a demonstration

of the possibility of including an on chip interconnect, operating at 5 GHz, and

achieving performance in excess of TeraFLOPS while maintaining a power usage

of less than 100W. TeraFLOPS NoC has a five-port, two-lane, five-pipelinestage router with a double pumped crossbar used to interconnect the tiles in

a 2D mesh network. Each input port is connected to two 16 entry deep FIFO

buffers, one for each lane. A single crossbar for both lanes is double pumped in

the fourth pipeline stage using dual-edge triggered flip-flops, allowing the switch

to transfer data at both edges of the clock signal.

• SWIFT [29] is a 2×2 standalone NoC research chip demonstrating the practicality of implementing token flow control [30] and low swing crossbar switches

and links. The buffer-bypassed traversal of flits through a reduce-swing datapath is demonstrated to perform at 400 MHz and obtain latency and power

reductions of approximately 40 percent each. The token flow control microar-

46

2.2. Related Work: Existing Mesh NoC Chips

chitecture pre-allocates buffers and links in the network by using tokens. Many

flits are then able to bypass buffering, improving link utilization and reducing the buffer turnaround time. Dual voltage supply differential reduced-swing

drivers and sense-amplifier receivers sustain the low-swing signaling necessary

to reduce the dynamic power consumption.

We calculated zero-load latency and channel load of these networks for both

unicast-only and broadcast-only traffic. Zero-load latency can be obtained by multiplying the average hop-count by the number of pipeline stages to traverse a hop, with

serialization latency added on to model pipelining of all flits. In terms of throughput,

we computed channel load based on a flit injection rate per core of R, following the

methodology of [13]. The results are shown in the Table 2.2.

It is noted in this table that our proposed NoC, which will be described in the

following section, optimizes for broadcast traffic and incurs much lower zero-load latency and channel load compared to all other networks. TILE64 attempts to optimize

for all three metrics by utilizing independent simple networks for different message

types. The simple router design, with no virtual channels, improves unicast zero-load

latency but broadcast traffic latency is poor as its lack of multicast support forces

the source NIC to duplicate k 2 − 1 copies of a broadcast flit and send a copy to every

destination NIC. This increases channel load by k 2 − 1 times, causing contention at

all routers along the shared route, making it impossible to meet the single-cycle per

hop. TILE64’s static partitioning of traffic across 5 networks may also lead to poor

throughput when exercised with realistic uniform traffic. Similar effect on broadcast

latency and channel load is observed for the TeraFLOPS and SWIFT NoCs as none

of these chip prototypes have multicast support. The SWIFT NoC with a single-cycle

pipeline for unicasts performs better on zero-load latency, albeit at a lower operating

frequency. The TeraFLOPS NoC has poor zero-load latency in terms of cycles due

to a 5-stage pipeline, which is aggravated with broadcasts.

47

Table 2.1: Theoretical limits of a k×k mesh NoC for unicast and broadcast traffic.

Metric

Unicasts

(one-to-one multicasts)

2(k + 1)/3

Average Hop Count (Haverage )

k×R/4

R

2(k + 1)/3

R, for k <= 4

k×R/4, for k > 4

2(k + 1)/3×Exbar

+ Exbar

+ 2(k + 1)/3×Elink

k 2 ×Exbar

+ (k 2 − 1)×Elink

48

Table 2.2: Comparison of mesh NoC chip prototypes.

Clock frequency

Power supply

Power consumption

Latency Metrics

Delay per hop

Zero-load latency

(cycles)

Throughput Metrics

Channel width

Bisection bandwidth

Channel load

(R:injection rate/core)

Intel

TeraFLOPS [5]

8×10, 65nm

5GHz

1.1-1.2V

97W

1ns

30 (unicast)

120.5

(broadcast)

39b

1560Gb/s

64R (unicast)

4096R

(broadcast)

Tilera TILE64 [31]

SWIFT [29]

5 8×8, 90nm

2×2, 90nm

750MHz

225MHz

1.0V

1.2V

15-22W

116.5mW

Modeled as 8×8 networks

1.3ns

8.9-17.8ns

9 (unicast)

12 (unicast)

77.5 (broadcast)

86 (broadcast)

Modeled as 8×8 networks

5×32b

64b

937.5Gb/s

112.5Gb/s

64R (unicast)

64R (unicast)

4096R (broadcast)

4096R (broadcast)

Our work

4×4, 45nm SOI

1GHz

1.1V

427.3mW

4×4 network

1-3ns

6 (unicast)

3.3 (unicast)

11.5 (broadcast)

5.5 (broadcast)

64b

512Gb/s

64R (unicast)

4×4 network

64b

256Gb/s

16R (unicast)

64R (broadcast)

16R (broadcast)

Chapter 2. Towards the Theoretical Limits of a Mesh NoC

Channel Load on each bisection link (Lbisection )

Channel Load on each ejection link (Lejection )

Theoretical Latency Limit

given by Haverage

Theoretical Throughput Limit

given by max{Lbisection , Lejection }

Theoretical Energy Limit

Exbar : energy of crossbar traversal

Elink : energy of link traversal

Broadcasts

(one-to-all multicasts)

(3k − 1)/2, for k even

(k − 1)(3k + 1)/2k, for k odd

k 2 ×R/4

k 2 ×R

(3k − 1)/2, for k even

(k − 1)(3k + 1)/2k, for k odd

k2 × R

2.3. Chip Design and Fabrication

2.3

Chip Design and Fabrication

Our mesh NoC chip design starts with the state-of-the-art router microarchitecture

(Figure 1-2). We then add features pushing latency towards the theoretical limit of

a single cycle per hop, throughput towards the theoretical limit of maximum channel

load and energy towards the theoretical limit of just datapath traversal. In the

fabricated network, all routers are connected to network interface circuits (NICs)

to generate and receive packets. For realistic traffic, we separately model request

and response messages to reflect that most manycore chips today use shared memory

architecture and rely on the request and response messages between nodes to maintain

data coherence. To avoid message-level deadlocks in such cache-coherent manycore

processors, each input port has two message classes (MCs), request and response.

The request message class contains 4 VCs, each of which is 1-flit deep, while the

response message class contains 2 VCs, each of which is 3-flit deep. All flits follow

an XY dimension ordered routing (DOR) and a broadcast flit is replicated only when

#4

#3

#3

#3

#2

#4

#3

#2

#5

#4

#3

#4

Flit Size

64bits

Request

Packet Size

1 flit

Response

Packet Size

5 flits

Microarchitecture 6VCs over 2MCs

#2

#2

#0

#1

#1

#3

#2

#2

#2

#2

#3

#2

#1

#1

#3

#3

#2

#4

#3

No-load Routerand-link Latency

1 cycle

Operating

Frequency

1GHz

Power Supply

Voltage

1.1V

Technology

45nm SOI CMOS

Figure 2-2: Broadcast example and overview of the fabricated 4×4 mesh NoC.

49

Chapter 2. Towards the Theoretical Limits of a Mesh NoC

1mm link

2mm link

Tri-state

RS D

Router #1

NORTH

Router #5

Router #3

Router #2

320um

540um

590um

X B AR

Tri-state

NIC

RSD

EAST

Router #8

WEST

XBAR

Router #4

SOUTH

260um

Router #9

Router #10

Router #11

Router #12

Router #13

Router #14

Router #15

Router #16

Figure 2-3: Die photo and design layout of the 4×4 mesh NoC and stand-alone lowswing crossbar switch connected to longer links (1mm and 2mm wires).

the XY DOR requires different output ports to minimize the network traffic (XY-tree

DOR). Figure 2-2 describes such a broadcast example with overview of our fabricated

4×4 mesh NoC. As shown in the die photo overlaid with its design layout (Figure 23), an additional crossbar switch is separately laid out with longer links, 1mm and

2mm wires, to explore higher data rate performance of our low-swing crossbar switch

(clock frequency of the overall network is limited by the synthesized router logic).

Following subsections will completely describe the proposed mesh NoC chip design.

50

2.3. Chip Design and Fabrication

2.3.1

Towards Theoretical Latency Limits

We first push the state-of-the-art design towards the latency bounds by adding two

key features: a virtual bypassing microarchitecture to hide delays due to buffering

and arbitration [6, 30, 32], and low-swing datapath circuits based on linear-mode

drive transistors to achieve single cycle ST+LT without lowering clock frequency.

• Single-stage pipeline with lookaheads. In pipeline stage 2 of the state-ofthe-art design (Figure 1-2), we add and generate 15b lookahead signals from the

results of NRC and mSA-II, and send them to the next router. The lookaheads

try to pre-allocate the crossbar switch ahead of the actual flit, thus hiding

mSA-II from the router delay. The lookahead takes priority over requests from

buffered flits at the next router, and directly enters mSA-II. If the lookahead

wins an output port, this pre-allocation allows the following flit to bypass the

first two pipeline stages and go into the third stage directly, reducing the router

pipeline depth from 4 to 2. It is notable that our active pre-allocation by

lookaheads enables incoming flits to bypass routers at all loads, in contrast to

a plain approach of bypassing only at low-loads when the input queues are

empty [33, 34, 35].

• Single-cycle ST+LT with low-swing circuits. We apply the low-swing signaling technique based on linear-mode drive transistors, which can reduce the

charging/discharging delay and dynamic energy when driving capacitive parasitics [36], to the NoC datapath. As will be described later in Section 2.3.3,

the proposed low-swing circuits obtain higher current driving ability (i.e. lower

linear drive resistance) even at small Vds than the reduced-swing signaling generated by simply lowering supply voltage, and hence, our low-swing datapath enables single-cycle ST+LT at higher clock frequency. Our chip prototype

demonstrates that the proposed low-swing circuits enable up to 5.4GHz singlecycle ST+LT (more details in Section 2.4).

51

Chapter 2. Towards the Theoretical Limits of a Mesh NoC

These two optimizations achieve a single-cycle-per-hop delay for unicasts and multicasts, exactly matching the theoretical latency limits. The caveat is that in case

of contention for the same output port from multiple lookaheads, one of them will

have to be buffered and then forced to go through the 3-stage pipeline. In addition,

critical path delay is stretched, which will be analyzed in Section 2.4.2.

2.3.2

Towards Theoretical Throughput Limits

Next, we take two steps towards the throughput bounds for both unicasts and

broadcasts: router-level multicast support for bandwidth sharing and single-cycleper-hop latency for fast buffer reuse.

• Multicast support inside routers. We extend the multicast capability of

the state-of-the-art design into our lookahead-based microarchitecture by letting

lookaheads perform the multicast switch allocation. This scheme enables one

multicast/broadcast flit to be sent from the source NIC, and get routed to

all other routers in the network via a tree. The multicast capability allows

a broadcast flit to share bandwidth till it does not require an explicit forking

into different directions. This dramatically reduces contention compared to the

textbook router design [13] where multiple flits would have to be sent as unicasts

which are guaranteed to create contention at along the shared routes. We use

a dimension ordered XY-tree routing in our design as it is deadlock free, and

simplifies the routing algorithm.

• Single-cycle-per-hop latency. The number of buffers/VCs required at every

input port to sustain a particular throughput depends upon the buffer/VC

turnaround time, i.e. the number of cycles for which the buffer/VC is occupied.

This is where our optimizations for latency in Section 2.3.1 come in handy here

since they reduce the pipeline depth, thus reducing buffer turnaround time,

thereby increasing throughput given the same number of buffers. For our singlecycle pipeline, the turnaround time for buffers/VCs is 3: one cycle for ST+LT

52

2.3. Chip Design and Fabrication

to the downstream router, one cycle for the free VC/buffer signal to return

from the downtsream router (if the flit successfully bypassed), and one cycle

for it to be processed and ready to be used for a new flit. We thus choose

4 VCs in the request message class, each 1-flit deep (since requests packets

in our design are 1-flit wide) to satisfy VC turnaround time and sustain high

throughput for broadcasts. We chose 2 VCs in our response message class, each

3-flit deep, for the 5-flit response packets. This number was chosen to be less

than the turnaround time to shorten the critical path, and reduce the total

buffers (which increase power consumption). We thus chose a total of 6 VCs

per port, with a total of 10 buffers.

2.3.3

Towards Theoretical Energy Limits

Section 2.1 reveals a significant energy gap between the state-of-the-art router

energy and the theoretical energy limit (which is just clocking and datapath energy,

Exbar and Elink ). Such a gap is due to buffering energy (Ebuf f ), arbitration logic energy

(Earb ) and silicon leakage energy (Elkg ). Conventionally, these energy overheads are

traded off against latency and throughput as follows: Fewer buffers reduce Ebuf f and

Elkg , but stretch latency due to contention and lower throughput. Or, simple routers

like wormhole routers [13] reduce Earb and Elkg , and increase operating frequency f ,

but these come at the expense of poorer latency and throughput.

Our proposed NoC first includes multicast support so even broadcasts and multicasts can approach the theoretical energy limit. Then, it incorporates two new

features that permits different tradeoffs of latency, throughput and energy. First, our

multicast virtual bypassing reduces Ebuf f , while improving both latency and throughput. The hidden cost lies in increased Earb and decreased f . As will be shown in

Section 2.4.1, the savings in Ebuf f outweigh the Earb overheads, and operating frequency can still be in GHz. Second, our chip employs low-swing signaling to reduce

dynamic energy in the datapath (Exbar and Elink ) which is unavoidable and part

53

Chapter 2. Towards the Theoretical Limits of a Mesh NoC

Figure 2-4: 64bits 5×5 tri-state RSD-based matrix crossbar switch and link circuitry.

of the theoretical energy limit. Our low-swing circuits based on linear-mode drive

transistors provides an opportunity to break the conventional trade-offs that achieve

dynamic energy savings at the cost of latency and throughput penalties. Indeed, our

low-swing datapath optimizes both energy and latency. Its downsides lie in its area

overheads and reduced process variation immunity.

Figure 2-4 shows the circuit implementation of the low-swing crossbar switch

directly connected to links with tri-state reduced-swing drivers (RSDs). This circuit

54

2.3. Chip Design and Fabrication

design enables low-swing signaling in crossbar vertical wires and link wires. The tristate RSD disconnects horizontal and vertical wires and only drives the corresponding

vertical wire and link, thereby providing energy-efficient multicasting capability. With

an additional supply voltage (LVDD), the 4-PMOS stacked RSD design generates

more reliable low-swing signaling in the presence of wire capacitance and resistance

variation than equalized interconnects [37, 38, 39, 40] where low-swing signaling is

obtained by wire channel attenuation. A delay cell aligns an input signal (which

drives only a 1b crossbar) to an enable signal (which drives all of 64 1bit crossbars).

It reduces mismatch between charging and discharging time, thus decreasing intersymbol interference (ISI). The 64bits links are designed with 0.15um-width 0.30umspace fully shielded differential wires, to eliminate noise coupling of crosstalk effects

and supply voltage variation.

Figure 2-5 shows the detailed router microarchitecture and pipeline of our proposed mesh NoC that incorporates virtual bypassing, low-swing signaling datapath

and router-level multicast support. The following section will closely explore not

only its performance and energy benefits but also the concomitant costs such as area

overhead, stretched critical path, reduced noise margin.

55

Chapter 2. Towards the Theoretical Limits of a Mesh NoC

56

Figure 2-5: Proposed router microarchitecture and pipeline.

2.4. Evaluation

2.4

Evaluation

We first evaluate the measured energy-latency-throughput of our fabricated NoC

against that of the baseline design and the theoretical mesh limits defined in Section 2.1. Armed with our chip measurements, we then delve into three specific case

studies on virtual bypassing; low-swing signaling; and power modeling and estimation

to dissect our design choices.

2.4.1

Latency, Throughput and Energy

We measured average packet latency of our NoC as a function of packet injection

rate, with two different traffic patterns: mixed traffic (50% broadcast request, 25%

unicast request and 25% unicast response messages) and broadcast-only traffic (100%

broadcast request messages), at 1GHz operating frequency. Figure 2-6 and Figure 2-7

show the results along with the baseline performance and theoretical mesh bounds.

Here, we chose a more aggressive baseline that has single-cycle ST+LT instead of separate ST and LT stages described in Section 1.2. Since even the full-swing baseline

can support single-cycle ST+LT at 1GHz, this baseline is a fairer model of an equivalent unicast full-swing NoC. Except for the the single-cycle ST+LT, the baseline used

in this section is identical to Figure 1-2. The theoretical latency limits (cycles/packet)

include two extra cycles for NIC-to-router and router-to-NIC traversals which are indispensable since traffic injects and ejects through the NICs. Theoretical throughput

limits are calculated based on received flits, then converted into Gb/s to factor in the

1GHz clock frequency and 64-bit flit size (16×64b×1/1GHz=1024Gb/s). Simulation

results were obtained from pre-layout synthesis with sufficient simulation cycles (104

cycles) to make scan-chain warmup (128 cycles) negligible.

For latency, our design enables 48.7% (mixed traffic) and 55.1% (broadcast-only)

reductions before the network saturates as compared to the baseline. To enable

precise comparisons, we define the saturation point as the injection rate at which NoC

57

Chapter 2. Towards the Theoretical Limits of a Mesh NoC

Figure 2-6: Network performance evaluation with mixed traffic at 1GHz.

latency reaches 3 times the average no-load latency; most multi-threaded applications

run within this range. The low-load latency gap from the theoretical latency limit is

5.7 (6.3) cycles for mixed (broadcast) traffic, i.e. only 1.03 (1.14) cycles of contention

latency per hop for mixed (broadcast) traffic. This can be further improved to 0.04

(0.05) cycles of contention latency per hop (obtained through RTL simulations) by

removing the artifact in our chip whereby all NICS had identical pseudo-random

generators that caused contention which lowers the amount of bypassing even at low

injection rates.

Throughput wise, the fabricated NoC approaches the theoretical limits: 87%

(mixed traffic) and 91% (broadcast-only) of the theoretical throughput limits. In

58

2.4. Evaluation

Figure 2-7: Network performance evaluation with broadcast-only traffic at 1GHz.

addition, our NoC design has 2.1x (mixed traffic) and 2.2x (broadcast-only) higher