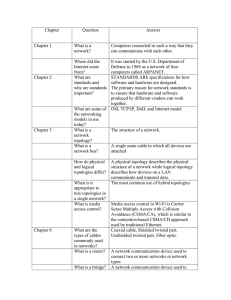

Chia-Hsin Chen MAR LIBRARIES

advertisement