Document 11206959

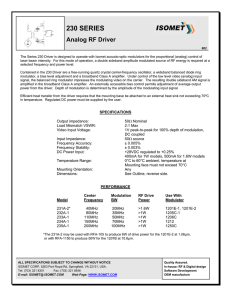

advertisement