Lab 5 - EE-313 MULTIPLEXERS

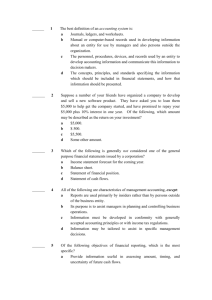

advertisement

Lab 5 - EE-313 MULTIPLEXERS Rev 02/21/2013 I. Purpose: A. Reinforce the skill necessary to implement a functional logic design. B. Introduce ENTITY instantiation and use of a VHDL entity as the top level entity. II. Equipment: A. Computer with Altera Software and web access B. Altera DE2 Board with power supply and USB cable III. Pre-lab assignment: A. Complete Lab 4 IV. Description and Notes In this project, you will create a multiplexer and de-multiplexer. You will then use a top level entity designed using VHDL to instantiate the multiplexer and de-multiplexer so that you can demonstrate their proper operation. The project entities must meet the following design requirements. Multiplexer Project Design Requirements PROJECT NAME: yourlastname_lab05 ENTITY NAME yourlastname_lab05a FUNCTION Instantiate the multiplexer you designed and connect it to the designated inputs and outputs. NAME TYPE SIZE STD_LOGIC_VECTOR 18 bits INPUT sw key STD_LOGIC_VECTOR 4 bits STD_LOGIC_VECTOR 9 bits OUTPUTS ledg NOTES • Switches 1 and 0 shall control the multiplexer. • The data into the multiplexer shall come from keys 0 through 3. • The output of the multiplexer shall be displayed on green led 0. ENTITY NAME yourlastname_lab05b FUNCTION Instantiate the de-multiplexer you designed and connect it to the designated inputs and outputs. NAME TYPE SIZE STD_LOGIC_VECTOR 18 bits INPUT sw key STD_LOGIC_VECTOR 4 bits STD_LOGIC_VECTOR 9 bits OUTPUTS ledg NOTES • Switches 1 and 0 shall control the de-multiplexer. • The data into the de-multiplexer shall come from keys 0. • The output of the de-multiplexer shall be displayed on green leds 3 through 0. Lab 5 - EE-313 MULTIPLEXERS Rev 02/21/2013 ENTITY NAME yourlastname_mux FUNCTION Operate as a 4 input 1 bit multiplexer with Active HIGH control. NAME TYPE SIZE STD_LOGIC_VECTOR 2 bits INPUT s d STD_LOGIC_VECTOR 4 bits STD_LOGIC 1 bit OUTPUTS y ENTITY NAME yourlastname_dmux FUNCTION Operate as a 4 output 1 bit de-multiplexer with Active HIGH control. NAME TYPE SIZE STD_LOGIC_VECTOR 2 bits INPUT s x STD_LOGIC 1 bit STD_LOGIC_VECTOR 4 bits OUTPUTS d Instantiation In a block diagram file, an entity is instantiated by creating a symbol for it and wiring the symbol in the schematic. In VHDL, an entity is instantiated using the ENTITY keyword. The sample code below illustrates how this is done. Figure 1 – Sample Code • • • • • • u1 is the name to be assigned to the specific instantiation of the de-multiplexer. If you were to have 3 instantiations, they could be called u1, u2, and u3. The specific name does not matter as long as it is unique and meets the naming conventions of VHDL. entity is the keyword that begins the instantiation. work.schultz_dmux(dataflow) tells the compiler to use the dataflow architecture of the schultz_dmux entity from the current project. port map begins the section that maps signals from the current entity which is using the de-multiplexer to the de-multiplexer. The => operator connects the instantiated entities inputs and outputs to signals of the entity which is using it. (ie. the input port s of the de-multiplexer is connected to bits 1 and 0 of the signal sw). NOTE that this is different than the <= operator. ); terminates the port map section of the entity statement. V. Lab 5 - EE-313 MULTIPLEXERS Lab Procedure and Questions: Rev 02/21/2013 A. Create a new project that implement the multiplexer and demultiplexer entities in VHDL. HINT: The multiplexer can be implemented using a single WITH/SELECT/WHEN statement while the de-multiplexer will require four WITH/SELECT/WHEN statements. B. Create a new top-level entity yourlastname_lab05a in accordance with the design requirements. NOTE: The architecture section of the file shall instantiate the multiplexer of in a manner similar to the example shown above. C. Make yourlastname_lab05a.vhd your top level entity by right clicking it in the Project Navigator->Files tab and selecting Set as Top-Level Entity. D. Assign pins by importing the pin assignment file (method 2), compile and debug your project. Once the project compiles successfully, program the Altera board and demonstrate proper operation to the instructor. E. Repeat steps B-D for the de-multiplexer yourlastname_lab05b. NOTE: It is not necessary to create a new project provided you set the top level entity to be yourlastname_lab05b.vhd F. Include printouts of your VHDL code in your lab notebook. G. Questions 1. What questions did you ask the instructor while performing this lab? 2. What were the answers to the questions asked? 3. How could you use your multiplexer to implement the following logic function? 𝑍 = 𝐴𝐵 + 𝐴𝐵� + 𝐴̅𝐵�