Serial: A digital signal representation that uses one line... information. The binary logic states are transmitted 1 bit at...

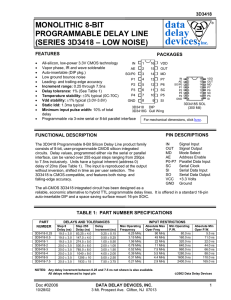

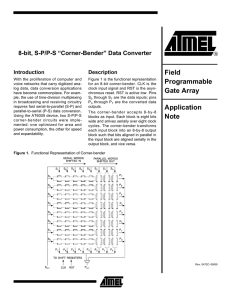

advertisement

Serial: A digital signal representation that uses one line or channel to transmit binary information. The binary logic states are transmitted 1 bit at a time, with the LSB first. Surface-Mount Device: A newer style of integrated circuit, soldered directly to the surface of a printed-circuit board. They are much smaller and lighter than the equivalent logic constructed in the DIP through-hole-style logic. Timing Diagram: A diagram used to display the precise relationship between two or more digital waveforms as they vary relative to time. Totem Pole: The term used to describe the output stage of most TTL integrated circuits. The totem-pole stage consists of one transistor in series with another, configured in such a way that when one transistor is saturated, the other is cut off. Transistor: A semiconductor device that can be used as an electronic switch in digital circuitry. By applying an appropriate voltage at the base, the collectorto-emitter junction will act like an open or a shorted switch. TTL: Transistor-transistor logic. The most common integrated circuit used in digital electronics today. A large family of different TTL integrated circuits is used to perform all the logic functions necessary in a complete digital system. Problems Sections 2-1 and 2-2 2-1. Determine the period of a clock waveform whose frequency is (c) 4.27 MHz (d) 17 MHz (a) 2 MHz (b) 500kHz Determine the frequency of a clock waveform whose period is (e) 2ps (f) 100 ps (g) 0.75 ms (h) 1.5ps Sections 2-3 and 2-4 2-2. Sketch the serial and parallel representations (similar to Figure 2-10) of the following numbers, and calculate how long they will take to transmit (clock frequency = 2 MHz). (b) A3C 16 (a) 45B 16 2-3. (a) How long will it take to transmit the number 33 10 in serial if the clock frequency is 3.7 MHz? (Transmit the number as an 8-bit binary number.) (b) Is the serial line HIGH or LOW at 1.2lps? 2-4. (a) How long will it take to transmit the three ASCII-coded characters $14 in 8-bit parallel if the clock frequency is 8 MHz? (b) Repeat for $78.18 at 4.17 MHz. PROBLEMS 53 Cpl~ Sketch the serial data on a single line relative to the clock reference. - ~ S 0 I l I 0 ;:, : o I Sketch the same/ data in parallel p by using several~ """ 0 1 \'' 0 23 0 Figure 2-9 tP 1 1 7 = 5 MHz = 0 ·2 JlS = =4 !serial !parallel = 1 X 0.2 JlS = 0.8 JlS X 0.2 JlS = 0.2 JlS EXAMPLE 2-6 Sketch the serial and parallel representations (least significant digit first) of the hexadecimal number 4A. (Assume a 4-bit parallel system and a clock frequency of 4kHz.) Also, what is the state (1 or 0) of the serial line 1.2 ms into the transmission? Solution: 4A 16 = 0 1 0 0 1 0 1 02 . tP = 1 1 7 = 4 kHz = 0.25 ms Therefore, the increment of time at each falling edge increases by 0.25 ms. Because each period is 0.25 ms, 1.2 ms will occur within the 0 period of the number 4, which, on the So line, is a 0 logic state (see Figure 2-10). Cp I 0 o.o So 0.25 0.50 0.75 1.0 1.25 1.50 1.75 2.0 (Time, ms) 1 0 Figure 2-10 34