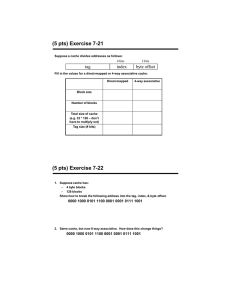

(5 pts) Exercise 7-21 tag index byte offset

advertisement

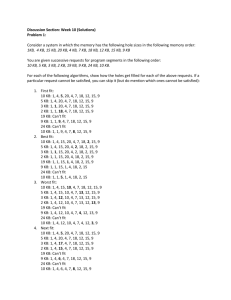

(5 pts) Exercise 7-21 Suppose a cache divides addresses as follows: 4 bits tag 3 bits index byte offset Fill in the values for a direct-mapped or 4-way associative cache: Direct-mapped 4-way associative Block size 2^3 = 8 b 2^3 = 8 b 2^4 = 16 4*2^4 = 64 Number of blocks Total size of cache (e.g. 32 * 128 – don’t have to multiply out) 8*16 8*64 Tag size (# bits) 32-7=25 32-7=25 (5 pts) Exercise 7-22 2 bits for byte offset 1. Suppose cache has: 7 bits for index – 4 byte blocks – 128 blocks Show how to break the following address into the tag, index, & byte offset. 0000 1000 0101 1100 0001 0001 0111 1001 23 (tag) 7 (index) 2 (byte offset) 2. Same cache, but now 8-way associative. How does this change things? 0000 1000 0101 1100 0001 0001 0111 1001 8-way only 128/8 = 16 sets (for index) 26 (tag) 4 (index) 2 (byte offset) (5 pts) Exercise 7-23 • Given a cache that is: 32/4 = 8 sets (3 bits) – 4-way associative 4 bits for byte offset – 32 blocks – 16 byte block size What is the cache index and byte offset (the actual values, not their size) for the following address: 0x3ab12395 Index = 1 Offset = 5 Cache index = Byte offset = And this one: 0x70ff1213 Index = 1 Offset = 3 Cache index = Byte offset = Do these addresses conflict in the cache? Sort of – same index, but have associativity. Note that having different offsets does NOT help avoid a conflict – each block has only one tag, so all data in a block must be from that tag. (10 pts) Exercise 7-26 Suppose a 32-bit address is divided up as follows for caching: 6 bits – byte offset 5 bits – index 21 bits – tag Fill in the following table for the two given types of caches Direct-mapped 2-way associative Block size 26 = 64 bytes 26 = 64 bytes Number of blocks #sets = #blocks = 25 = 32 #sets = 25 = 32 # blocks = #sets*assoc = 32 * 2 = 64 32 blocks * (64 bytes/block) = 2048 bytes = 2K 64 blocks * (64 bytes/block) = 4096 bytes = 4K Total cache size (10 pts) Exercise 7-27 Suppose a direct-mapped cache has 16 byte blocks and a total of 128 blocks (N=128). The machine has 64 bit addresses. 1. How many address bits are used for the byte offset? 16 byte blocks need 4 bits for byte offset (24 = 16) 2. How many address bits are used for the index? 128 blocks 128 sets (direct mapped) need 7 bits for index (27 = 128) 3. How many address bits are used for the tag? 64 bits – 4 – 7 = 53 bits for tag Now suppose the cache is 4-way set associative. Answer again: 1. How many address bits are used for the byte offset? 16 byte blocks need 4 bits for byte offset (24 = 16) 2. How many address bits are used for the index? # sets = 128 blocks / 4 blocks/set = 32 sets need 5 bits for index (25 = 32) 3. How many address bits are used for the tag? 64 bits – 4 – 5 = 55 bits for tag (5 pts) Exercise 7-31 • • Given system with – 20 bit virtual addresses – 16 bit physical addresses – 512 byte page sizes How to split a virtual address? Virtual page # • Page offset What will the physical address look like? Physical page # • 11 bits 7 bits Page offset 9 bits 28 = 256 8 bit page offset 9 bits How many entries in the page table? 211 (all possible virtual page #’s) (5 pts) Exercise 7-32 (new problem – not related to 7-31) Page Table Translate the following addresses: 1. B004890 7590 890 2. B002123 3. B006001 On disk F4C0 001 Valid? Physical Page or Disk Block # B000 1 B004 B001 1 A120 B002 0 AB00 B003 0 8003 B004 1 7590 B005 1 5800 B006 1 F4C0 … (5 pts) Exercise 7-33 Page Table Given the fragment of a page table on the right, answer the following questions assuming a page size of 1024 bytes 10 bits (based on page size) 1. What is the virtual address size (# bits) 16 bits (VPN, from examining table) + 10 (offset) = 26 bits 2. What is the physical address size (# bits) 8 bits (PPN, from examining table) + 10 (offset) = 18 bits Valid? Physical Page # B000 1 B0 B001 1 A0 B002 0 AB B003 0 80 B004 1 90 B005 1 58 B006 1 F4 3. Number of entries in page table? 216 (one for each possible VPN) … (6 pts) Exercise 7-36 Suppose we have a virtual memory system with a 32-bit address space and 16 KB pages. 1. Show how (e.g. draw a simple picture of the address, and label it’s different parts, with numbers of bits) to divide an address into the page offset and the virtual page number. 16 KB = 214, so we need 14 bits for the page offset, leaving 18 bits for the page number: 2. How many entries are needed in the page table? 18 bits in the page number mean 218 possible page numbers, and we need an entry for each. (10 pts) Exercise 7-37 For a virtual memory system, we usually want… 1. Direct-mapped OR 4-way associative OR fully associative 2. Why? fully-associative – disk is slow, so time to decide best page to evict doesn’t hurt much 3. Write-back OR Write-through 4. Why? Write-back – otherwise, very very slow to send every write to disk!