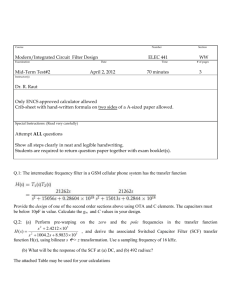

A Zero-Crossing Switched-Capacitor Filter Design

advertisement

A Zero-Crossing Switched-Capacitor Filter Design

by

Sungah Lee

Submitted to the Department of Electrical Engineering

and Computer Science

in partial fulfillment of the requirements for the degree of

Masters of Science in Electrical Engineering and Computer Science

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2008

© Massachusetts Institute of Technology 2008. All rights reserved.

A uthor ......

.............................

Department of Electrical Engineering and Computer Science

May 10, 2008

Certified by....

Hae-Seung Lee

Professor, Electrical Engineering and Computer Science

Thesis Supervisor

Accepted by ....

MASSACHUSETTS NSTrrU

OF TEGHNOLOG.Y

JUL 0 12008

LIBRARIES

/

Chairman,

C

Terry P. Orlando

Department Committee on Graduate Students

A Zero-Crossing Switched-Capacitor Filter Design

by

Sungah Lee

Submitted to the Department of Electrical Engineering and Computer Science

on May 22, 2008, in partial fulfillment of the

requirements for the degree of

Masters of Science in Electrical Engineering and Computer Science

Abstract

Design of switched capacitor circuits in scaled CMOS technologies is becoming difficult

because of low device intrinsic gain and reduced power supply voltage. To solve these

problems, comparator-based switched-capacitor (CBSC) circuits and zero-crossing based

circuits (ZCBC) were suggested as a possible solution to the op-amp based circuits. In

this thesis, we explore zero-crossing based circuits (ZCBC) in high-order differential

switched-capacitor filters to replace area inefficient op-amps-based continuous-time baseband filters. For the prototype for the zero-crossing based high-order switched capacitor

filter, a low-pass ladder filter network will be used which is less sensitive to component

variations. Several transformation steps from this low-pass passive ladder filter network

to a differential high-order switched capacitor filter will be explored. To verify this

architecture, SWITCAP will be used. And then ZCBC circuit implementation in Cadence

will be explored.

Thesis Supervisor: Hae-Seung Lee

Title: Professor, Electrical Engineering and Computer Science

Acknowledgments

First, I would like to express deepest appreciation to my advisor, Prof. Lee, for giving me

the opportunity to work on this project. I really appreciated his guidance and help since I

started my degree at MIT.

For me, this project has been a wonderful learning experience, and I could not have done

it without a lot of help from many people around me. I would like to thank Lee and

Sodini group members who have been around me by giving me help and enjoyable

environment. Especially, I would like to thank Matthew Park, who has given me all

realistic help and support since I started my degree at MIT.

Finally, I would like to thank my parents and my brother for all of their support

throughout the years and providing me with the discipline to make it this far, and I would

like to thank my grandparents in South Korea for always giving me encouragement.

Thank-you everyone,

Sungah Lee

Contents

1. Introduction

2. Ladder Filter Networks

2.1 Low-Pass Ladder Filter Network

2.2 Transformation Steps

2.3 A Differential Filter Architecture

2.4 Switched-Capacitor Integrator

2.5 A Differential Switched-Capacitor Active Ladder Filter

2.6 Determination of Capacitor Values

3. Verification of Filter Architecture through SWITCAP

3.1 Step-by-Step Verification

3.1.1 First-Order Switched-Capacitor Integrator

3.1.2 Second-Order Switched-Capacitor Low Pass Filter

3.1.3 Third-Order Switched-Capacitor Low Pass Filter

3.1.4 Fourth-Order Switched-Capacitor Low Pass Filter

3.1.5 Fifth-Order Switched-Capacitor Low Pass Filter

3.2 Adjustment of Capacitor Values

4. Circuit Implementation in Cadence

4.1 Traditional Op-Amp Based Switched-Capacitor Integrator

4.2 Comparator-Based Switched-Capacitor (CBSC) Integrator

4.3 Zero-Crossing Based Switched-Capacitor (ZCBC) Integrator

4.3.1 ZCBC Integrator Operation

4.3.2 Current Source Limitation

4.3.3 Spectre Simulated Result

4.4 Differential Zero-Crossing Based Switched-Capacitor (ZCBC) Integrator

4.4.1 Differential ZCBC Integrator Operation

4.4.2 Overshoot due to a finite delay from comparator

4.4.3 Common Mode Feedback

4.5 Differential Fifth-Order Switched-Capacitor Low-Pass Ladder Filter

5. Conclusion and Future Work

6. References

List of Figures

2-1 A low-pass passive ladder filter

2-2 A differential 5th-order active switched-capacitor filter architecture

2-3 A low-pass passive ladder filter

2-4 A s-domain signal flowgraph which shows signal flow in the architecture shown in

Fig 1.

2-5 A s-domain block diagram which multiplied all current nodes by a unit resistance

2-6 An integrator which has a transfer function

2-7 A single ended version 5th order active ladder filter

2-8 A differential version 5th order active ladder filter

2-9 An op-amp integrator

2-10 A parasitic sensitive switched-capacitor integrator

2-11 A parasitic insensitive switched-capacitor integrator

2-12 A differential 5th-order switched-capacitor filter architecture

2-13 A low-pass passive ladder filter

3-1 A first-order switched-capacitor integrator

3-2 SWITCAP Frequency Response of first-order switched-capacitor integrator

3-3 A second-order switched-capacitor low-pass filter

3-4 SWITCAP Frequency Response of second order switched-capacitor low-pass filter

3-5 A third-order switched-capacitor low-pass filter

3-6 SWITCAP Frequency Response of third order switched-capacitor low-pass filter

3-7 A fourth-order switched-capacitor low-pass filter

3-8 SWITCAP Frequency Response of a fourth-order switched-capacitor low-pass filter

3-9 A differential 5th-order switched-capacitor low-pass filter architecture

3-10 SWITCAP Frequency Response of a fifth-order switched-capacitor low-pass filter,

which is a total circuit in this thesis.

3-11 SWITCAP Frequency Response of a fifth-order switched-capacitor low-pass filter,

which is a total circuit in this thesis.

4-1 A parasitic insensitive switched-capacitor integrator

4-2 Timing diagram

4-3 A traditional op-amp based switched-capacitor integrator

4-4 Op-amp based switched-capacitor integrator transient response

4-5 A comparator-based switched-capacitor integrator

4-6 Comparator-based switched-capacitor integrator transient response

4-7 A zero-crossing based switched-capacitor(ZCBC) integrator

4-8 CBSC comparator inputs

4-9 Dynamic Zero-Crossing Detector (ZCD)

4-10 A zero-crossing based switched-capacitor (ZCBC) integrator which replaces ZCD

block in Fig 25 with a dynamic zero-crossing detector.

4-11 Timing diagram ( Integration Phase )

4-12 A zero-crossing based switched-capacitor (ZCBC) integrator which has nmos

current source

4-13 Spectre simulation result for ZCBC integrator

4-14 A differential zero-crossing based switched-capacitor(ZCBC) integrator

4-15 Differential ZCBC integrator simulation result

4-16 Timing diagram of a differential ZCBC integrator

4-17 Overshoot due to finite delay from comparator

4-18 A differential ZCBC integrator with subtracting capacitors

4-19 A differential 5th-order switched-capacitor low-pass filter architecture

4-20 A differential

5th-order

switched-capacitor low-pass filter with ZCBC integrators

4-21 SWITCAP Frequency Response of a fifth order switched-capacitor low-pass filter

List of Tables

2-1 Component values of a low-pass passive ladder filter

3-1 Adjusted Capacitor Values through step-by-step SWITCAP simulation

3-2 Practically Adjusted Capacitor Values

Chapter 1

Introduction

Design of switched capacitor circuits in scaled CMOS technologies is becoming

increasingly challenging. Because power supply voltages have been reduced greatly, the

voltage headroom available for the output swing of op-amps has been reduced. Also, to

maintain the same dynamic range, input-referred noise of the op-amp must be reduced.

kT

Therefore, based on the noise formula , -T-, compensation capacitor C, has to be bigger

C

to make noise small. To maintain the same speed of operation, Gm should be big which

means that power consumption must be increased.

Another difficulty in op-amp design for scaled CMOS technologies is due to the low

intrinsic device gain. Devices with shorter lengths have lower output resistance and

therefore have lower intrinsic device gain. To increase gain, we can cascode or cascade

stages. However cascoding brings about output swing problem and cascading can cause

stability problem.

To address the issues of lower supply voltages and low intrinsic device gain, comparator

- based switched-capacitor circuit (CBSC) technique is proposed that eliminates the need

for high gain op-amps in the signal path.[4] Op-amp forces a virtual ground condition.

This forces all the charge sampled onto Ci,, to transfer to integration capacitor Ci,.

However, in switched capacitor circuits, an accurate virtual ground condition is only

required at the sampling instant. Therefore, it should be possible to detect the virtual

ground condition at a single time point using a threshold detection comparator rather than

forcing it with an op-amp. Also detecting the virtual ground condition should be more

energy efficient than forcing it.

In this work, we explore zero-crossing based circuits (ZCBC) in high-order differential

switched-capacitor filters to replace area inefficient op-amps-based continuous-time baseband filters.

If high-order filters are implemented by cascading second-order filters, the frequency

response will be very sensitive to component variations. To implement less sensitive

high-order filters, in this project, a low-pass ladder filter network will be used as the

prototype for the zero-crossing based high-order switched capacitor filter. In Chapter 2,

several transforming steps from a passive ladder filter network to a differential high-order

switched-capacitor filter are explored. And in Chapter 3, this architecture is verified by

SWITCAP, giving the frequency response with low-pass characteristics.

Differential op-amps in a high-order switched capacitor filter are replaced by zerocrossing based circuits (ZCBC). In Chapter 4, these circuit implementation in Cadence

will be explored.

Chapter 2

Ladder Filter Networks

2.1 Low-Pass Ladder Filter Network

As I mentioned before in the introduction, if high-order filters are implemented by

cascading second-order filters, the frequency response will be very sensitive to

component variations. To implement less sensitive high-order filters, a low-pass ladder

filter network which is shown in Fig 1 will be used as the prototype for the zero-crossing

based high-order switched capacitor filter.

13

Vin

Fig 1. A low-pass passive ladder filter

Because this low-pass passive ladder filter has two inductors, three capacitors, this filter

has a 5 th -order low pass filter characteristics.

Through several transforming steps, we can achieve a differential 5th -order active

switched-capacitor filter architecture, which is shown in Fig 2.

Fig 2. A differential 5th-order active switched-capacitor filter architecture

Unlike the 5 -order passive ladder filter, this filter above has 5 differential op-amps. In

section 2.2, transformation steps from a passive ladder filter network to a differential

active switched-capacitor filter are explained step by step.

2.2 Transformation Steps

From a low-pass passive ladder filter which is shown in Fig 1,which is shown below for

convenience, we can write node equations as follows:

15

Vin

Fig 1. A low-pass passive ladder filter

Vin - V,

RI

I1 - 13 =12

1

12 sC =

SCI

V,

VI - V2

sL2

13

15

14(

1S3 )

)

sC3

14'

V2 -Vout

sL4

Vout = I5 (

2

V2 ,>

I5

1

sC 5

tR2

From these equations, we can derive the following s-domain signal flowgraph shown in

Fig 3.

Vout

Fig 3. A s-domain signal flowgraph which shows signal flow in the architecture shown in

Fig 1.

18

Because voltage-controlled voltage sources (such as op-amps) are used for integrators in

this implementation, we need to transform this diagram into the signal flowgraph, shown

in Fig 4, which multiplied all current nodes by a unit resistance R.. To maintain

relationships between voltage and current nodes, the gain factors must also be multiplied

by the normalizing resistance R..

Fig 4. A s-domain block diagram which multiplied all current nodes by a unit resistance

R, (In this figure, a unit resistance R. is equal to R )

V

1

The integrator, which is shown in Fig 5, has a transfer function - =

I

sC

V

1

Fig 5. An integrator which has a transfer function - = _--

I

sC

Therefore, s-domain block diagram shown in Fig 4 can be transformed into the following

diagram, shown in Fig 6, which has 5 integrators.

Fig 6. A single ended version 5th order active ladder filter

This is a single ended version 5th order active ladder filter architecture, which has five

single-ended op-amps.

2.3 A Differential Filter Architecture

Differential circuits can give many advantages over single-ended version circuits such as

common mode noise reduction, power supply noise reduction and distortion

improvement. Therefore, we explore a differential version of the filter architecture. We

can transform a single-ended version of the 5th order active ladder filter, which is shown

in Fig 6, into a differential version shown in Fig 7. By cross-coupling output wires, sign

changes can be implemented very easily while inverting amplifiers are required for sign

changes in a single-ended version shown in Fig 6.

Fig 7. A differential version

5 th

order active ladder filter

2.4 Switched-Capacitor Integrator

The conventional basic block of the active-ladder filter circuits is an op-amp based

integrator shown in Fig 8. The transfer function of this integrator is given by

Vot (s)

Vi (s)

1

sCA

2 R,

Fig 8 An op-amp based integrator

By replacing resistor R 1 with capacitor C 1 , and two switches, a switched-capacitor

integrator shown in Fig 9 can be implemented.

C2

Vin

C

--.

B

/,.....

Fig 9. A parasitic sensitive switched-capacitor integrator ( Here, this integrator is very

sensitive to a parasitic capacitance Cp .)

Capacitor C1 is switched at the rate of switching frequency

fsw

. In each cycle,

capacitor is charged to the input voltage Vi, , and then is discharged by the op-amp,

giving an effective resistance Re- f,

givig aneffetiv

resstaneR

ff

1

therefore the transfer function is given by

sw C,

C

Vou(z()

I z1/2

Vin (z)

2=

V1 (z)

- z1-I , which is now determined by a ratio of capacitors, high

C

accuracy and stability can be achieved in this implementation.

However, switched-capacitor integrator shown in Fig 9 is sensitive to parasitic

capacitances. Therefore, even though two extra switches are used, to get rid of the effect

of parasitic capacitances, parasitic insensitive switched-capacitor integrator which is

shown in Fig 10 is used in this work.

C2

phil

Vin-.0

phi2

C1

phi2

phil

-Vout

Fig 10. A parasitic insensitive switched-capacitor integrator

2.5 A Differential Switched-Capacitor Active Ladder Filter

Because of many advantages mentioned before, in this work, we will explore a

differential switched-capacitor filter network which is shown in Fig 2. This structure can

be derived from Fig 7 by replacing resistors with switched capacitor resistors. For

convenience, Fig 2 is shown again below.

Fig 2. A differential 5th-order switched-capacitor filter architecture

2.6 Determination of Capacitor Values

Components values of the low-pass passive ladder filter, which is used as the prototype

for this work, are determined first. For convenience, Figure 1 is shown again below.

Here, a cutoff frequency for this filter is set at 10MHz which is 0.1 of 100MHz sampling

frequency. And this filter is designed as a 5 th -order Butterworth low pass filter

configuration. Unit resistor R. , which is used to convert current nodes to voltage nodes,

has same value as both R1 and R 2 . Passive components values determined from standard

design tables are shown in Table 1.

11

Vin

Fig 1. A low-pass passive ladder filter

Passive Components

R,

Values

19

C,

L2= C 2

9.83578e-09 F

2.57513e-08 F

3.1831e-08F

2.57513e-08 F

9.83578e-09F

C3

L4 = C4

C5

R2

e

R,

i

1

Table 1. Component values of a low-pass passive ladder filter

As this low-pass passive ladder filter is transformed to a differential 5th -order active

switched-capacitor filter architecture, two inductors L2 , L4 are replaced with two

integrating capacitors C2 , C4 . In the actual switched capacitor filter, we should

determine the value of Capacitor C. which corresponds to RU, RI, R 2 . This value can be

determined as follows:

1

1=

1

(lOOe6)C U

Cu = lOnF

Chapter 3

Verification of Filter Architecture through SWITCAP

In order to verify the switched-capacitor architecture we explored through Chapter 2,

SWITCAP is used. Through Chapter 3, we will verify this architecture, which is shown

in Fig 2, step by step from 1st order to

5 th

order total circuit architecture. In this circuit, s

to z transformation errors affect the frequency response. Therefore, through these stepby-step verifications, capacitor values should be adjusted a little to obtain desirable

frequency response characteristics. In 3.2, adjusted capacitor values are presented.

3.1 Step-by-Step Verification

3.1.1 First-Order Switched-Capacitor Integrator

The following circuit diagram shows first order switched capacitor integrator, which is

first stage of the fifth-order filter.

Fig 11. A first-order switched-capacitor integrator

This integrator has been verified through SWITCAP, giving the frequency response in

Fig 12, which shows the desired integrator characteristic.

3

4

5

6

7

X10

Fig 12. SWITCAP Frequency Response of first-order switched-capacitor integrator

Because we can get an accurate integrator characteristics, we can set C,value as it was

originally set in 2.6

3.1.2 Second-Order Switched-Capacitor Low-Pass Filter

The following circuit diagram shows a second-order switched-capacitor filter, which

includes first stage and second stage of the fifth order low-pass filter.

Fig 13. A second-order switched-capacitor low-pass filter

This architecture which has two integrators is expected to give a low-pass characteristics.

Through SWITCAP, this filter has been verified as giving the following low-pass

frequency response shown in Fig 14. We can get an accurate low-pass characteristics,

therefore, we can set C2 value as it was originally set in 2.6

C

0

-5

-10

-15

-20

-25

-30f~

0

1

2

3

4

5

6

7

x 10

Fig 14. SWITCAP Frequency Response of second order switched-capacitor low-pass

filter

3.1.3 Third-Order Switched-Capacitor Low-Pass Filter

The following circuit diagram shows a third-order switched-capacitor filter, which

includes first stage, second stage and third stage of the fifth-order low-pass filter.

Fig 15. A third-order switched-capacitor low-pass filter

This architecture which has three integrators is expected to give a low-pass

characteristics. Through SWITCAP, this filter has been verified as giving the low-pass

frequency response shown in Fig 16. Through SWITCAP simulation, capacitor C3 value

has been adjusted slightly to give the desirable low-pass frequency response

characteristics.

U

-5

-10

-15

-20

-25

-30

-35

-40

-A'

0

1

2

3

4

5

6

7

x 10

Fig 16. SWITCAP Frequency Response of third order switched-capacitor low-pass filter

3.1.4 Fourth-Order Switched-Capacitor Low-Pass Filter

The following circuit diagram shows a fourth-order switched-capacitor low-pass filter,

which includes first stage, second stage, third stage and fourth stage of the fifth-order

low-pass filter.

Fig 17. A fourth-order switched-capacitor low-pass filter

This architecture which has four integrators is expected to give a low-pass characteristics.

Through SWITCAP, this filter has been verified as giving the low-pass frequency

response shown in Fig 18. Through SWITCAP simulation, capacitor C4 value has been

adjusted slightly to give more desirable low-pass frequency response characteristics.

0

-10

-20

-30

-40

-50

-60

0

1

2

3

4

5

6

7

S10

7

Fig 18. SWITCAP Frequency Response of a fourth-order switched-capacitor low-pass

filter

3.1.5 Fifth-Order Switched-Capacitor Low-Pass Filter (Total Circuit)

The following circuit diagram shows the fifth-order switched-capacitor low-pass filter,

which is a total circuit in this work, which was shown above in Fig 2. For convenience,

this figure is reproduced below.

Fig 2. A differential 5th-order switched-capacitor low-pass filter architecture

Through SWITCAP, this filter has been verified as giving the low-pass frequency

response shown in Fig 19. Through SWITCAP simulation, capacitor value C5 has been

adjusted to give the desirable low-pass frequency response characteristics.

-10

-20

-30

-40

-50

7

-60

x 10

Fig 19. SWITCAP Frequency Response of a fifth-order switched-capacitor low-pass

filter, which is a total circuit in this thesis.

3.2 Adjustment of Capacitor Values

By using SWITCAP, we explore the adjustment of capacitor values in order to give the

desirable low-pass frequency response characteristics. Table 2 shown below shows the

adjusted capacitor values.

Components

C, = 10nF

Values

C1

L2= C2

9.8e-09 F

2.6e-08 F

2.6e-08 F

C3

L4 =C

4

C5

2.2e-08 F

9.2e-08 F

Table 2. Adjusted Capacitor Values through step-by-step SWITCAP simulation

Also capacitor values shown above are not practical values. In switched-capacitor filters,

kT

only capacitor ratios matter except - noise consideration. Therefore, the capacitor sizes

C

can be changed into practically reasonable sizes very easily. Practically adjusted

capacitor values are shown in Table 3.

Components

C = 10e-13 F

Values

C1

9.8e-13 F

L2 =C

2

2.6e-12 F

C3

2.6e-12F

L4=C 4

2.2e-12F

9.2e-13 F

C5

Table 3. Practically Adjusted Capacitor Values

A differential fifth order switched capacitor filter with these practically adjusted capacitor

values shown in Table 3 has given same low-pass frequency response which is shown in

Fig 19. For convenience, this figure is shown again below. This result was easily

expected because only capacitor ratios mattered in switched-capacitor filters.

-10

-20

-30

-40

-50

-60

0

1

2

3

4

5

6

7

xl7

X 107

Fig 19. SWITCAP Frequency Response of a fifth-order switched-capacitor low-pass

filter, which is a total circuit in this thesis.

Chapter 4

Circuit Implementation in Cadence

4.1 Traditional Op-Amp Based Switched-Capacitor Integrator

Before we explore a zero-crossing based switched-capacitor integrator, first consider a

traditional op-amp based switched-capacitor integrator which is shown in Fig 10. For

convenience, Fig 10 is reproduced below.

C2

phil

Vin

Vout

Fig 10. A parasitic insensitive switched-capacitor integrator

The operation of this traditional op-amp based switched-capacitor integrator is as follows:

CLK

_

Sample

Integrate

Fig 20. Timing diagram

C02

C

VCm

"6m

Vcm

Fig 21. A traditional op-amp based switched-capacitor integrator

'I1_

voý I

I

vx J

Vcm

t

Fig 22. Op-amp based switched-capacitor integrator transient response

There are two phases one of which is the sampling phase and the other is the integration

phase which are shown in Fig 20 above. Traditional op-amp based switched-capacitor

integrator and transient response are shown in Fig 21 and Fig 22. During sampling phase,

input Vin is sampled, and capacitor C1 is charged. During the integration phase, the Op

amp forces all the charge sampled onto C1 to be transferred to C2 driving the output

voltage V0 , and once Vx equals Vcm, this integration is complete. In scaled CMOS

technologies, low intrinsic device gain and lower supply voltages make it hard to

implement high performance op-amp required in the op-amp based switched capacitor

integrator. Therefore, comparator-based switched-capacitor circuit(CBSC) technique is

proposed that eliminates the need for high gain op-amps in the signal path as explained

earlier. This comparator-based switched-capacitor circuit(CBSC) technique is explained

in section 4.2.

4.2 Comparator-Based Switched-Capacitor (CBSC) Integrator

As mentioned in 4.1, comparator-based switched-capacitor(CBSC) circuits have been

proposed to overcome the shortcomings of Op amp based circuits. Comparator-based

switched-capacitor (CBSC) integrator and transient response are shown in Fig 23 and Fig

24.

C2

C

Vocm

Vcm

Vcm

Vc m

Fig 23. A comparator-based switched-capacitor integrator

"h._

vo

It

I

Vcm

e'ý

t

Fig 24. Comparator-based switched-capacitor integrator transient response

Op-amp based circuits and CBSC based circuits use the same input sampling circuit. The

difference is in the method of achieving the virtual ground condition during the charge

transfer phase. In switched capacitor circuits, an accurate virtual ground condition is only

required at the sampling instant. Therefore, in a comparator-based switched-capacitor

integrator, op-amp is replaced with a comparator and a current source. During the

sampling phase, as in the op-amp based switched-capacitor integrator, the input voltage

Vin is sampled, and capacitor C, is charged. However, during the integration phase, the

current source charges the capacitors, resulting in a voltage ramp on V0, therefore,

causing a voltage ramp on V,. When Vx equals Vcm, a comparator detects this condition,

and then disables the current source thereby completing integration.

4.3 Zero-Crossing Based Switched-Capacitor (ZCBC)

Integrator

4.3.1 ZCBC Integrator Operation

C

Vcm

VCm

Fig 25. A zero-crossing based switched-capacitor(ZCBC) integrator

The inputs to the comparator of a comparator-based switched-capacitor integrator are

voltage ramps which have constant slopes as shown in Fig 26. Therefore, a general

purpose comparator in Fig 23 can be replaced with dynamic zero-crossing detector,

which is shown in Fig 27 [5]. By using dynamic zero-crossing detector, the

implementation can be more power and area efficient than using a general purpose

comparator.

VxFig

26. CBSC comparator inputs (V node)

Fig 26. CBSC comparator inputs (V,, node)

Vdd

phil _bar

VXH

Vp

Fig 27. Dynamic Zero-Crossing Detector (ZCD)

Fig 28 shows the implementation of zero-crossing based switched-capacitor (ZCBC)

integrator which replaces the comparator with a dynamic zero-crossing detector which

consists of only two devices.

Control

phi 1

Fig 28. A zero-crossing based switched-capacitor (ZCBC) integrator which replaces ZCD

block in Fig 25 with a dynamic zero-crossing detector.

p12

pr~ese

Fig 29. Timing diagram ( Integration Phase )

The ZCBC integrator operates in a similar fashion to a CBSC integrator which was

explained above. During the sampling phase, the input Vin is sampled, and VP preset to

V, . Then, as shown in Fig 29, phi2, preset are set to high to start integration. During

preset phase, the output is initially preset to ground to ensure that V, is always below

than threshold voltage of the zero-crossing detector. The current source is then enabled.

When Vx gets high enough to cross the threshold of the zero-crossing detector transistor,

VP is pulled low sampling the output voltage at that instant.

4.3.2 Current Source Limitation

Finite output resistance of the current source can give rise to output voltage error similar

to finite gain in op amp based circuits. Therefore, larger output resistance is desirable. In

Fig 28, a current source is implemented by using a PMOS device which has low output

resistance ro compared to NMOS devices. Therefore, circuit implementation shown in

Fig 28 can be implemented like the diagram which is shown in Fig 30 in which a current

source is implemented by only NMOS devices. Also here, during the preset phase, output

is preset to Vd, which is opposite to the previous case in Fig 28.

Vdd

preset

phi

phi 2grol

Fig 30. A zero-crossing based switched-capacitor (ZCBC) integrator which has nmos

current source

4.3.3 Spectre Simulated Result ( ZCBC Integrator)

The simulated result for zero-crossing based circuits (ZCBC) integrator, which is shown

in Fig 28, is shown in figure 31.

1) input: sine, output: cosine

Transient Response

5901m

--

510m

:

VT("/Vin")

1

500m

1

490m

480m

1

,

1

,

I

,

_~

,

,

.

,

,

,

.

1

,

,

1

r\

,

,

,

s

,

'

a. VT("/,ot ")

1.10

Boom I

500m

200m

-

1•m

,

4 .Ou

5.0u

6.0u

7.0u

time ( s )

2) input : pulse, output: triangular

8.0u

9.0u

Transient Response

550m

\ff(,

500m

{

ij.

.

.

.

L450m

t,

"""

VT'vorf'/~ut )

1,10

700m

300m

-lom

'"""

i

4.0u

5.0u

time ( s )

6.0u

7.0u

Figure 31 Spectre simulation result for ZCBC integrator

With a sine wave as an input, a cosine wave is produced at the output, and also with a

pulse train as an input, a triangular waveform is produced at the output. This

demonstrates zero-crossing integrator is working properly.

4.4 Differential Zero-Crossing Based Switched-Capacitor

(ZCBC) Integrator

As mentioned before, differential circuits have many advantages including common

mode noise reduction, power supply noise reduction and distortion improvement. In most

applications, differential circuits are desirable, therefore, we investigate a differential

version zero-crossing based switched-capacitor(ZCBC) integrator. Differential op-amps

in a high-order switched-capacitor filter are replaced by this differential zero-crossing

detectors. Fig 32 shows a differential zero-crossing based switched-capacitor(ZCBC)

integrator, which is the key component in a high-order switched- capacitor filter.

phi I

,iIJ'

phi2!

control

Fig 32. A differential zero-crossing based switched-capacitor(ZCBC) integrator

f

n~I

---- F

04t•ff"t

._;~.......

-7

A-

_____

·-

I

.....

. ........

______

.twit.

40ON

--- 4-

-F

-

~~'~~--1

2M6

-

--

~-a

...

.......

9

I

.... ...

-.......

,=

AA.

'~

-l

-sea-

~1

C .......

i

Il

-t

tI

-soon-

-14

~

finn

r*r*

L

i

43.8m

t;-w ( *

)

91.r0

Fig 33. Differential ZCBC integrator simulation result

4.4.1 Differential ZCBC Integrator Operation

The Timing diagram of a differential ZCBC integrator is shown in Fig. 34

san- Ilr phase

tarEier phase

I

II

I

I I

I

I

I

I

II

PH

pH2

Preses

Van I

I

Va~ I

IaI

I

-I

I _J. I

""

VM÷

I

I

I

I

I

Fig 34. Timing diagram of a differential ZCBC integrator

During the sampling phase, differential inputs, inp andinm, are sampled. Then as shown

in Fig 34, phi2 and preset are set to high to start the integration phase. During preset

phase, differential outputs, outp and outm, are preset to ground and Vdd. Both current

sources are then enabled. As shown in Fig 34, When Vx÷ and Vx_ intersect, is positive,

the zero-crossing detector trips, and the output voltage is sampled as desired.

4.4.2 Overshoot due to a finite delay from zero crossing detector

As we can see in Fig 35, there is an overshoot on Vx_, Vx_ resulting in an overshoot on

outp, outm due to a finite delay from the zero crossing detector.

Vdc

Vx-

vnIIII

VaIi

o

IIL_

veI

I

I

VX+' I

,I

I

I

td'

Fig 35. Overshoot due to finite delay from comparator

One way to reduce this overshoot is to subtract charge from the integrating capacitors

every cycle the corresponds to the overshoot error. Fig 36 shows the circuit diagram with

the subtracting capacitors. Here, Ve should be made smaller than Vm to subtract charge

from the integrating capacitors during integrating phase (phi2). The operation of this is

as follows. During the sampling phase, Vref is sampled on Cbract .During the integration

phase, all the charge sampled onto Csubtract , which is negative because Vef is smaller than

Vý,, is transferred to integrating capacitors subtracting charge.

Vmf

Vref

Fig 36. A differential ZCBC integrator with subtracting capacitors

4.4.3 Common Mode Feedback

Fully differential op-amp based circuits require a common-mode feedback(CMFB)

circuit. The common-mode feedback(CMFB) circuit makes common-mode voltage Vcm

V +VS,

stay roughly at Vdd+Vs . It is difficult to implement common-mode feedback(CMFB)

2

circuits, which has been one of the drawbacks of a fully differential op-amp based circuit

implementation. However, in fully differential zero-crossing based circuits(ZCBC),

common-mode voltage is determined by the strengths of up-current and down current

sources. Although mismatch between up-current and down-current sources can cause a

small error, these can be removed per each cycle. Therefore, when it comes to a commonmode feedback(CMFB) circuit, a fully differential ZCBC circuits have another advantage

over op-amp based circuits because common-mode feedback circuit for op-amp based

circuits is not necessary.

4.5 Differential Fifth-Order Switched-Capacitor Low-Pass

Ladder Filter

Differential op-amps in a verified differential 5th-order switched-capacitor low-pass filter

architecture shown in Fig 2, which is shown again below, are replaced by differential

zero-crossing based circuits(ZCBC) which is explored in section 4.4.

Fig 2. A differential 5th-order switched-capacitor low-pass filter architecture

A differential 5th-order switched-capacitor low-pass filter architecture is shown in Fig

37. Circles indicate that those parts are to be replaced by differential zero-crossing based

integrators.

Fig 37. A Differential 5h-order switched-capacitor low-pass filter, in which circles are

replaced with differential ZCBC integrators

SPICE transient simulation has not been performed on this circuit because it takes

extremely long simulation time to show frequency response. Instead, because we have

verified the architecture through SWITCAP giving the desired low-pass frequency

response which is shown below, we expect to get similar frequency response from the

zero-crossing based filter.

U

-10

-20

-30

-40

-50

--•N--v

0

1

2

3

4

5

6

7

X107

Fig 18. SWITCAP Frequency Response of a fifth order switched-capacitor low-pass filter

Chapter 5

Conclusion and Future work

In this thesis, we explored the design of 5th -order ZCBC switched-capacitor ladder filter.

To design this, a low-pass passive ladder filter which has two inductors and three

capacitors was used as a prototype and then through several transformation procedures

we achieved a differential 5th -order switched-capacitor ladder filter architecture. This

architecture has been verified by SWITCAP. Differential amplifiers in the architecture

are then replaced by zero-crossing based circuits (ZCBC). Therefore, we implement a 5t h

order ZCBC switched-capacitor filter which is much more area efficient than op-ampsbased continuous-time base-band filters and also by using ZCBC technique. We can

avoid implementing conventional op-amp-based integrators which are becoming very

difficult to implement in scaled CMOS technologies.

In this zero-crossing based circuits (ZCBC) switched-capacitor filter design, there are

three things which need further research. First, the finite output resistance of the current

source results in residue errors on output voltage. Therefore, further research in how to

improve current sources is needed. Second, in differential ZCBC integrator, the mismatch

between up-current and down-current sources cause a common-mode error. Further

research is needed in how to correct this current mismatch or how to control this current

mismatch. Third, there is an overshoot due to a finite delay from a comparator. In 4.4.2,

one way of reducing this overshoot from a finite delay was presented. However this

method also requires generating a correct reference voltage to subtract the right amount

of charge from integrating capacitor. Therefore, further research in how to produce this

reference voltage in simple manner is needed.

Chapter 6

References

[1] G.M. Jacobs, D.J. Allstot, R.W. Brodersen, P.R. Gray, "Design Techniques for MOS

Switched Capacitor Ladder Filters," IEEE Transactions on Circuits And Systems,

VOL. CAS-25, NO.12, Dec. 1978.

[2] T.S. Durrani, R. Chapman, "Optimal All-Pole Filter Design Based on Discrete Prolate

Spheroidal Sequences," IEEE Transactions on Acoustics, Speech, and Signal

Processing, VOL. ASSP-32, NO.4, August 1984.

[3] S. Azuma, S. Kawama, K.Iizuka, M. Miyamoto, D, Senderowicz, "Embedded AntiAlliasing in Switched-Capacitor Ladder Filters With Variable Gain and Offset

Compensation," IEEE Solid-State Circuits, VOL 37,No.3, March 2002.

[4] T. Sepke, J.K. Fiorenza, C.G. Sodini, P. Holloway, and H.-S. Lee, "Comparatorbased switched-capacitor circuits for scaled CMOS technologies," IEEE Int'l SolidState Circuits Conf. Dig. Of Tech. Papers, San Francisco, CA, Feb. 2006, pp. 220221.

[5] L. Brooks and H.-S. Lee, "A zero-crossing-based 8b 200MS/s pipelined ADC," IEEE

Int'l Solid-State Circuits Conf. Dig. Of Tech. Papers, San Francisco, CA, Feb. 2007,

pp. 15-17.